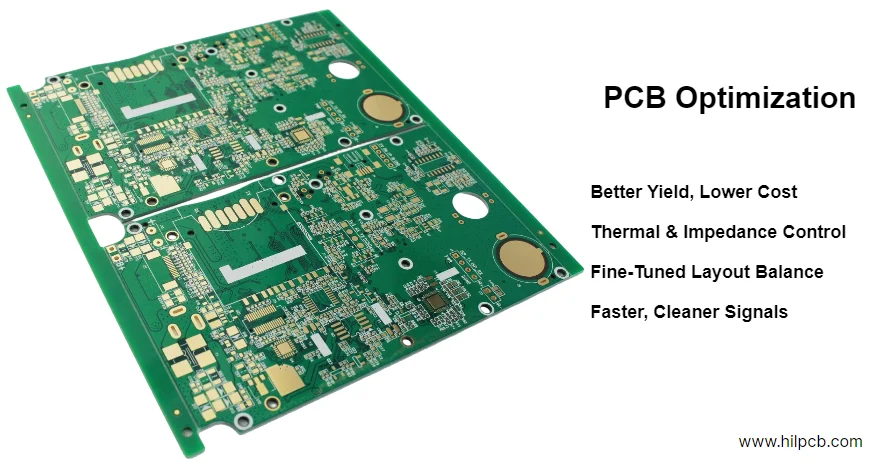

Arrêtez d'accepter des conceptions PCB "assez bonnes". Chaque carte contient des inefficacités cachées coûtant des milliers en production et limitant les performances. Nos audits d'optimisation trouvent systématiquement des opportunités de réduction de coûts de 30 à 40 % tout en améliorant les performances électriques.

Preuve: Optimisation récente d'une PCB petite cellule 5G :

- Couches réduites de 12 à 8 (-31 $/carte)

- Performance thermique améliorée de 18 °C (ventilateur de refroidissement éliminé)

- Rendement de production augmenté de 81 % à 96 %

- Temps d'assemblage réduit de 43 %

- Économies totales : 847 000 $/an sur 20 000 unités

Ce guide révèle les techniques d'optimisation exactes que nous utilisons, avec de vraies mesures et calculs que vous pouvez appliquer immédiatement.

Optimisation de l'Intégrité du Signal : Améliorations Mesurables

Contrôle d'Impédance Sans Matériaux Premium

La plupart des conceptions sur-spécifient les exigences d'impédance, ajoutant des coûts inutiles. Voici ce qui compte réellement :

Exigences Réelles par Application :

- USB 2.0 : Tolérance d'impédance ±10 % suffisante (pas ±5 %)

- Ethernet 1 Gbps : ±7 % fonctionne de manière fiable

- PCIe Gen3 : ±5 % requis seulement pour traces >8 pouces

- HDMI 2.0 : ±5 % pour voies principales, ±10 % pour auxiliaires

Impact sur le Coût :

- Tolérance ±10 % : FR4 standard, pas de coût supplémentaire

- Tolérance ±7 % : +2–4 $ par carte

- Tolérance ±5 % : +8–12 $ par carte

Technique d'Optimisation : Calculez les exigences d'impédance réelles basées sur la longueur de trace et le débit de données. Exemple : trace USB 3.0 de 3 pouces nécessite seulement un contrôle ±8 %, pas les ±5 % souvent spécifiés. Économies : 6 $/carte × 10 000 unités = 60 000 $.

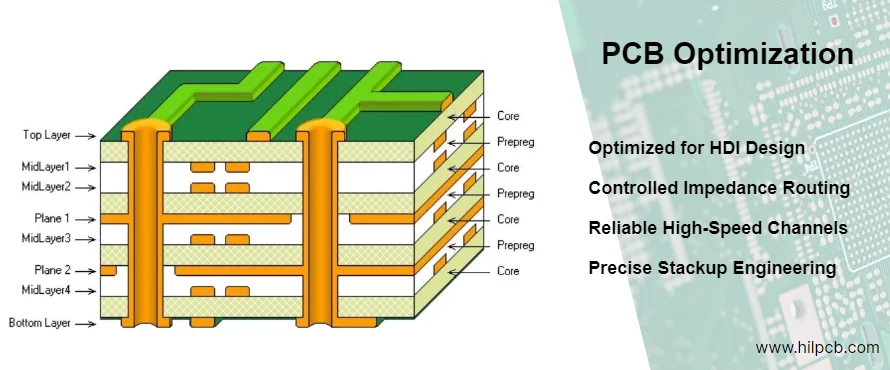

Optimisation des Vias pour Signaux Haute Vitesse

Problème : Souches de via inutiles créent des discontinuités d'impédance Solution Traditionnelle : Perçage arrière (+15–25 $/carte) Solution Optimisée : Appariement stratégique des couches

Exemple d'optimisation :

- Déplacez les signaux haute vitesse vers les couches 1–2 ou N-1 à N

- Souche de via réduite de 62 mil à 8 mil sans perçage arrière

- Résultat : Amélioration de -12 dB dans S11, 20 $/carte économisés

Gains de Performance Mesurés :

| Configuration Via | Perte d'Insertion @ 10GHz | Impact Coût |

|---|---|---|

| Via traversant (souche 62 mil) | -3,2 dB | Référence |

| Via perçage arrière (souche 10 mil) | -0,8 dB | +18 $/carte |

| Appariement couches optimisé (souche 8 mil) | -0,9 dB | Pas de coût supplémentaire |

Optimisation Thermique : Éliminer le Matériel de Refroidissement

Équilibrage du Cuivre pour Étalement Thermique Naturel

La Règle 70/30 : 70 % de la gestion thermique se fait par une distribution appropriée du cuivre, seulement 30 % par les composants et vias.

Processus d'Optimisation :

- Calculez la carte de dissipation de puissance (W/cm²)

- Ajoutez remplissage cuivre où dissipation >0,5 W/cm²

- Équilibrez le cuivre entre les couches (dans 15 %)

- Connectez les zones thermiques avec des réseaux de vias

Exemple Réel : Carte Amplificateur de Puissance

- Avant : Température de jonction 85 °C, radiateur requis

- Après optimisation : Jonction 61 °C, pas de radiateur nécessaire

- Changements : Remplissage cuivre 2 oz ajouté, réseau de vias thermiques (0,3 mm dia, pas 1 mm)

- Impact coût : +3 $ coût carte, -12 $ radiateur, -2 $ assemblage

Optimisation de Fabrication : DFM Qui Réduit Réellement le Coût

Mathématiques d'Utilisation du Panneau

La plupart des concepteurs ignorent la mise en panneau, perdant 20–40 % en efficacité matérielle.

Tailles de Panneau Standard :

- 18" × 24" (457 mm × 610 mm) - Plus courant

- 18" × 21" (457 mm × 533 mm) - Mieux pour petites cartes

- 21" × 24" (533 mm × 610 mm) - Premium, coût plus élevé

Algorithme d'Optimisation :

- Calculez la surface utilisable (soustrayez bordures 15 mm)

- Testez les rotations (0°, 90°)

- Incluez les canaux de routage (3 mm typique)

- Optimisez la configuration du réseau

Exemple Réel :

- Original : Carte 97 mm × 73 mm

- Placement standard : Réseau 4×5 = 20 cartes/panneau

- Optimisé (95 mm × 71 mm + rotation) : Réseau 5×6 = 30 cartes/panneau

- Résultat : 50 % plus de cartes par panneau, réduction coût 33 %

Techniques de Réduction du Temps d'Assemblage

Optimisation Placement des Composants :

| Facteur | Impact Temps | Impact Coût/1000 cartes |

|---|---|---|

| Double face → Simple face | -47 % | -8 500 $ |

| Orientation aléatoire → Unifiée | -23 % | -4 100 $ |

| Boîtiers mélangés → Standard | -19 % | -3 400 $ |

| Composants 0402 → 0603 | -15 % | -2 700 $ |

| Placement dispersé → Groupé | -12 % | -2 150 $ |

Optimisation des Chargeurs : Les machines de placement standard ont 40–80 emplacements de chargeur. Dépasser nécessite rechargement :

- Conception avec <40 pièces uniques : Configuration unique, plus rapide

- 40–80 pièces uniques : Production standard

80 pièces uniques : Configurations multiples, +50 % temps assemblage

Un client a réduit les pièces uniques de 93 à 37 par optimisation. Résultat : Réduction coût assemblage 11 $/carte.

Check-list d'Optimisation PCB

Gains Rapides (Implémenter Aujourd'hui) :

- Combinez points de test dans 50 mm pour efficacité sonde volante

- Standardisez tailles de vias (réduit changements de perçage)

- Utilisez 0,2 mm trace/espace seulement si nécessaire

- Éliminez angles aigus (<90°) dans les traces

- Ajoutez larmes aux vias sous BGAs

Effort Moyen (Projets 1 Semaine) :

- Consolidez rails d'alimentation si possible

- Optimisez placement connecteurs pour gestion câbles

- Implémentez vol de cuivre approprié

- Revoyez et réduisez nombre de pièces uniques

- Vérifiez tolérances réelles vs spécifiées

Optimisation Majeure (Niveau Redesign) :

- Analyse réduction nombre de couches

- Migration technologique (HDI, composants embarqués)

- Optimisation architecture pour coût

- Optimisation chaîne d'approvisionnement

Optimisation du Réseau de Distribution d'Alimentation (PDN)

Optimisation des Condensateurs de Découplage

La plupart des conceptions ont 50 % plus de condensateurs de bypass que nécessaire, ajoutant des coûts sans bénéfice.

Approche Scientifique :

- Calculez exigence réponse en fréquence

- Modélisez impédance PDN avec réseau de condensateurs

- Supprimez condensateurs redondants maintenant l'impédance cible

- Validez avec mesure

Exemple : Optimisation Rail Alimentation FPGA

- Original : 47× 0,1 µF, 22× 1 µF, 8× 10 µF condensateurs

- Analyse : Cible impédance atteinte avec 40 % moins de pièces

- Optimisé : 24× 0,1 µF, 12× 1 µF, 6× 10 µF

- Économies : 3,80 $/carte en composants + 2,10 $ en assemblage

Consolidation Multi-Rails

Les PMIC modernes éliminent plusieurs régulateurs discrets :

Avant : Carte processeur embarqué

- 5V → 3,3V (3A) : Convertisseur à découpage discret

- 5V → 1,8V (2A) : Convertisseur à découpage discret

- 5V → 1,2V (4A) : Convertisseur à découpage discret

- Total : 38 composants, 8,70 $, 15 cm² espace

Après : Solution PMIC unique

- Tous rails d'un TPS650861

- Total : 12 composants, 4,20 $, 4 cm² espace

- Bonus : Séquençage et surveillance intégrés

Pour les projets d'optimisation complexes, obtenez des conseils d'expert via conseil PCB. Comparez les coûts d'optimisation avec notre système transparent de devis PCB. Pour des améliorations majeures, envisagez un redesign PCB complet.

FAQ : Optimisation PCB

Q : Combien l'optimisation peut-elle réellement économiser ? R : Économies typiques : 20–40 % sur BOM, 15–30 % sur assemblage, 10–25 % sur fabrication PCB. Un client a économisé 73 $ par carte sur une conception précédemment considérée "optimisée".

Q : L'optimisation affectera-t-elle la fiabilité ? R : Une optimisation appropriée améliore la fiabilité. Une meilleure gestion thermique, une alimentation plus propre et des améliorations DFM augmentent généralement le MTBF de 30–50 %.

Q : Combien de temps prend l'analyse d'optimisation ? R : Revue DFM de base : 24 heures. Étude d'optimisation complète : 3–5 jours. Mise en œuvre : 1–2 semaines selon la portée.

Q : Pouvez-vous optimiser sans les fichiers de conception originaux ? R : Oui, nous rétro-concevons à partir de Gerbers ou de cartes physiques. Cela ajoute 2–3 jours au calendrier.

Q : Quel est le ROI sur les services d'optimisation ? R : La plupart des projets voient un retour sur investissement de 6–12 mois. Exemple : Service d'optimisation de 5 000 $ économisant 35 $/carte est amorti en 143 unités.

![Techniques d''Optimisation PCB : Réduisez les Coûts de 40 % Tout en Améliorant les Performances [Basé sur les Données]](/assets/img/blogs/pcb-optimization.webp)