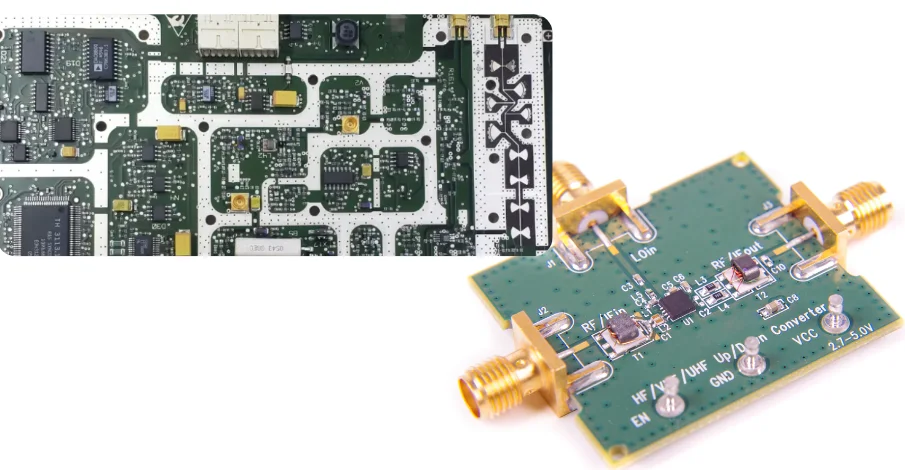

L'integrità del segnale determina il successo o il fallimento nei progetti PCB ad alta frequenza. Poiché le velocità di trasmissione dei dati superano i 25 Gbps e le frequenze superano i 40 GHz, il mantenimento di segnali puliti richiede approcci sistematici alla progettazione, all'analisi e alla convalida. Questa guida fornisce soluzioni pratiche per ottenere un'integrità del segnale superiore nelle applicazioni più impegnative.

Che cos'è l'integrità del segnale e perché è fondamentale nella progettazione di PCB HF

L'integrità del segnale si riferisce alla qualità dei segnali elettrici mentre viaggiano attraverso un PCB ed è particolarmente critica nella progettazione di PCB HF (PCB ad alta frequenza). Con l'aumento delle frequenze del segnale, mantenere l'integrità del segnale significa preservare parametri importanti come l'ampiezza, la temporizzazione e la forma della forma d'onda. La distorsione di questi parametri può portare a un significativo degrado del segnale, soprattutto alle alte frequenze, dove anche problemi minori possono causare errori nei dati.

Le metriche chiave per valutare l'integrità del segnale nei PCB HF includono l'altezza dell'occhio (l'apertura verticale per le decisioni sui bit, in genere >100 mV), l'ampiezza dell'occhio (il margine di temporizzazione, in genere >0,6 UI) e il jitter (variazioni di temporizzazione, in genere <0,3 UI per la maggior parte dei sistemi). Anche il tasso di errore di bit (BER) è una misura importante, con un obiettivo di <10^-12, garantendo che il sistema possa trasmettere dati in modo affidabile e senza errori.

Con l'aumentare della frequenza, aumentano anche le sfide nel mantenere l'integrità del segnale. Per i PCB HF che operano a 1-5 GHz, il controllo dell'impedenza e la minimizzazione della diafonia sono fondamentali, con un obiettivo di perdita di ritorno di >15dB. A 5-20 GHz, l'attenzione si sposta sulla riduzione al minimo delle perdite e sull'ottimizzazione delle transizioni via, con una perdita di inserzione inferiore a 3 dB. A 20-40 GHz, la rugosità superficiale diventa critica, richiedendo una tangente di perdita (Df) inferiore a 0,002. Per le frequenze superiori a 40 GHz, ogni aspetto del design del PCB deve essere attentamente ottimizzato per garantire che il segnale rimanga pulito e non distorto.

Come analizzare e misurare l'integrità del segnale

Fondamenti di analisi del diagramma a occhio

I diagrammi a occhio forniscono una visualizzazione completa della qualità del segnale sovrapponendo più transizioni di bit:

Parametri critici dell'occhio:

- Apertura occhi: Determina il margine di rumore

- Percentuale di attraversamento: indica la distorsione del ciclo di lavoro

- Tempo di salita/discesa: mostra i limiti della larghezza di banda

- Componenti di jitter: casuale vs deterministico

Interpretazione dei diagrammi a occhio:

- Occhio spalancato: buona integrità del segnale

- Chiusura verticale: rumore di ampiezza, diafonia

- Chiusura orizzontale: jitter eccessivo

- Occhi multipli (PAM4): richiede 3 aperture libere

Requisiti di misurazione:

- Larghezza di banda dell'oscilloscopio: >2,5× frequenza del segnale

- Dimensione del campione: >1 milioni di forme d'onda

- Sondaggio corretto: riduce al minimo gli effetti del carico

Analisi nel dominio del tempo e della frequenza

Misure TDR/TDT:

- Rivela le discontinuità di impedenza

- Individua le aree problematiche

- Caratterizza tramite transizioni

- Convalida i modelli di simulazione

Analisi dei parametri S:

- S11/S22: Perdita di ritorno (<-10dB minimo)

- S21: Perdita di inserzione (dipendente dall'applicazione)

- S31/41: Isolamento della diafonia (>30dB)

- Modalità mista: caratterizzazione differenziale

Problemi comuni di integrità del segnale e soluzioni

Gestione della diafonia in layout densi

La diafonia peggiora con la diminuzione degli edge rate e l'aumento della densità di routing. Si verifica attraverso l'accoppiamento capacitivo e induttivo, portando a interferenze near-end (NEXT) e far-end (FEXT).

Meccanismi di diafonia:

- Capacitivo: accoppiamento del campo elettrico tra le tracce

- Induttivo: accoppiamento del campo magnetico tra le tracce

- Near-end (NEXT): Interferenza alla fonte

- Far-end (FEXT): Interferenza sul ricevitore

Strategie di mitigazione:

- Spaziatura 3W: Facile da implementare con guadagno di isolamento di 10-15 dB e basso costo.

- Guard Traces: offre un isolamento di 15-20 dB, con complessità e costi di implementazione moderati.

- Via recinzione: Raggiunge un isolamento di 20-30 dB, ma è più complesso e ha un costo medio.

- Strati separati: fornisce un isolamento di >40 dB, ma richiede un'attenta progettazione e comporta costi elevati.

Migliori pratiche:

- Traccia del percorso perpendicolare su strati adiacenti.

- Riduci al minimo le tracce parallele per ridurre l'accoppiamento.

- Utilizzare la segnalazione differenziale ove possibile per una migliore immunità al rumore.

- Implementa una corretta progettazione dello stackup per ridurre al minimo la diafonia.

Controllo delle riflessioni e dell'impedenza

Le riflessioni dovute alle discontinuità di impedenza portano alla degradazione del segnale e agli errori dei dati. Le fonti comuni di queste discontinuità includono le transizioni di via, le interfacce dei connettori, le modifiche della larghezza della traccia e le transizioni del piano di riferimento.

Soluzioni:

- Ottimizza le dimensioni dell'antipad per garantire transizioni fluide.

- Progettare meccanismi di lancio adeguati alle interfacce in modo che corrispondano all'impedenza.

- Utilizzare rastremazioni graduali per le tracce per evitare bruschi cambiamenti di impedenza.

- Mantieni piani di riferimento continui su tutti i livelli per ridurre le riflessioni del segnale.

Tecniche di riduzione del jitter

Un jitter eccessivo limita la larghezza degli occhi e può causare errori di bit, con conseguente scarsa qualità del segnale. Il jitter è tipicamente costituito da jitter casuale (RJ) e jitter deterministico (DJ), dove il jitter totale (TJ) è la somma di entrambi i componenti.

Componenti di jitter:

- Jitter casuale (RJ): tipicamente 1-2 ps RMS.

- Jitter deterministico (DJ): Di solito 5-20 ps di picco.

- Jitter totale (TJ): TJ = DJ + 14×RJ (al tasso di errore di bit 10^-12).

Strategie di riduzione:

- Utilizzare sorgenti di clock a basso jitter per ridurre al minimo gli errori di temporizzazione.

- Riduci al minimo le discrepanze della lunghezza della traccia per evitare ritardi nel segnale.

- Controlla il rumore dell'alimentatore per ridurre gli errori indotti dal jitter.

- Implementare una terminazione corretta per mantenere l'integrità del segnale.

- Aggiungere l'equalizzazione quando necessario per compensare il degrado del segnale.

Best practice per l'integrità del segnale ad alta frequenza

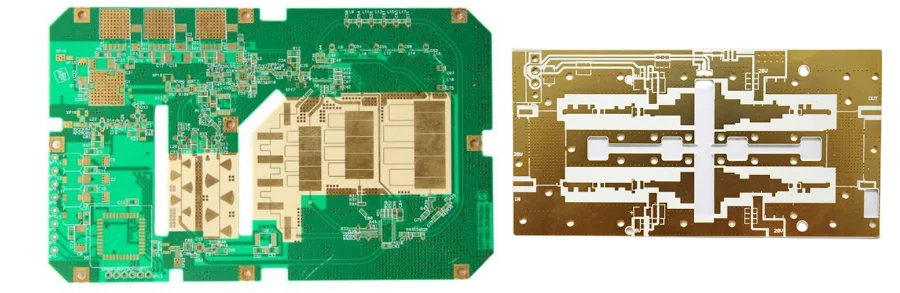

Progettazione ottimizzata dello stack-up PCB

Uno stack-up progettato correttamente costituisce la base per l'integrità del segnale:

Principi chiave:

- Piani di terra/alimentazione adiacenti per ogni livello di segnale

- La costruzione simmetrica previene la deformazione

- Dielettrici sottili per un accoppiamento stretto

- Impedenza costante tra gli strati

Esempio di stack-up ad alta velocità a 8 strati:

- L1/L8: Segnali a microstriscia (impedenza controllata)

- L2/L7: Piani di massa (continui)

- L3/L6: Coppie ad alta velocità Stripline

- L4/L5: Nucleo di alimentazione/terra

Implementazione della coppia differenziale

La segnalazione differenziale fornisce un'immunità al rumore superiore:

Requisiti di progettazione:

- Lunghezza corrispondente: <0,025 mm all'interno della coppia

- Spaziatura costante: Mantenere l'accoppiamento

- Routing simmetrico: parassiti uguali

- Nessuna divisione tra le coppie

Applicazioni comuni:

- PCIe: 85Ω differenziale

- Ethernet: differenziale 100Ω

- USB 3.0: differenziale 90Ω

- HDMI: differenziale 100Ω

Tramite strategie di ottimizzazione

I vias influiscono in modo significativo sull'integrità del segnale sopra i 5 GHz:

Tecniche di ottimizzazione:

- Riduci al minimo le transizioni: instradare su un singolo strato quando possibile

- Backdrilling: rimuovere i tronchetti >0,5 mm a >10 GHz

- HDI Microvias: Utilizzabile per applicazioni a >20 GHz

- Vie di terra: Posizionare entro 1 mm dalle vie del segnale

Il ruolo dell'integrità dell'alimentazione nella qualità del segnale

Il rumore dell'alimentatore influisce direttamente sull'integrità del segnale attraverso molteplici meccanismi:

Requisiti di progettazione PDN

Calcolo dell'impedenza target: Ztarget = Vripple / (0,5 × Itransiente)

Per alimentazione a 1 V con ripple da 50 mV e transitorio da 10 A: Ztarget = 0,05 / 5 = 10mΩ

Raggiungimento dell'impedenza target:

- Condensatori di massa: 100-1000μF

- Disaccoppiamento ceramico: 0,1-10μF

- Alta frequenza: 10-100nF

- Capacità incorporata: <1nF

Strategia di disaccoppiamento

Linee guida per il posizionamento:

- Entro 2 mm dai pin di alimentazione per >1 GHz

- Vie multiple per una bassa induttanza

- Collegamento diretto al piano di massa

- Distribuito su tutta la scheda

Strumenti di simulazione e verifica

Analisi pre-layout

Simulazioni essenziali:

- Pianificazione del budget del canale

- Esplorazione topologica

- Compromessi sui materiali

- Ottimizzazione della terminazione

Requisiti dello strumento:

- Risolutori di campo 2D per impedenza rapida

- EM 3D per strutture complesse

- Simulazione di circuiti per l'analisi del sistema

- Analisi statistica per la resa

Verifica post-layout

Flusso di convalida:

- Estrarre i parassiti del layout

- Includi strutture 3D

- Esegui l'analisi degli angoli

- Genera diagrammi a occhio

- Verifica le specifiche

Precisione della correlazione:

- Impedenza: ±5%

- Perdita: ±10%

- Area interattiva: ±15%

- Richiede modelli accurati

Perché scegliere HILPCB per l'integrità del segnale

HILPCB fornisce soluzioni complete per l'integrità del segnale per applicazioni ad alta frequenza:

- Servizi di progettazione: Analisi SI pre-layout

- Simulazione: strumenti HFSS, CST, Sigrity

- Materiali: inventario completo di RF/microonde

- Test: TDR, VNA a 40 GHz

- Esperienza: applicazioni 5G, radar, HPC

- Supporto: Consulenza tecnica esperta

Domande frequenti

Q1: Quali sono le cause dei problemi di integrità del segnale alle alte frequenze? R: Le cause primarie includono discontinuità di impedenza, diafonia eccessiva, perdite dipendenti dalla frequenza e rumore dell'alimentatore. I problemi peggiorano con edge rate più elevati e frequenze più elevate.

Q2: Come faccio a sapere se ho problemi di integrità del segnale? R: Cerca diagrammi ad occhio chiuso, BER elevato (>10^-12), jitter eccessivo (interfaccia utente >0,3), errori intermittenti o test di conformità non superati.

Q3: Quando dovrei preoccuparmi dell'integrità del segnale? R: Considerare SI quando: le frequenze superano i 100 MHz, i tempi di salita scendono al di sotto di 1ns o le lunghezze delle tracce superano λ/10 alla frequenza operativa.

Q4: Qual è la differenza tra NEXT e FEXT? R: NEXT viene visualizzato all'estremità sorgente ed è in genere peggiore. FEXT appare all'estremità più lontana e si accumula con la lunghezza accoppiata. Stripline riduce al minimo la FEXT.

Q5: Quanto aggiunge l'analisi SI al tempo di progettazione? R: Un'adeguata analisi SI aggiunge il 20-30% alla progettazione iniziale, ma consente di risparmiare il 40-50% complessivo riducendo le iterazioni del prototipo.

Q6: Qual è la cosa più importante per l'integrità del segnale? R: L'impedenza controllata è fondamentale, seguita da un corretto design dello stackup, discontinuità ridotte al minimo e un'adeguata erogazione di potenza.