Smettila di accettare progetti PCB "abbastanza buoni". Ogni scheda contiene inefficienze nascoste che costano migliaia in produzione e limitano le prestazioni. Le nostre audit di ottimizzazione trovano costantemente opportunità di riduzione dei costi del 30-40% migliorando contemporaneamente le prestazioni elettriche.

Prova: Recente ottimizzazione di una PCB small cell 5G:

- Strati ridotti da 12 a 8 (-31 $/scheda)

- Prestazioni termiche migliorate di 18 °C (ventola di raffreddamento eliminata)

- Resa di produzione aumentata dall'81% al 96%

- Tempo di assemblaggio ridotto del 43%

- Risparmi totali: 847.000 $/anno su 20.000 unità

Questa guida rivela le esatte tecniche di ottimizzazione che utilizziamo, con misurazioni e calcoli reali che puoi applicare immediatamente.

Ottimizzazione Integrità del Segnale: Miglioramenti Misurabili

Controllo Impedenza Senza Materiali Premium

La maggior parte dei progetti sovra-specifica i requisiti di impedenza, aggiungendo costi non necessari. Ecco cosa conta realmente:

Requisiti Reali per Applicazione:

- USB 2.0: Tolleranza impedenza ±10% sufficiente (non ±5%)

- Ethernet 1 Gbps: ±7% funziona in modo affidabile

- PCIe Gen3: ±5% richiesto solo per tracce >8 pollici

- HDMI 2.0: ±5% per lane principali, ±10% per ausiliarie

Impatto Costi:

- Tolleranza ±10%: FR4 standard, nessun costo aggiuntivo

- Tolleranza ±7%: +2–4 $ per scheda

- Tolleranza ±5%: +8–12 $ per scheda

Tecnica di Ottimizzazione: Calcola i requisiti di impedenza effettivi basati su lunghezza traccia e velocità dati. Esempio: traccia USB 3.0 da 3 pollici necessita solo controllo ±8%, non i ±5% spesso specificati. Risparmi: 6 $/scheda × 10.000 unità = 60.000 $.

Ottimizzazione Via per Segnali Alta Velocità

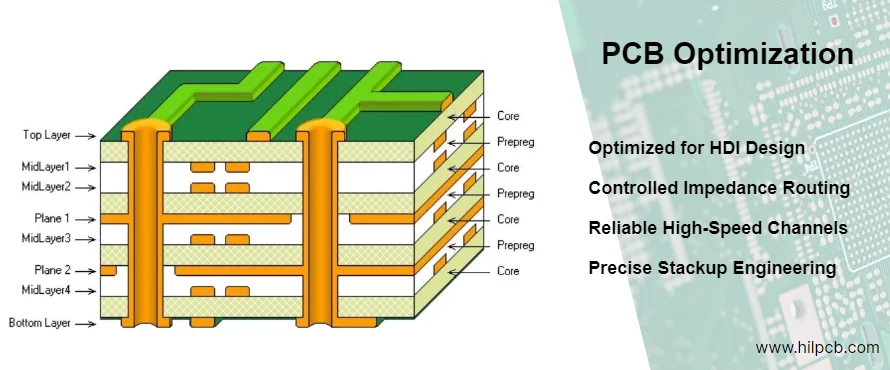

Problema: Monconi via non necessari creano discontinuità di impedenza Soluzione Tradizionale: Backdrilling (+15–25 $/scheda) Soluzione Ottimizzata: Accoppiamento strategico strati

Esempio ottimizzazione:

- Sposta segnali alta velocità agli strati 1–2 o N-1 a N

- Moncone via ridotto da 62 mil a 8 mil senza backdrilling

- Risultato: Miglioramento -12 dB in S11, 20 $/scheda risparmiati

Guadagni Prestazionali Misurati:

| Configurazione Via | Perdita Inserzione @ 10GHz | Impatto Costo |

|---|---|---|

| Via passante (moncone 62 mil) | -3,2 dB | Baseline |

| Via backdrilled (moncone 10 mil) | -0,8 dB | +18 $/scheda |

| Accoppiamento strati ottimizzato (moncone 8 mil) | -0,9 dB | Nessun costo aggiuntivo |

Ottimizzazione Termica: Eliminare Hardware di Raffreddamento

Bilanciamento Rame per Diffusione Termica Naturale

La Regola 70/30: 70% della gestione termica avviene attraverso corretta distribuzione rame, solo 30% attraverso componenti e via.

Processo di Ottimizzazione:

- Calcola mappa dissipazione potenza (W/cm²)

- Aggiungi rame flooding dove dissipazione >0,5 W/cm²

- Bilancia rame tra strati (entro 15%)

- Collega zone termiche con array di via

Esempio Reale: Scheda Amplificatore di Potenza

- Prima: Temperatura giunzione 85 °C, richiesto dissipatore

- Dopo ottimizzazione: Giunzione 61 °C, nessun dissipatore necessario

- Cambiamenti: Aggiunto rame flooding 2 oz, array via termici (0,3 mm dia, passo 1 mm)

- Impatto costo: +3 $ costo scheda, -12 $ dissipatore, -2 $ assemblaggio

Ottimizzazione Produzione: DFM Che Riduce Effettivamente i Costi

Matematica Utilizzo Pannello

La maggior parte dei progettisti ignora la pannellizzazione, perdendo 20–40% in efficienza materiale.

Dimensioni Pannello Standard:

- 18" × 24" (457 mm × 610 mm) - Più comune

- 18" × 21" (457 mm × 533 mm) - Migliore per schede piccole

- 21" × 24" (533 mm × 610 mm) - Premium, costo più alto

Algoritmo di Ottimizzazione:

- Calcola area utilizzabile (sottrai bordi 15 mm)

- Testa rotazioni (0°, 90°)

- Includi canali di routing (3 mm tipico)

- Ottimizza configurazione array

Esempio Reale:

- Originale: Scheda 97 mm × 73 mm

- Posizionamento standard: Array 4×5 = 20 schede/pannello

- Ottimizzato (95 mm × 71 mm + rotazione): Array 5×6 = 30 schede/pannello

- Risultato: 50% più schede per pannello, riduzione costo 33%

Tecniche Riduzione Tempo Assemblaggio

Ottimizzazione Posizionamento Componenti:

| Fattore | Impatto Tempo | Impatto Costo/1000 schede |

|---|---|---|

| Doppia faccia → Singola faccia | -47% | -8.500 $ |

| Orientamento casuale → Unificato | -23% | -4.100 $ |

- Ottimizzazione Posizionamento Componenti (continua)

| Fattore | Impatto Tempo | Impatto Costo/1000 schede |

|---|---|---|

| Package misti → Standard | -19% | -3.400 $ |

- Ottimizzazione Posizionamento Componenti (continua)

| Fattore | Impatto Tempo | Impatto Costo/1000 schede |

|---|---|---|

| Componenti 0402 → 0603 | -15% | -2.700 $ |

- Ottimizzazione Posizionamento Componenti (continua)

| Fattore | Impatto Tempo | Impatto Costo/1000 schede |

|---|---|---|

| Posizionamento sparso → Raggruppato | -12% | -2.150 $ |

Ottimizzazione Alimentatori: Macchine pick-and-place standard hanno 40–80 slot alimentatore. Superare richiede ricarica:

- Progetto con <40 parti uniche: Setup singolo, più veloce

- 40–80 parti uniche: Produzione standard

80 parti uniche: Setup multipli, +50% tempo assemblaggio

Un cliente ha ridotto parti uniche da 93 a 37 attraverso ottimizzazione. Risultato: Riduzione costo assemblaggio 11 $/scheda.

Checklist Ottimizzazione PCB

Vittorie Rapide (Implementa Oggi):

- Combina punti test entro 50 mm per efficienza sonda volante

- Standardizza dimensioni via (riduce cambi trapano)

- Usa 0,2 mm traccia/spazio solo dove necessario

- Elimina angoli acuti (<90°) nelle tracce

- Aggiungi teardrop ai via sotto BGA

Sforzo Medio (Progetti 1 Settimana):

- Consolida rail alimentazione dove possibile

- Ottimizza posizionamento connettori per gestione cavi

- Implementa copper thieving appropriato

- Rivedi e riduci conteggio parti uniche

- Verifica tolleranze effettive vs specificate

Ottimizzazione Maggiore (Livello Redesign):

- Analisi riduzione numero strati

- Migrazione tecnologia (HDI, componenti embedded)

- Ottimizzazione architettura per costo

- Ottimizzazione catena fornitura

Ottimizzazione Rete Distribuzione Alimentazione (PDN)

Ottimizzazione Condensatori Disaccoppiamento

La maggior parte dei progetti ha il 50% in più di condensatori bypass del necessario, aggiungendo costi senza beneficio.

Approccio Scientifico:

- Calcola requisito risposta in frequenza

- Modella impedenza PDN con rete condensatori

- Rimuovi condensatori ridondanti mantenendo impedenza target

- Valida con misurazione

Esempio: Ottimizzazione Rail Alimentazione FPGA

- Originale: 47× 0,1 µF, 22× 1 µF, 8× 10 µF condensatori

- Analisi: Target impedenza raggiunto con 40% meno parti

- Ottimizzato: 24× 0,1 µF, 12× 1 µF, 6× 10 µF

- Risparmi: 3,80 $/scheda in componenti + 2,10 $ in assemblaggio

Consolidamento Multi-Rail

I PMIC moderni eliminano multipli regolatori discreti:

Prima: Scheda processore embedded

- 5V → 3,3V (3A): Switching discreto

- 5V → 1,8V (2A): Switching discreto

- 5V → 1,2V (4A): Switching discreto

- Totale: 38 componenti, 8,70 $, 15 cm² spazio

Dopo: Soluzione PMIC singola

- Tutti i rail da un TPS650861

- Totale: 12 componenti, 4,20 $, 4 cm² spazio

- Bonus: Sequenziamento e monitoraggio integrati

Per progetti di ottimizzazione complessi, ottieni guida esperta attraverso consulenza PCB. Confronta costi di ottimizzazione con il nostro sistema trasparente di preventivo PCB. Per miglioramenti maggiori, considera completo redesign PCB.

FAQ: Ottimizzazione PCB

D: Quanto può realisticamente risparmiare l'ottimizzazione? R: Risparmi tipici: 20–40% su BOM, 15–30% su assemblaggio, 10–25% su fabbricazione PCB. Un cliente ha risparmiato 73 $ per scheda su un progetto precedentemente considerato "ottimizzato".

D: L'ottimizzazione influenzerà l'affidabilità? R: L'ottimizzazione appropriata migliora l'affidabilità. Migliore gestione termica, alimentazione più pulita e miglioramenti DFM tipicamente aumentano MTBF del 30–50%.

D: Quanto tempo richiede l'analisi di ottimizzazione? R: Revisione DFM base: 24 ore. Studio di ottimizzazione completo: 3–5 giorni. Implementazione: 1–2 settimane a seconda dello scope.

D: Puoi ottimizzare senza file di progetto originali? R: Sì, reverse-engineering da Gerber o schede fisiche. Questo aggiunge 2–3 giorni alla timeline.

D: Qual è il ROI sui servizi di ottimizzazione? R: La maggior parte dei progetti vede payback 6–12 mesi. Esempio: Servizio ottimizzazione 5.000 $ risparmiando 35 $/scheda si ripaga in 143 unità.

![Tecniche di Ottimizzazione PCB: Riduci i Costi del 40% Migliorando le Prestazioni [Basato su Dati]](/assets/img/blogs/pcb-optimization.webp)