以太网连接仍然是现代网络基础设施的支柱,从企业数据中心到工业自动化系统。随着数据传输速度从快速以太网持续升级到多千兆标准,以太网PCB设计的复杂性呈指数级增长。本综合指南探讨了以太网PCB设计和制造的关键方面,重点关注定义成功高速网络实施的技术挑战。

以太网标准的演进为PCB布局、信号完整性和制造精度引入了日益严格的要求。现代以太网实施,特别是支持1000BASE-T、2.5GBASE-T和10GBASE-T标准的实施,需要对差分信号、电磁兼容性和先进制造技术的深入理解。在HILPCB,我们在高速PCB制造方面的专业知识使我们能够精确可靠地应对这些挑战。

以太网PCB架构和系统集成

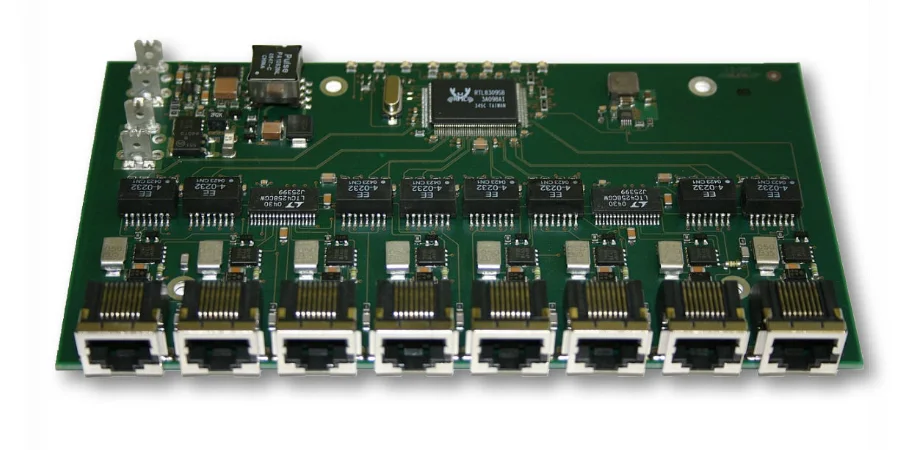

以太网PCB架构基本上由三个相互连接的元素组成:媒体访问控制(MAC)层、物理层(PHY)收发器以及带有RJ-45连接的磁性隔离电路。每个组件在信号处理链中都有不同的功能,但它们的集成需要仔细考虑电气特性和物理放置。

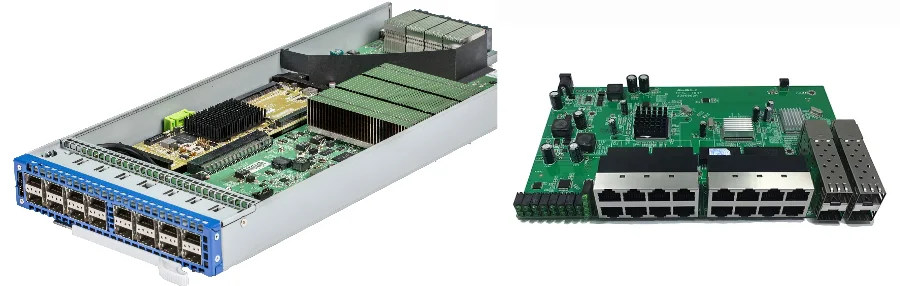

MAC层通常集成在微控制器或专用交换控制器中,处理数据包形成、碰撞检测和媒体访问协议。现代实施通常具有集成的MAC/PHY组合,特别是在空间优化至关重要的微控制器应用中。然而,高端口数交换应用经常需要单独的PHY收发器来实现必要的通道密度和性能特征。

关键架构元素:

- MAC/PHY接口:具有精确时序要求的MII、RMII、GMII和RGMII协议

- 差分信号:100欧姆阻抗控制,±10%容差,以实现最佳信号完整性

- 磁性隔离:带有Bob Smith终端的变压器耦合电路,用于EMI抑制

- 电源管理:具有专用去耦策略的多轨电源传输

PHY收发器执行将数字信号转换为适合铜缆或光纤媒体的模拟传输格式的关键功能。这些设备实施复杂的数字信号处理算法,包括回声消除、串扰缓解和自适应均衡。MAC和PHY层之间的电气接口遵循标准化协议,每个协议都针对特定的数据速率和实施要求进行了优化。

对于需要优越电气性能的应用,我们的FR4 PCB解决方案为可靠的以太网实施提供了基础,同时保持批量生产的成本效益。

以太网PCB的信号完整性和阻抗控制

信号完整性代表了以太网PCB设计中最关键的技术挑战,特别是对于千兆位和多千兆位实施。基本要求集中在整个信号路径中维持100欧姆差分阻抗,从PHY收发器输出通过磁性电路到RJ-45连接器接口。

差分阻抗控制需要精确管理走线几何形状、介电特性和电磁场分布。走线宽度、间距和介电高度之间的关系决定了差分对的特征阻抗。对于εr = 4.3-4.7的典型FR4结构,在标准叠层配置上实现100欧姆差分阻抗通常需要6-8密尔的走线宽度和6-8密尔的间距。

关键信号完整性参数:

- 阻抗控制:100Ω ±10%差分阻抗,带TDR验证

- 长度匹配:对内偏斜<50密尔,对间偏斜<200皮秒

- 过孔管理:每个走线最多2个过孔转换,带有受控焊盘尺寸

- 回流路径连续性:所有差分布线下方不间断的参考平面

差分走线对之间的边缘耦合效应在阻抗计算中引入了额外的复杂性。当差分走线边到边间距小于30密尔时,电容耦合可以将有效差分阻抗降低5-20欧姆。这种现象需要在设计阶段通过调整走线几何形状或修改间距要求进行补偿。

先进的高频PCB材料为要求苛刻的以太网应用提供了优越的电气性能。具有降低耗散因子和在频率范围内稳定介电常数的低损耗介电材料能够在多千兆位数据速率下改善信号完整性。

组件放置和布局优化

战略性组件放置构成成功以太网PCB实施的基础,直接影响信号完整性、电磁兼容性和制造良率。PHY收发器、磁性电路和RJ-45连接器之间的空间关系需要仔细优化,以在保持实际制造约束的同时实现最佳电气性能。

PHY收发器和磁性电路之间的关键距离应保持在最少25mm(约1英寸),以减少EMI。这种分离减少了来自PHY的高频数字开关噪声与磁性隔离变压器内敏感模拟电路之间的耦合。

放置指南:

- PHY到磁性器件距离:最小25mm分离以减少EMI

- 磁性器件到RJ-45距离:分立实施最大25mm

- 数字信号隔离:与差分对最少300密尔分离

- 去耦放置:PHY电源引脚10mm内以获得最佳效果

组件之间的差分走线路由需要平行路由,具有匹配的长度和受控的间距。从PHY到连接器的总走线长度不应超过4英寸(100mm),以最小化信号衰减并保持可接受的信噪比。在此约束内,差分对应保持平行路由,间距变化最小化以保持阻抗控制并减少模式转换。

对于具有高引脚数设备的复杂路由要求,我们的HDI PCB技术能够实现紧凑设计,具有卓越的路由密度,同时保持信号完整性要求。

以太网PCB制造中的接地平面设计和EMI缓解

有效的接地平面设计在以太网PCB制造中至关重要,因为它直接影响信号完整性、EMI抑制和法规合规性。正确的实施确保高速差分信号保持清洁的回流路径和稳定的性能。

关键接地平面原则:

- 连续参考平面 – 在所有差分走线下提供不间断的接地以保持低阻抗回流路径。

- 避免平面分割 – 差分对下方的间隙可能会破坏回流电流并增加EMI发射。

- 磁性隔离区域 – 在分立磁性组件下保持接地平面清洁以防止不必要的耦合。

- 机箱接地集成 – 为连接器模块和EMI屏蔽使用专用机箱接地。

- 受控终端区域 – 在终端区域周围保持适当的间隙和阻抗。

多层叠层允许功能接地的分离,同时保持信号层与相邻平面紧密耦合,减少环路电感和辐射噪声。以太网PCB制造中正确的接地平面策略确保强大的EMI性能、信号可靠性和符合网络标准。

专业以太网PCB制造和装配服务

在HILPCB,我们提供先进的以太网PCB制造和装配服务,将高频设计专业知识与精密制造能力相结合。我们的综合方法涵盖从组件规格到最终装配测试的完整信号链,确保要求苛刻的网络应用的可靠性能。

制造能力:

- 阻抗控制制造:±5%容差,带统计过程控制和测试样本

- 先进过孔技术:激光钻孔微过孔、顺序层压和精密电镀

- 高频材料:Rogers基板和低损耗介电材料,具有优越的射频性能

- 精密装配:0.4mm BGA放置,±25µm精度,全面AOI/ICT测试

- 质量系统:ISO 9001:2015合规性,完全可追溯性和统计过程控制

阻抗控制制造代表以太网PCB生产的关键能力。实现所需的100欧姆差分阻抗需要精确控制走线几何形状、介电厚度和铜电镀参数。铜电镀厚度、介电常数和叠层配准中的制造工艺变化可能显著影响最终阻抗值。

我们的交钥匙装配服务提供从原型开发到大批量生产的完整制造解决方案,确保所有生产阶段的一致质量和性能。

以太网PCB的测试和验证程序包括直流电气特性和高频性能参数。时域反射测量(TDR)测试验证阻抗控制并识别高速信号路径中的不连续性。网络分析表征与特定以太网标准相关的频率范围内的插入损耗、回波损耗和串扰性能。

关于以太网PCB设计的常见问题

问:以太网PCB设计与标准数字PCB有何不同?

答:以太网PCB设计需要精确的100欧姆差分阻抗控制、专门的磁性隔离电路、先进的EMI缓解技术以及仔细的组件放置,以在千兆位速度下保持信号完整性。PHY到磁性器件接口的模拟特性需要优越的噪声控制和回流路径管理。

问:高速以太网应用推荐哪些基板材料?

答:对于10GBASE-T和更高速度,像Rogers RO4350B这样的低损耗材料提供最佳性能。标准高质量FR4适用于1000BASE-T应用,而2.5GBASE-T和5GBASE-T可能受益于中等损耗基板,这取决于实施要求和成本约束。

问:如何确保以太网PCB性能符合IEEE标准?

答:我们实施包括TDR阻抗验证、插入/回波损耗的S参数测量、串扰分析和EMC预合规测试在内的综合测试。我们的制造工艺通过阻抗测试样本和完整的电气测试协议保持统计过程控制。

问:以太网PCB布局的关键间距要求是什么?

答:关键间距要求包括:PHY到磁性器件最小25mm分离,分立实施的磁性器件到RJ-45最大25mm,差分对到数字信号最小300密尔分离,以及对内长度匹配在50密尔内以获得最佳信号完整性。

问:您能支持原型和生产以太网PCB要求吗?

答:是的,我们提供从初始设计咨询到大批量生产的完整以太网PCB服务。我们的能力包括阻抗建模、设计优化、原型制造、精密装配、综合测试以及带有完整质量文档和可追溯性系统的持续生产支持。