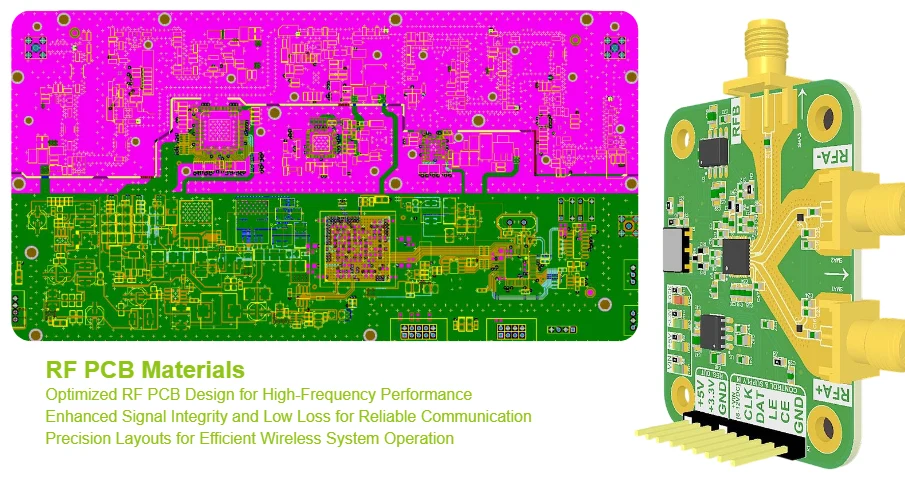

与传统数字电路相比,RF PCB设计需要完全不同的方法。在1 GHz以上的频率下,每条走线都成为传输线,传统设计规则完全失效。在Highleap PCB工厂,我们经过15年以上的实践完善了RF设计方法,帮助工程师应对高频电路实现的复杂性。

RF设计成败的关键往往在于理解电磁场在高频下的行为。信号波长与PCB尺寸相当,使得每个设计决策都对性能至关重要。

理解RF设计基础

随着频率升高,RF电路行为会发生显著变化。在1 GHz时,FR4基板中的波长约为100mm——通过精心设计仍可管理。但在10 GHz时,波长缩短至仅15mm,使得四分之一波长段仅有3.75mm长。

这种比例效应意味着传统PCB特性如过孔、弯曲和元件焊盘会产生显著的电磁不连续性。在直流下看似简单的连接,在RF频率下会变成复杂的阻抗变换器。

关键RF现象:

- 趋肤效应:电流集中在导体表面,增加电阻

- 介质损耗:PCB材料吸收RF能量,衰减信号

- 电磁耦合:相邻走线通过电场和磁场相互作用

- 地弹:高频电流在接地平面上产生电压波动

解决方案是将每条PCB走线视为具有精心管理特性阻抗的受控传输线,单端信号通常为50欧姆,差分对为100欧姆。

RF成功的关键布局技术

RF布局优先级

信号完整性

在整个信号路径中保持受控阻抗,以实现最小反射和最佳性能。

地管理

为RF电流建立连续返回路径,避免信号劣化和噪声。

EMI控制

实施策略以最小化电磁干扰,确保可靠的信号质量。

热管理

通过合理的元件布局和散热孔设计确保有效散热,防止过热。

层叠优化

将关键射频信号布置在外层,直接接触地平面,确保更紧密的场控制。

电源分配

设计低阻抗电源分配网络,使用电容实现有效去耦和储能。

射频布局始于智能化的层叠设计。将最关键射频信号布置在外层,使其直接接触地平面。这种配置能提供最紧密的场控制和最可预测的阻抗特性。

核心布局规则:

走线布线:尽可能缩短射频走线,使用柔和曲线而非90度直角。锐角弯折会造成阻抗不连续,导致能量反射回源端。

元件布局:布置关键射频元件以最小化互连长度。目标是在保持信号完整性的同时,为不同电路模块提供充分隔离。

过孔策略:每个过孔都会引入寄生电感和电容。在关键信号路径中尽可能减少过孔数量,必要时优化过孔尺寸并通过背钻去除无用残桩。

接地缝合:沿射频走线每四分之一波长布置接地过孔。这确保回流路径紧贴信号路径,最小化环路面积和电磁辐射。

材料选择策略

PCB基板材料的选择直接影响射频性能、成本和可制造性。标准FR4材料在1GHz以下表现良好,但更高频率需要采用具有可控介电特性的专用射频PCB材料。 Rogers RO4350B代表了大多数射频应用领域的行业标准,在性能、成本和可制造性之间实现了良好平衡。其介电常数为3.38,损耗角正切为0.0037,可处理高达77 GHz的频率,同时保持与标准PCB加工设备的兼容性。

对于需要超低损耗的应用,Rogers RO3003以仅0.0013的损耗角正切提供卓越性能。这种材料对于信号纯度至关重要的精密振荡器、低噪声放大器和测量设备至关重要。

在大规模生产中,成本优化变得尤为关键。与其在整个PCB上使用昂贵的射频材料,不如考虑混合方案:仅在关键射频层使用优质材料,而电源层、地层和数字控制层采用标准材料。该策略可在不影响射频性能的前提下降低40-60%的材料成本。

阻抗控制实现

受控阻抗是成功射频设计的核心。当特性阻抗与系统阻抗(通常为50欧姆)匹配时,可实现从源到负载的最大功率传输,并将反射降至最低。

实现精确阻抗控制需要仔细关注走线几何形状、介质厚度和制造公差。现代场求解器工具可将阻抗预测精度控制在2-3%以内,但如果控制不当,制造偏差很容易超出该精度范围。

关键参数:

- 走线宽度:与阻抗成反比 - 较宽的走线阻抗较低

- 介质厚度:与阻抗成正比

- 介电常数:高Dk材料会导致阻抗降低

- 走线厚度:影响较小,但较厚的铜会略微增加阻抗

制造公差控制至关重要。将走线宽度公差保持在±0.025mm(±1密耳)以内,介质厚度公差保持在±0.025mm以内,可实现±5%的阻抗精度。对于需要±3%公差的临界应用,这些制造控制必须更加严格。

测试验证阻抗控制策略。时域反射计(TDR)可提供沿走线长度的详细阻抗分布,而网络分析仪测量可确认频率范围内的性能。我们的射频PCB测试服务包含全面验证,确保设计符合规范。

电源分配与EMI管理

射频电路会产生电磁场并受其影响,因此EMI控制对可靠运行至关重要。不良的EMI设计会导致振荡、灵敏度下降和杂散发射,从而违反法规要求。 电源分配网络(PDN)设计始于低阻抗供电。采用专用电源层并配置多级不同频率的去耦电容:将小型陶瓷电容(10pF至100pF)靠近RF芯片电源引脚用于高频去耦,较大电容(1µF至10µF)用于中频储能。

地平面管理至关重要。在RF走线下保持连续完整的地平面,避免分割或间隙。当无法避免地平面不连续时,使用多个缝合过桥接以提供替代回流路径。

隔离技术可防止电路模块间产生非预期耦合。采用接地保护走线隔离敏感模拟电路与数字开关电路。对于极端隔离需求,可考虑采用接地金属屏蔽罩。

物理间距同样有效。平行RF走线间距至少保持三倍线宽以最小化串扰。差分信号应保持紧密对间距(通常1-2倍线宽),在最大化差分对耦合的同时最小化与其他电路的耦合。

测试验证流程

验证工作需确认RF设计在所有工况下均符合预期。该流程应从设计初期的仿真开始,延续至样机测试和生产认证阶段。

设计验证始于HFSS或CST等工具的电磁仿真。这些3D求解器能精确预测复杂RF结构(包括连接器、过孔转换和元件互扰)的性能表现。

样机测试通过硬件测量验证仿真结果。关键参数包括S参数(回波损耗、插入损耗、隔离度)、阻抗曲线和功率承载能力。

环境测试确保器件在温湿度变化和机械应力下可靠工作。由于材料特性变化和机械膨胀,RF性能会随温度显著偏移。

量产阶段需建立明确的测试标准和验收限值。记录所有测试程序并实施统计过程控制以监控生产一致性。

准备好将RF概念转化为实体硬件了吗?我们的专业RF设计团队可全程指导,从初始概念到生产认证。