在数据速率超过100 Gbps、射频系统突破40 GHz的时代,传统电路板材料已达到其物理极限。介质和导体中的损耗开始侵蚀信号裕量、缩小抖动预算并损害系统可靠性。这就是超低损耗PCB的用武之地--一种采用精英材料和精密制造工艺设计的电路板,旨在最小化插入损耗、保持信号保真度,并支持下一代高速电子产品。

本综合指南将探讨超低损耗PCB与标准设计的区别、如何选择正确的材料,以及实现数据中心、5G基础设施和卫星通信等系统峰值性能所需的关键设计和制造实践。

目录

什么是超低损耗PCB?

超低损耗PCB的核心定义是一个主要特征:显著降低的信号衰减,尤其是在高频下。与标准板相比,其优势显而易见:

- 显著降低的插入损耗: 支持在背板上进行更长的走线或更高的数据速率,无需昂贵的重驱动器或中继器。

- 卓越的相位稳定性和更低的色散: 对于相干通信系统、相控阵天线和高频射频应用至关重要。

- 减少的信号发热: 最小化导体和介质发热,从而提高功率处理能力和长期可靠性。

- 更高的信噪比 (SNR): 保持信号的完整性,使得能够使用先进的高阶调制方案。

虽然标准FR-4可能足以满足基本数字逻辑需求,但当您的损耗预算紧张时--无论是在高速串行链路还是毫米波雷达模块中--超低损耗设计不再是一种选择,而是必需品。

影响信号完整性的关键因素 {#影响信号完整性的关键因素}

要设计超低损耗PCB,设计人员必须应对三个基本的信号劣化源:

1. 介质损耗(通过损耗因数Df测量): 这是最关键的因素。介质损耗量化了基板材料吸收信号电磁能并将其转化为热量的多少。它就像一种“电摩擦”,在信号传输过程中削弱信号。超低损耗材料由其极低的Df值定义,通常在目标频率下低于0.002。

2. 导体损耗(受铜粗糙度影响): 在高频下,电流仅沿走线外表面流动(趋肤效应)。粗糙的铜箔会增加走线的有效路径长度和电阻,从而增加导体损耗。超低损耗设计要求使用极低轮廓(VLP)或光滑反处理铜箔来最小化这种影响。

3. 色散(受介电常数Dk稳定性影响): 虽然低Dk有利于信号速度,但其跨频率的稳定性才是真正区分高性能材料的因素。Dk随频率变化的材料会引起色散,即信号的不同频率分量在不同时间到达。这会“涂抹”信号,扭曲其波形,并关闭数据眼图。

选择超低损耗层压板的分层指南

选择合适的层压板是低损耗设计中最重要的决策。以下是材料的关键层级:

- 层级 1: 高性能环氧树脂和混合材料 (Df ~0.004 - 0.008): 这些材料相比标准FR-4有显著提升,适用于许多高速数字应用。它们在性能、成本和可制造性之间提供了良好的平衡。

- 层级 2: 碳氢化合物和陶瓷填充混合物 (Df ~0.002 - 0.004): 这类材料是当今要求最苛刻的数字和高频系统的主力。它们为56/112 Gbps数据通道和许多射频应用提供了优异的性能。

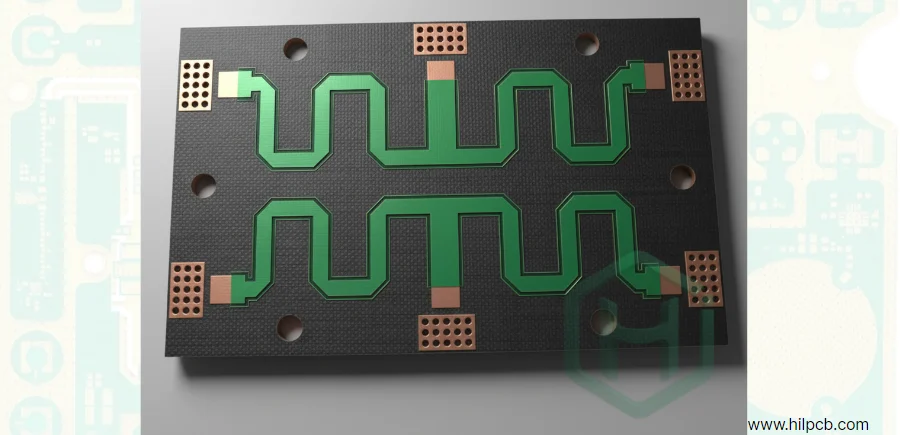

- 层级 3: PTFE基层压板 (Teflon™) (Df < 0.002): 这是黄金标准。PTFE及其复合材料提供了可能的最低介质损耗,使其成为关键任务毫米波雷达、卫星通信和最先进高速测试设备的唯一选择。

专业提示: 务必指定确切的材料数据表以及必须满足Dk/Df值的频率。这可以防止在测试制造好的电路板时出现“性能意外”。

最大化超低损耗PCB性能的设计策略

即使最高性能的材料也可能因次优设计而失效。实现最小损耗和最大信号保真度需要结合仔细的规划、仿真和布局纪律。以下是最有效的策略:

利用高级场求解器进行精确阻抗建模: 通用计算器通常无法捕捉超低损耗材料和复杂铜轮廓的细微相互作用。现代场求解器模拟电磁行为,考虑精确的介电常数、铜粗糙度和走线几何形状。这确保了高频走线在整个板上保持其预期的特性阻抗,减少反射并保持信号完整性。

最小化走线长度并避免不必要的弯曲: 每一毫米铜都会引入插入损耗和相位延迟。尽可能保持走线短、直且平滑,不仅减少了介质和导体损耗,还降低了串扰和信号失真的风险。温和的曲线优于尖锐的90°弯曲,后者在高频下会产生阻抗不连续性。

消除信号残桩并优化过孔设计: 未使用的过孔残桩在高频下像微型天线一样,产生共振零点,降低信号质量。背钻、盲孔或埋孔等技术可以移除这些残桩,防止反射引起的失真。适当的过孔设计--包括焊盘尺寸、反焊盘间距和电镀质量--在保持一致性阻抗和最小化寄生电感方面也起着关键作用。

确保连续且低电感的返回路径: 高速信号需要每个走线旁边有一个不间断的接地层。坚实的返回路径减少了环路面积,保持了阻抗,并最小化了电磁干扰(EMI)。层叠规划、仔细分离信号层与电源层以及策略性的过孔缝合,都是维持稳定返回电流路径的基本实践。

控制串扰和层间相互作用: 高密度布局增加了串扰的风险。保持高速信号之间的足够间距,考虑使用差分对布线以提高抗噪性,并在必要时使用屏蔽层。仿真工具可以预测层间的耦合,从而在制造前进行设计调整。

通过仿真迭代和验证: 即使采用最佳设计实践,超低损耗PCB也需要验证。时域和频域仿真--使用S参数和眼图分析--可以在生产前验证布局是否满足目标插入损耗、回波损耗和信号上升/下降要求。

通过整合这些策略,工程师可以充分利用超低损耗材料的优势,即使在要求最苛刻的高速或射频应用中,也能实现最小的插入损耗、稳定的阻抗和最大的信号保真度。

为什么制造精度不容妥协

超低损耗PCB要求更高水平的制造专业知识。关键关注领域包括:

- 专业层压和粘结工艺: 像PTFE这样的材料需要独特的温度曲线和粘结膜,这与标准FR-4处理不同。

- 高精度钻孔和电镀: 许多低损耗基材的柔软特性需要专门的钻孔技术,以创建对信号完整性至关重要的清洁、可靠的过孔壁。

- 严格的质量验证: 性能必须被证明,而不是假设。我们使用时域反射计(TDR)验证每个面板的阻抗,并使用网络分析仪进行S参数测量,以确认电路板满足其指定的插入损耗预算。

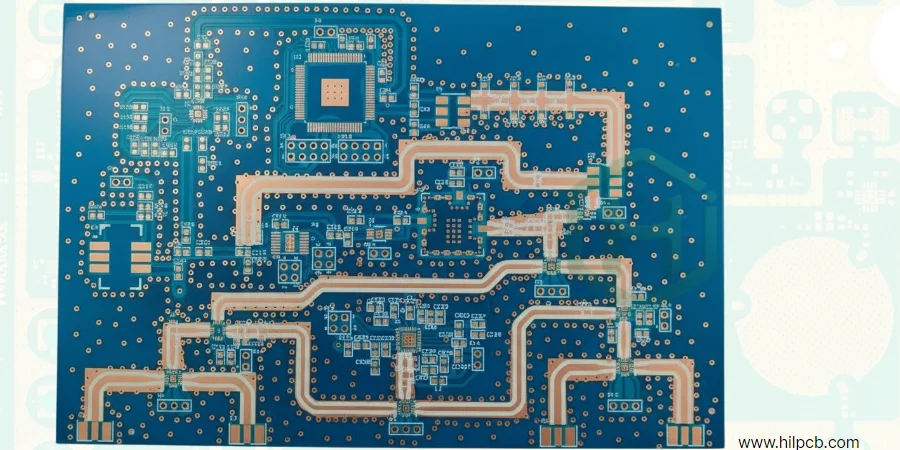

推动超低损耗PCB需求的关键应用

这项技术的需求由那些每一分贝损耗和每一皮秒延迟都至关重要的行业驱动:

- 数据中心背板和线卡 (100/400/800 Gbps)

- 5G 和 6G 毫米波基础设施 (相控阵天线)

- 汽车雷达和ADAS (77 GHz 及以上)

- 卫星和航空航天通信有效载荷

- 高速测试和测量设备

结论

设计超低损耗PCB不仅仅是选择正确的材料--它需要一种整体方法,结合先进的层压板、仔细的布局和精密的制造。通过解决介质和导体损耗、控制信号残桩以及维持干净的返回路径,工程师即使在最高数据速率下也能保持信号完整性。

对于高速数据中心、5G/6G基础设施、雷达系统和卫星通信等应用,超低损耗PCB不仅仅是一项技术改进--它是性能、可靠性和面向未来设计的关键推动者。今天投资于细致的设计和制造,确保您的系统能够自信地应对明天的速度和复杂性。