HDI PCB制造 | 50–75微米微孔、任意层、VIPPO | IATF 16949认证

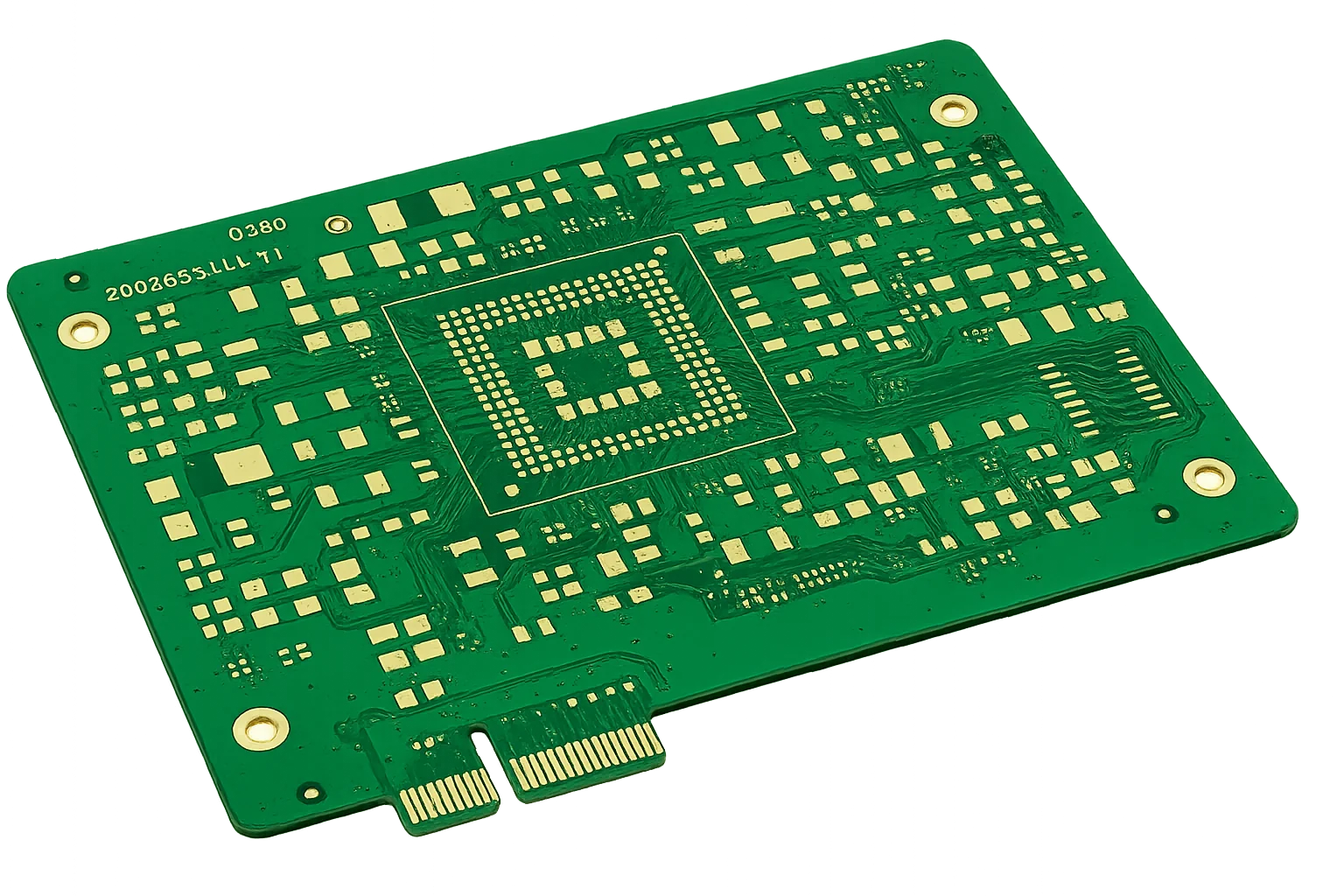

高密度互连(HDI) PCB,具备50–75微米激光微孔、1+N+1至任意层架构、孔内填铜镀覆(VIPPO)技术,以及适用于10–56 Gbps(每秒10至56千兆比特)的低损耗堆叠设计。阻抗控制±5%(正负5%)并通过TDR验证。提供7天快速交付服务。

HDI技术选型与价值工程

密度与性能平衡的叠层架构当BGA间距小于0.8毫米或层数超出经济限制时,HDI技术开始被采用。我们评估3个决策节点:微孔堆叠高度(通常限于2层以确保可靠性)、顺序压合周期(1+N+1与2+N+2的成本效益对比)以及工作频率超过5–8 GHz时的材料转换。通过系统的叠层优化,总厚度通常可减少25–40%,同时保持IPC-6012 Class 3可靠性。

50–75微米的激光微孔(纵横比≤1:1)可实现盘中孔扇出,相比狗骨布线减少约40–60%的寄生电感。对于>10–12 Gbps的差分对,更短的互连可保持眼图裕量并降低信号偏移。详细孔设计与测试关联请参阅我们的阻抗控制指南和微孔可靠性研究。

关键风险:过度堆叠微孔、树脂填充不良或压合不平衡可能导致热应力下的空洞、孔壁开裂和导电阳极丝(CAF)形成。过钻或高纵横比也会增加孔与捕获盘界面的失效风险。

我们的解决方案:我们强制执行IPC-6016和IPC-6012 Class 3微孔可靠性标准。每个叠层结构都经过Z轴膨胀模拟,采用真空辅助电镀填孔和平面化处理。截面分析和互连应力测试(IST)确认堆叠孔完整性及电镀Cpk≥1.33。对于超高密度设计,混合叠层结合多层PCB和背板PCB以实现布线与电源分配平衡。

- 微孔直径:50–75微米,纵横比≤1:1

- 顺序压合:支持1+N+1至任意层配置

- VIPPO凹陷深度<10%焊盘厚度

- 优化布局中差分对偏移控制至±5皮秒

- 关键层采用损耗因子0.005–0.012的低/超低损耗混合叠层

- 大型BGA的翘曲控制≤0.7%(小于或等于0.7%)

🚀 快速报价请求

🔧 获取完整制造能力

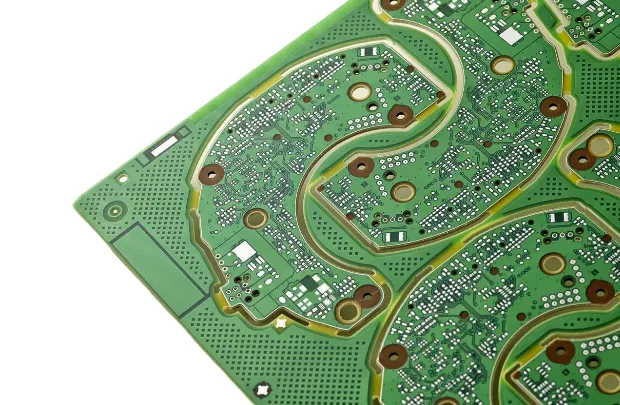

顺序叠加工艺控制与验证

通过多阶段对准验证实现层间对位精度多周期叠加工艺将层间对位精度保持在±25–50微米范围。355纳米UV-YAG激光在FR-4高Tg(170–180°C——170至180摄氏度)和低损耗系统中提供稳定的烧蚀效果。能量密度根据Dk/Df调整,以防止碳化并保持金属化所需的清洁侧壁。

铜填充材料根据可靠性选择:汽车级热循环(−40°C↔+125°C——零下40至零上125摄氏度)采用电解铜,成本优化的消费级产品采用导电浆料。量产前的CAM工程应用有限元分析预测微通孔拐角处的CTE应力。尺寸稳定性通过光学检测每面板5个0.0位,符合IPC-2226 C级标准。

- CO₂与UV激光光束精度±10微米

- 化学镀种子层均匀性±10%(正负10%)

- 堆叠通孔的X射线对准检测分辨率达5微米

- 通过IPC-TM-650 2.6.26标准IST(互连应力测试)认证

HDI PCB能力与性能矩阵

针对可靠性—成本平衡优化的工艺窗口

| 参数 | 标准能力 | 高级能力 | 标准 |

|---|---|---|---|

层数 | 4–30层 | 最高60+层 | IPC-2226 |

基材 | 高Tg FR-4、低Dk/Df材料 | Megtron 6/7、Isola I-Speed、Rogers RO4000 | IPC-4101 |

板厚 | 0.4–3.2毫米 | 0.2–6.0毫米 | IPC-A-600 |

最小线宽/间距 | 75/75微米(3/3密耳) | 50/50微米(2/2密耳) | IPC-2221 |

最小孔径(激光) | 0.10毫米(4密耳) | 0.05毫米(2密耳) | IPC-2226 |

过孔技术 | 盲/埋孔、微孔(1+N+1、2+N+2) | 堆叠/交错、VIPPO、任意层 | IPC-6012 |

纵横比(微孔) | 0.8:1(0.8比1) | 1:1(1比1) | IPC-2226 |

最大面板尺寸 | 500×400毫米 | 600×500毫米 | 制造能力 |

阻抗控制 | ±10%(正负10%) | ±5%(正负5%) | IPC-2141 |

表面处理 | HASL、ENIG、OSP、沉银 | ENEPIG、软/硬金、选择性OSP | IPC-4552/4556 |

质量检测 | 电测、AOI、X射线 | 4线开尔文、切片分析、IST、HAST | IPC-9252 |

认证 | ISO 9001、UL、RoHS | IATF 16949、ISO 13485、AS9100、MIL-PRF-31032 | 行业标准 |

交付周期 | 7–15天 | 24小时快速打样 | 生产计划 |

准备开始您的PCB项目了吗?

无论您需要简单的原型还是复杂的生产运行,我们先进的制造能力确保卓越的质量和可靠性。30分钟内获取您的报价。

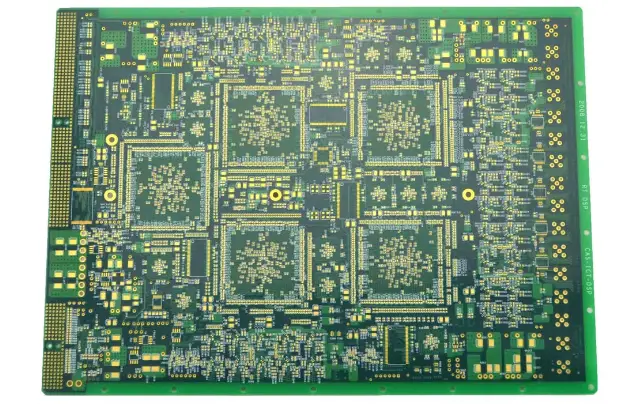

叠层架构与材料系统集成

当0.8毫米间距的BGA引脚数超过400–600针时,通常需要从1+N+1升级到2+N+2结构。我们在10 GHz频率附近建立约1/4λ(四分之一波长)的过孔残桩谐振模型,并将关键信号网络转移至盲孔/背钻路径。当插入损耗预算降至约0.8–1.0 dB/英寸时,采用低损耗介质材料(Df 0.009–0.012)具有合理性。详见HDI制造技术和盲孔优化方案。

叠孔微孔的可靠性取决于连续电镀的铜厚均匀性。我们要求孔壁铜厚≥18–20微米(通过切片验证)。交错式叠孔设计可提升20–30%的热循环寿命,但需占用更多面积。VIPPO填充材料的热膨胀系数(≈45–55 ppm/°C)经过优化以降低焊点应力;当单孔散热超过约2 W时则选用铜填充方案。

增层工艺优化与制程窗口控制

芯板预处理要求收缩率<0.05%。每个SBU循环包含:175–190°C层压、70–80°侧壁角度的激光钻孔、化学镀铜+电镀铜。除胶渣采用高锰酸盐工艺,在完全清除残留的同时最小化介质凹陷。环宽与孔距的制程能力指数Cpk保持≥1.33。脉冲反向电镀实现>80%的深镀能力。完整流程参见HDI技术指南。

层压后质检包含:10微米精度的AOI检测、微孔颈缩X射线断层扫描、飞针/夹具电气测试。4线开尔文法可验证±1毫欧电阻精度,用于临界互连检测。

通过受控阻抗实现高速性能

缩短过孔残桩与紧密平面耦合可改善回波损耗。对于>10 Gbps差分对,我们采用盲孔/背钻结构消除谐振残桩。当dB/in–GHz乘积接近极限时,选用超低损耗材料(Df 0.005–0.007)。我们的阻抗建模采用3D电磁场仿真分析过孔阵列与过渡结构,实现±5%的量产公差(通过测试板验证)。低轮廓铜箔(Rz<2微米)可降低约15–20%的导体损耗。超薄介质层(50–75微米)使PDN回路电感低于100皮亨。

可靠性验证:热循环、湿度与IST测试

热循环测试范围−40°C至+125°C(零下40至零上125摄氏度),每次停留15分钟,目标≥1000次循环且电阻变化不超过10%。IST通过焦耳热效应检测早期失效(通常在150°C下进行>500次循环——150摄氏度)。HAST测试条件130°C/85% RH(130摄氏度/100分之85相对湿度)持续96小时以验证防潮性能。

SEM横截面检测铜晶粒、附着力和空隙;IPC-A-600 Class 3验收标准包括≥5微米的包覆镀层且无膝裂。离子清洁度≤1.56微克/平方厘米NaCl当量。CAF测试条件65°C/88% RH(65摄氏度/100分之88相对湿度)下施加100 VDC持续≥500小时。

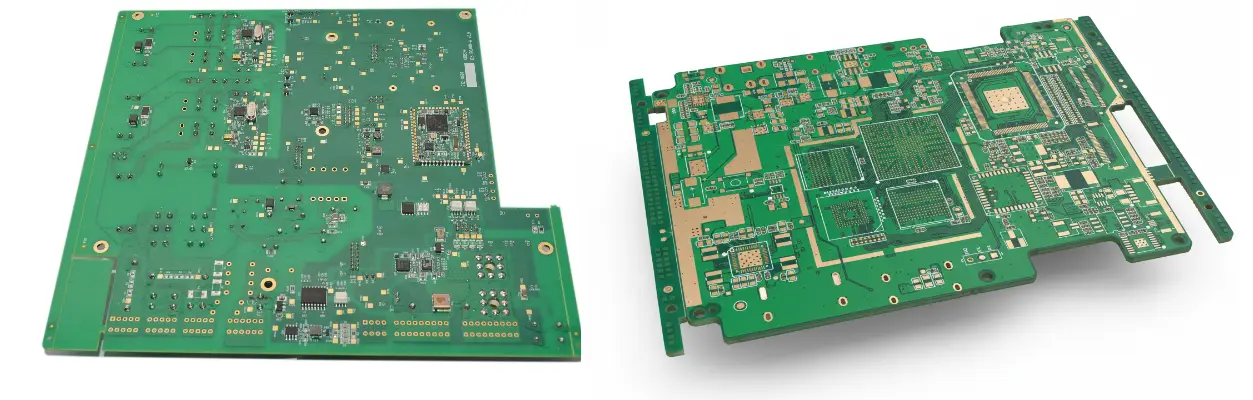

行业定制化HDI策略

汽车ADAS: 2+N+2叠层结构搭配选择性低损耗射频层,77 GHz(77千兆赫兹)时插入损耗<0.3 dB/in(小于每英寸0.3分贝),填充铜导热孔实现θJB<2°C/W(小于每瓦2摄氏度)。

医疗设备: 符合ISO 13485标准的任意层微缩技术。

数据通信/5G: 支持25–56 Gbps(每秒25至56千兆比特)SERDES;详见5G PCB技术。

消费电子: 仅在密度需求区域采用选择性HDI,降低成本15–25%。

工程保障与认证体系

经验: 经过量产验证的1+N+1至任意层方案,采用分区控制压合和LDI对位技术。

专长: 使用TDR/VNA进行过孔传输建模;对电镀和钻孔对位实施SPC管控;Cpk目标≥1.33(大于或等于1.33)。

权威认证: IPC Class 3、IATF 16949、ISO 13485、AS9100;提供端到端审核与文档支持。

可信赖性: MES系统追踪批次代码及序列号至在线测试数据;可提供IST/HAST认证报告。

- 工艺控制:镀层厚度、压合压力/温度、激光能量

- 追溯体系:单元序列化、元件批次追踪、数字化流程单

- 验证项目:IST测试、HAST测试、微切片审查、阻抗测试板

常见问题

如何在1+N+1和2+N+2 HDI之间做出选择?

什么因素限制了堆叠微孔的可靠性?如何缓解?

何时应该转向低损耗或超低损耗材料?

哪些因素对HDI价格影响最大?

能否在HDI上验证严格的阻抗公差?

体验先进的PCB制造卓越

从简单的原型到复杂的生产运行,我们的世界级工厂提供卓越的质量、快速的周转和有竞争力的价格。加入数千名信任我们PCB制造需求的满意客户。