Ethernet-Verbindungen bilden nach wie vor das Rückgrat der modernen Netzwerkinfrastruktur, von Unternehmensrechenzentren bis hin zu industriellen Automatisierungssystemen. Da die Datenübertragungsgeschwindigkeiten von Fast Ethernet auf Multi-Gigabit-Standards ansteigen, ist die Komplexität des Ethernet PCB-Designs exponentiell gewachsen. Dieser umfassende Leitfaden untersucht die entscheidenden Aspekte des Ethernet PCB-Designs und der Fertigung, wobei der Schwerpunkt auf den technischen Herausforderungen liegt, die erfolgreiche Hochgeschwindigkeitsnetzwerkimplementierungen definieren.

Die Entwicklung der Ethernet-Standards hat zunehmend strenge Anforderungen an PCB-Layout, Signalintegrität und Fertigungspräzision eingeführt. Moderne Ethernet-Implementierungen, insbesondere solche, die die 1000BASE-T-, 2.5GBASE-T- und 10GBASE-T-Standards unterstützen, erfordern ein tiefes Verständnis von Differenzialsignalen, elektromagnetischer Verträglichkeit und fortschrittlichen Fertigungstechniken. Bei HILPCB ermöglicht uns unsere Expertise in der Hochgeschwindigkeits-PCB-Fertigung, diese Herausforderungen mit Präzision und Zuverlässigkeit zu bewältigen.

Ethernet PCB-Architektur und Systemintegration

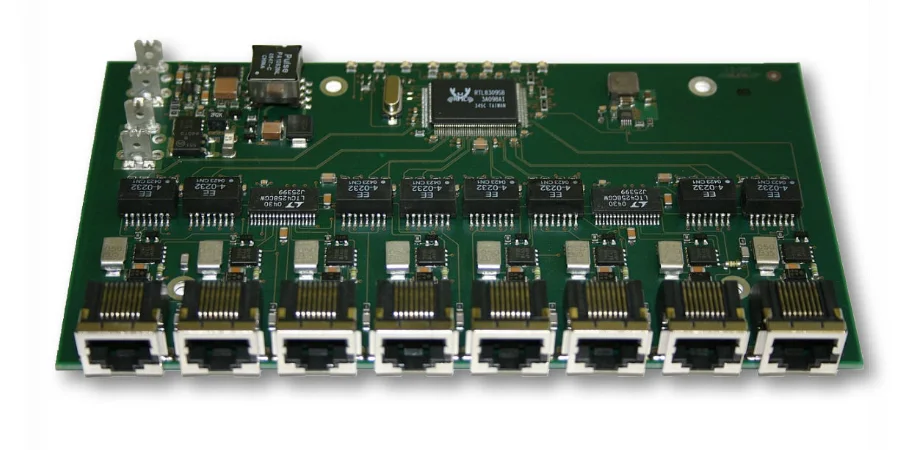

Die Ethernet PCB-Architektur besteht grundsätzlich aus drei miteinander verbundenen Elementen: der Media Access Control (MAC)-Schicht, dem Physical Layer (PHY)-Transceiver und der magnetischen Isolationsschaltung mit RJ-45-Anschluss. Jede Komponente erfüllt eine bestimmte Funktion in der Signalverarbeitungskette, doch ihre Integration erfordert eine sorgfältige Berücksichtigung der elektrischen Eigenschaften und der physischen Platzierung.

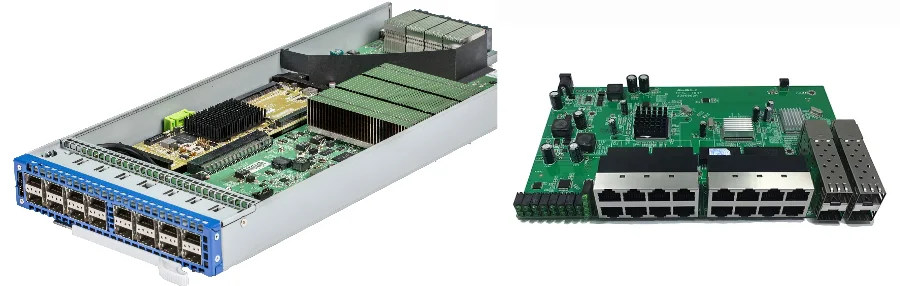

Die MAC-Schicht, die typischerweise in Mikrocontrollern oder dedizierten Switching-Controllern integriert ist, übernimmt die Paketbildung, Kollisionserkennung und Medienzugriffsprotokolle. Moderne Implementierungen weisen häufig integrierte MAC/PHY-Kombinationen auf, insbesondere in Mikrocontroller-Anwendungen, bei denen die Platzoptimierung entscheidend ist. Hochportzählige Switching-Anwendungen erfordern jedoch häufig separate PHY-Transceiver, um die erforderliche Kanaldichte und Leistungsmerkmale zu erreichen.

Wichtige Architekturelemente:

- MAC/PHY-Schnittstelle: MII-, RMII-, GMII- und RGMII-Protokolle mit präzisen Timing-Anforderungen

- Differenzialsignale: 100-Ohm-Impedanzkontrolle mit ±10 % Toleranz für optimale Signalintegrität

- Magnetische Isolation: Transformatorgekoppelte Schaltungen mit Bob-Smith-Terminierung zur EMI-Unterdrückung

- Stromversorgung: Mehrfach-Stromversorgung mit dedizierten Entkopplungsstrategien PHY-Transceiver erfüllen die entscheidende Funktion der Umwandlung digitaler Signale in analoge Übertragungsformate, die für Kupfer- oder Glasfasermedien geeignet sind. Diese Geräte implementieren ausgeklügelte digitale Signalverarbeitungsalgorithmen, einschließlich Echokompensation, Übersprechminderung und adaptiver Entzerrung. Die elektrische Schnittstelle zwischen MAC- und PHY-Schichten folgt standardisierten Protokollen, die jeweils für bestimmte Datenraten und Implementierungsanforderungen optimiert sind.

Für Anwendungen, die eine überlegene elektrische Leistung erfordern, bieten unsere FR4 PCB-Lösungen die Grundlage für zuverlässige Ethernet-Implementierungen und gewährleisten gleichzeitig Kosteneffizienz für die Serienproduktion.

Signalintegrität und Impedanzkontrolle für Ethernet-PCBs

Die Signalintegrität stellt die wichtigste technische Herausforderung im Ethernet-PCB-Design dar, insbesondere für Gigabit- und Multi-Gigabit-Implementierungen. Die grundlegende Anforderung besteht darin, eine differenzielle Impedanz von 100 Ohm über den gesamten Signalpfad beizubehalten – von den PHY-Transceiver-Ausgängen über magnetische Schaltungen bis zur RJ-45-Schnittstelle.

Die differenzielle Impedanzkontrolle erfordert eine präzise Steuerung der Leiterbahngeometrie, der dielektrischen Eigenschaften und der elektromagnetischen Feldverteilung. Das Verhältnis zwischen Leiterbahnbreite, Abstand und dielektrischer Höhe bestimmt die charakteristische Impedanz von Differenzialpaaren. Bei typischen FR4-Konstruktionen mit εr = 4,3-4,7 erfordert das Erreichen einer differenziellen Impedanz von 100 Ohm normalerweise Leiterbahnbreiten von 6-8 mils mit einem Abstand von 6-8 mils in Standard-Stapelkonfigurationen.

Kritische Signalintegritätsparameter:

- Impedanzkontrolle: 100Ω ±10% differenzielle Impedanz mit TDR-Verifizierung

- Längenanpassung: Intra-Pair-Skew <50 mils, Inter-Pair-Skew <200 Pikosekunden

- Via-Management: Maximal 2 Via-Übergänge pro Leiterbahn mit kontrollierten Pad-Abmessungen

- Rückpfadkontinuität: Unterbrechungsfreie Referenzebenen unter allen differenziellen Routings

Randkopplungseffekte zwischen differenziellen Leiterbahnpaaren führen zu zusätzlicher Komplexität bei Impedanzberechnungen. Wenn differenzielle Leiterbahnen näher als 30 mils (Kante zu Kante) beabstandet sind, kann die kapazitive Kopplung die effektive differenzielle Impedanz um 5-20 Ohm reduzieren. Dieses Phänomen erfordert eine Kompensation während der Entwurfsphase durch angepasste Leiterbahngeometrie oder modifizierte Abstandsanforderungen.

Fortschrittliche Hochfrequenz-PCB-Materialien bieten überlegene elektrische Leistung für anspruchsvolle Ethernet-Anwendungen. Dielektrika mit geringen Verlusten und stabilen Dielektrizitätskonstanten über Frequenzbereiche ermöglichen eine verbesserte Signalintegrität bei Multi-Gigabit-Datenraten.

Bauteilplatzierung und Layout-Optimierung

Die strategische Platzierung von Komponenten bildet die Grundlage für eine erfolgreiche Ethernet-PCB-Implementierung und beeinflusst direkt die Signalintegrität, elektromagnetische Verträglichkeit und die Fertigungsausbeute. Die räumlichen Beziehungen zwischen PHY-Transceivern, Magnetkreisen und RJ-45-Steckverbindern erfordern eine sorgfältige Optimierung, um eine optimale elektrische Leistung bei gleichzeitiger Einhaltung praktischer Fertigungsbeschränkungen zu erreichen.

Der kritische Abstand zwischen PHY-Transceivern und Magnetkreisen sollte aus Gründen der EMI-Reduzierung mindestens 25 mm (etwa 1 Zoll) betragen. Diese Trennung verringert die Kopplung zwischen hochfrequentem digitalem Schaltrauschen des PHY und der empfindlichen analogen Schaltung innerhalb der magnetischen Isolierungstransformatoren.

Platzierungsrichtlinien:

- PHY zu Magnetics Abstand: Mindestens 25 mm Abstand zur EMI-Reduzierung

- Magnetics zu RJ-45 Abstand: Maximal 25 mm für diskrete Implementierungen

- Digitale Signalisolierung: Mindestens 300 mils Abstand von differenziellen Paaren

- Entkopplungsplatzierung: Innerhalb von 10 mm von PHY-Stromstiften für optimale Wirksamkeit

Die differenzielle Leiterbahnführung zwischen Komponenten erfordert eine parallele Führung mit angepassten Längen und kontrollierten Abständen. Die gesamte Leiterbahnlänge vom PHY zum Stecker sollte 4 Zoll (100 mm) nicht überschreiten, um die Signaldämpfung zu minimieren und akzeptable Signal-Rausch-Verhältnisse zu erhalten. Innerhalb dieser Beschränkung sollten differenzielle Paare eine parallele Führung mit minimalen Abstandsänderungen beibehalten, um die Impedanzkontrolle zu erhalten und die Modenumwandlung zu reduzieren.

Für komplexe Routing-Anforderungen mit Bauteilen mit hoher Pinzahl ermöglicht unsere HDI-PCB-Technologie kompakte Designs mit außergewöhnlicher Routing-Dichte bei gleichzeitiger Einhaltung der Anforderungen an die Signalintegrität.

Masseflächen-Design und EMI-Reduzierung in der Ethernet-PCB-Fertigung

Ein effektives Masseflächen-Design ist in der Ethernet-PCB-Fertigung entscheidend, da es direkt die Signalintegrität, EMI-Unterdrückung und die Einhaltung von Vorschriften beeinflusst. Eine ordnungsgemäße Implementierung stellt sicher, dass hochfrequente differenzielle Signale saubere Rückleitungspfade und eine stabile Leistung beibehalten.

Wichtige Masseflächen-Prinzipien:

- Kontinuierliche Referenzflächen – Bieten eine unterbrechungsfreie Masse unter allen differenziellen Leitungen, um niederohmige Rückleitungspfade zu erhalten.

- Vermeidung von Flächenunterbrechungen – Lücken unter differenziellen Paaren können Rückströme stören und die EMI-Emissionen erhöhen.

- Magnetische Isolationszonen – Halten Sie Masseflächen unter diskreten magnetischen Komponenten frei, um unerwünschte Kopplung zu verhindern.

- Chassis-Masse-Integration – Verwenden Sie eine dedizierte Chassis-Masse für Steckermodule und EMI-Abschirmung.

- Kontrollierte Abschlussbereiche – Halten Sie ausreichende Abstände und Impedanzen in Abschlussbereichen ein. Mehrschichtige Lagenaufbauten ermöglichen die Trennung von funktionalen Massen, während Signallagen eng mit benachbarten Ebenen gekoppelt bleiben, wodurch die Schleifeninduktivität und abgestrahlte Störungen reduziert werden. Die richtige Masseebenenstrategie bei der Ethernet-PCB-Herstellung gewährleistet eine robuste EMI-Leistung, Signalzuverlässigkeit und die Einhaltung von Netzwerkstandards.

Professionelle Ethernet-PCB-Herstellung und Montagedienstleistungen

Bei HILPCB bieten wir fortschrittliche Ethernet-PCB-Herstellung und Montagedienstleistungen an, die Hochfrequenz-Design-Know-how mit präzisen Fertigungsfähigkeiten kombinieren. Unser umfassender Ansatz behandelt die gesamte Signalkette von Bauteilspezifikationen bis hin zur Endmontageprüfung und sichert so eine zuverlässige Leistung für anspruchsvolle Netzwerkanwendungen.

Fertigungsfähigkeiten:

- Impedanzkontrollierte Fertigung: ±5% Toleranz mit statistischer Prozesskontrolle und Testcoupons

- Fortschrittliche Via-Technologie: Lasergebohrte Mikrovias, sequentielle Laminierung und präzise Beschichtung

- Hochfrequenzmaterialien: Rogers-Substrate und verlustarme Dielektrika für überlegene HF-Leistung

- Präzisionsmontage: 0,4-mm-BGA-Platzierung mit ±25µm Genauigkeit und umfassender AOI/ICT-Prüfung

- Qualitätssysteme: ISO 9001:2015 konform mit vollständiger Rückverfolgbarkeit und statistischer Prozesskontrolle

Die impedanzkontrollierte Fertigung stellt eine kritische Fähigkeit für die Ethernet-PCB-Produktion dar. Das Erreichen der erforderlichen 100-Ohm-Differenzialimpedanz erfordert eine präzise Kontrolle der Leiterbahngeometrie, der Dielektrikumsdicke und der Kupferbeschichtungsparameter. Fertigungsprozessvariationen in der Kupferbeschichtungsdicke, der Dielektrizitätskonstante und der Lagenaufbauregistrierung können die endgültigen Impedanzwerte erheblich beeinflussen.

Unsere schlüsselfertigen Montagedienstleistungen bieten komplette Fertigungslösungen von der Prototypenentwicklung bis zur Serienproduktion und gewährleisten gleichbleibende Qualität und Leistung in allen Produktionsphasen.

Die Test- und Validierungsverfahren für Ethernet-PCBs umfassen sowohl DC-elektrische Eigenschaften als auch Hochfrequenzleistungsparameter. Zeitbereichsreflektometrie (TDR)-Tests validieren die Impedanzkontrolle und identifizieren Diskontinuitäten in Hochgeschwindigkeitssignalpfaden. Netzwerkanalysen charakterisieren Einfügedämpfung, Rückflussdämpfung und Übersprechleistung über die für spezifische Ethernet-Standards relevanten Frequenzbereiche.

Häufig gestellte Fragen zum Ethernet-PCB-Design

F: Was unterscheidet das Ethernet-PCB-Design von Standard-Digital-PCBs? A: Das Ethernet-PCB-Design erfordert eine präzise 100-Ohm-Differenzialimpedanzsteuerung, spezielle magnetische Isolationsschaltungen, fortschrittliche EMI-Minderungstechniken und eine sorgfältige Bauteilplatzierung, um die Signalintegrität bei Gigabit-Geschwindigkeiten zu gewährleisten. Die analoge Natur der PHY-zu-Magnetics-Schnittstelle erfordert eine überlegene Rauschkontrolle und Rückpfadmanagement.

Q: Welche Substratmaterialien werden für Hochgeschwindigkeits-Ethernet-Anwendungen empfohlen?

A: Für 10GBASE-T und höhere Geschwindigkeiten bieten verlustarme Materialien wie Rogers RO4350B optimale Leistung. Standard-FR4 hoher Qualität eignet sich für 1000BASE-T-Anwendungen, während 2.5GBASE-T und 5GBASE-T je nach Implementierungsanforderungen und Kostenbeschränkungen von mittelverlusten Substraten profitieren können.

Q: Wie stellen Sie sicher, dass die Ethernet-PCB-Leistung IEEE-Standards entspricht?

A: Wir führen umfassende Tests durch, einschließlich TDR-Impedanzverifikation, S-Parameter-Messungen für Einfüge-/Rückflussdämpfung, Übersprechanalyse und EMC-Vorabkonformitätstests. Unsere Fertigungsprozesse halten die statistische Prozesskontrolle mit Impedanztestmustern und vollständigen elektrischen Testprotokollen ein.

Q: Was sind die kritischen Abstandsanforderungen für das Ethernet-PCB-Layout?

A: Wichtige Abstandsanforderungen umfassen: Mindestabstand von 25 mm zwischen PHY und Magnetics, maximal 25 mm zwischen Magnetics und RJ-45 bei diskreten Implementierungen, Mindestabstand von 300 mils zwischen Differenzialpaar und digitalen Signalen sowie eine Längenanpassung innerhalb von 50 mils für optimale Signalintegrität.

Q: Können Sie sowohl Prototypen- als auch Produktionsanforderungen für Ethernet-PCBs unterstützen?

A: Ja, wir bieten komplette Ethernet-PCB-Dienstleistungen von der anfänglichen Designberatung bis zur Hochvolumenproduktion. Unsere Fähigkeiten umfassen Impedanzmodellierung, Designoptimierung, Prototypenfertigung, Präzisionsmontage, umfassende Tests sowie kontinuierliche Produktionsunterstützung mit vollständiger Qualitätsdokumentation und Rückverfolgbarkeitssystemen.