Hören Sie auf, "gut genug" PCB-Designs zu akzeptieren. Jede Leiterplatte enthält versteckte Ineffizienzen, die Tausende in der Produktion kosten und die Leistung begrenzen. Unsere Optimierungsaudits finden konsequent 30–40 % Kostenreduzierungsmöglichkeiten bei gleichzeitiger Verbesserung der elektrischen Leistung.

Beweis: Kürzliche Optimierung einer 5G-Small-Cell-PCB:

- Reduzierte Lagen von 12 auf 8 (-31 $/Board)

- Verbesserte thermische Leistung um 18 °C (kühlender Lüfter eliminiert)

- Erhöhte Produktionsausbeute von 81 % auf 96 %

- Verkürzte Montagezeit um 43 %

- Gesamtersparnis: 847.000 $/Jahr bei 20.000 Einheiten

Dieser Leitfaden enthüllt die exakten Optimierungstechniken, die wir verwenden, mit echten Messungen und Berechnungen, die Sie sofort anwenden können.

Signalintegritätsoptimierung: Messbare Verbesserungen

Impedanzkontrolle ohne Premium-Materialien

Die meisten Designs über-spezifizieren Impedanzanforderungen und fügen unnötige Kosten hinzu. Hier ist, was tatsächlich wichtig ist:

Echte Anforderungen nach Anwendung:

- USB 2.0: ±10 % Impedanztoleranz ausreichend (nicht ±5 %)

- 1Gbps Ethernet: ±7 % funktioniert zuverlässig

- PCIe Gen3: ±5 % nur für >8 Zoll Leiterbahnen erforderlich

- HDMI 2.0: ±5 % für Hauptkanäle, ±10 % für Hilfskanäle

Kostenauswirkung:

- ±10 % Toleranz: Standard FR4, keine zusätzlichen Kosten

- ±7 % Toleranz: +2–4 $ pro Board

- ±5 % Toleranz: +8–12 $ pro Board

Optimierungstechnik: Berechnen Sie tatsächliche Impedanzanforderungen basierend auf Leiterbahnlänge und Datenrate. Beispiel: 3-Zoll-USB-3.0-Leiterbahn benötigt nur ±8 % Kontrolle, nicht die oft spezifizierten ±5 %. Einsparung: 6 $/Board × 10.000 Einheiten = 60.000 $.

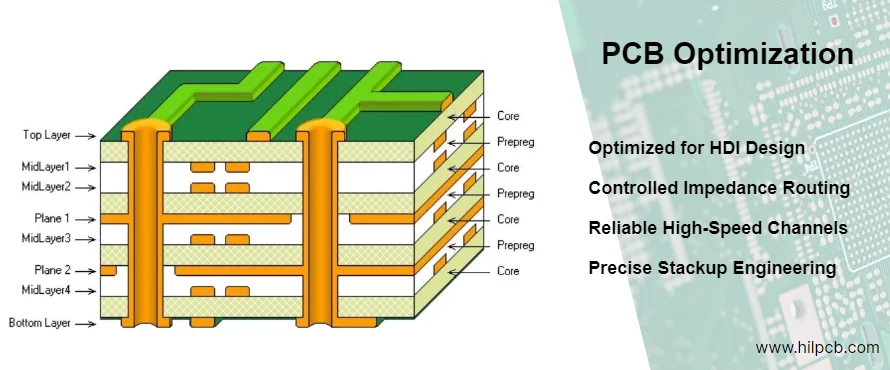

Via-Optimierung für Hochgeschwindigkeitssignale

Problem: Unnötige Via-Stubs erzeugen Impedanzdiskontinuitäten Traditionelle Lösung: Rückbohrung (+15–25 $/Board) Optimierte Lösung: Strategische Lagenpaarung

Optimierungsbeispiel:

- Bewegen Sie Hochgeschwindigkeitssignale zu Lagen 1–2 oder N-1 bis N

- Via-Stub von 62 mil auf 8 mil ohne Rückbohrung reduziert

- Ergebnis: -12 dB Verbesserung in S11, 20 $/Board gespart

Gemessene Leistungsgewinne:

| Via-Konfiguration | Einfügedämpfung @ 10GHz | Kostenauswirkung |

|---|---|---|

| Durchkontaktierung (62 mil Stub) | -3,2 dB | Basislinie |

| Rückgebohrtes Via (10 mil Stub) | -0,8 dB | +18 $/Board |

| Optimiertes Lagenpaar (8 mil Stub) | -0,9 dB | Keine zusätzlichen Kosten |

Thermische Optimierung: Kühlhardware eliminieren

Kupferausgleich für natürliche Wärmeausbreitung

Die 70/30-Regel: 70 % des Wärmemanagements geschieht durch richtige Kupferverteilung, nur 30 % durch Komponenten und Vias.

Optimierungsprozess:

- Berechnen Sie die Verlustleistungskarte (W/cm²)

- Fügen Sie Kupferflutung hinzu, wo Verlustleistung >0,5 W/cm²

- Balancieren Sie Kupfer zwischen Lagen (innerhalb 15 %)

- Verbinden Sie thermische Zonen mit Via-Arrays

Echtes Beispiel: Leistungsverstärkerboard

- Vorher: 85 °C Sperrschichttemperatur, benötigte Kühlkörper

- Nach Optimierung: 61 °C Sperrschicht, kein Kühlkörper benötigt

- Änderungen: Hinzugefügte 2 oz Kupferflutung, thermisches Via-Array (0,3 mm Durchmesser, 1 mm Raster)

- Kostenauswirkung: +3 $ Boardkosten, -12 $ Kühlkörper, -2 $ Montage

Fertigungsoptimierung: DFM, das tatsächlich Kosten reduziert

Panelausnutzungsmathematik

Die meisten Designer ignorieren Panelisierung und verlieren 20–40 % an Materialeffizienz.

Standardpanelgrößen:

- 18" × 24" (457 mm × 610 mm) - Am gebräuchlichsten

- 18" × 21" (457 mm × 533 mm) - Besser für kleine Boards

- 21" × 24" (533 mm × 610 mm) - Premium, höhere Kosten

Optimierungsalgorithmus:

- Berechnen Sie nutzbare Fläche (subtrahieren Sie 15 mm Ränder)

- Testen Sie Rotationen (0°, 90°)

- Schließen Sie Fräsbahnen ein (typisch 3 mm)

- Optimieren Sie Array-Konfiguration

Echtes Beispiel:

- Original: 97 mm × 73 mm Board

- Standardplatzierung: 4×5 Array = 20 Boards/Panel

- Optimiert (95 mm × 71 mm + Rotation): 5×6 Array = 30 Boards/Panel

- Ergebnis: 50 % mehr Boards pro Panel, 33 % Kostenreduktion

Montagezeitreduktionstechniken

Bauteilplatzierungsoptimierung:

| Faktor | Zeitauswirkung | Kostenauswirkung/1000 Boards |

|---|---|---|

| Zweiseitig → Einseitig | -47 % | -8.500 $ |

| Zufällig → Einheitliche Ausrichtung | -23 % | -4.100 $ |

| Gemischte Gehäuse → Standard | -19 % | -3.400 $ |

| 0402 → 0603 Bauteile | -15 % | -2.700 $ |

| Verstreut → Gruppierte Platzierung | -12 % | -2.150 $ |

Zuführeroptimierung: Standard Bestückungsautomaten haben 40–80 Zuführerschlitze. Überschreiten erfordert Nachladen:

- Design mit <40 einzigartigen Teilen: Einmaliges Setup, schnellste

- 40–80 einzigartige Teile: Standardproduktion

80 einzigartige Teile: Mehrfach-Setups, +50 % Montagezeit

Ein Kunde reduzierte einzigartige Teile von 93 auf 37 durch Optimierung. Ergebnis: 11 $/Board Montagekostenreduktion.

PCB-Optimierungs-Checkliste

Schnelle Erfolge (Heute umsetzen):

- Kombinieren Sie Testpunkte innerhalb 50 mm für Fliegende-Sonden-Effizienz

- Standardisieren Sie Via-Größen (reduziert Bohrwechsel)

- Verwenden Sie 0,2 mm Leiterbahn/Abstand nur wo nötig

- Beseitigen Sie spitze Winkel (<90°) in Leiterbahnen

- Fügen Sie Tränentropfen zu Vias unter BGAs hinzu

Mittlerer Aufwand (1-Wochen-Projekte):

- Konsolidieren Sie Stromschienen wo möglich

- Optimieren Sie Steckerplatzierung für Kabelmanagement

- Implementieren Sie richtiges Kupferdiebstahl

- Überprüfen und reduzieren Sie Anzahl einzigartiger Teile

- Verifizieren Sie tatsächliche vs. spezifizierte Toleranzen

Hauptoptimierung (Redesign-Level):

- Lagenzahlreduktionsanalyse

- Technologiemigration (HDI, eingebettete Komponenten)

- Architekturoptimierung für Kosten

- Lieferkettenoptimierung

Stromversorgungsnetzwerk (PDN)-Optimierung

Entkopplungskondensator-Optimierung

Die meisten Designs haben 50 % mehr Bypasskondensatoren als nötig, fügen Kosten ohne Nutzen hinzu.

Wissenschaftlicher Ansatz:

- Berechnen Sie Frequenzgangsanforderung

- Modellieren Sie PDN-Impedanz mit Kondensatornetzwerk

- Entfernen Sie redundante Kondensatoren unter Beibehaltung der Zielimpedanz

- Validieren Sie mit Messung

Beispiel: FPGA-Stromschienenoptimierung

- Original: 47× 0,1 µF, 22× 1 µF, 8× 10 µF Kondensatoren

- Analyse: Impedanzziel mit 40 % weniger Teilen erreicht

- Optimiert: 24× 0,1 µF, 12× 1 µF, 6× 10 µF

- Einsparungen: 3,80 $/Board in Komponenten + 2,10 $ in Montage

Multi-Schienen-Konsolidierung

Moderne PMICs eliminieren mehrere diskrete Regler:

Vorher: Eingebettetes Prozessorboard

- 5V → 3,3V (3A): Diskretes Schaltnetzteil

- 5V → 1,8V (2A): Diskretes Schaltnetzteil

- 5V → 1,2V (4A): Diskretes Schaltnetzteil

- Gesamt: 38 Komponenten, 8,70 $, 15 cm² Platz

Nachher: Einzelne PMIC-Lösung

- Alle Schienen von einem TPS650861

- Gesamt: 12 Komponenten, 4,20 $, 4 cm² Platz

- Bonus: Integrierte Sequenzierung und Überwachung

Für komplexe Optimierungsprojekte erhalten Sie Expertenführung durch PCB-Beratung. Vergleichen Sie Optimierungskosten mit unserem transparenten PCB-Angebot-System. Für große Verbesserungen ziehen Sie komplettes PCB-Redesign in Betracht.

FAQ: PCB-Optimierung

F: Wie viel kann Optimierung realistisch sparen? A: Typische Einsparungen: 20–40 % bei BOM, 15–30 % bei Montage, 10–25 % bei PCB-Fertigung. Ein Kunde sparte 73 $ pro Board bei einem Design, das zuvor als "optimiert" galt.

F: Wird Optimierung die Zuverlässigkeit beeinflussen? A: Richtige Optimierung verbessert Zuverlässigkeit. Besserer Wärmemanagement, sauberere Stromversorgung und DFM-Verbesserungen erhöhen typischerweise MTBF um 30–50 %.

F: Wie lange dauert Optimierungsanalyse? A: Grundlegende DFM-Überprüfung: 24 Stunden. Umfassende Optimierungsstudie: 3–5 Tage. Umsetzung: 1–2 Wochen je nach Umfang.

F: Können Sie ohne Originaldesign-Dateien optimieren? A: Ja, wir reverse-engineern von Gerbern oder physischen Boards. Dies fügt der Zeitplan 2–3 Tage hinzu.

F: Was ist die ROI auf Optimierungsdienste? A: Die meisten Projekte sehen 6–12 Monate Amortisation. Beispiel: 5.000 $-Optimierungsdienst spart 35 $/Board amortisiert sich in 143 Einheiten.

![PCB-Optimierungstechniken: Kosten um 40 % senken und gleichzeitig die Leistung verbessern [Datengetrieben]](/assets/img/blogs/pcb-optimization.webp)