L'integrità dell'alimentazione nella progettazione PCB ad alta frequenza è diventata fondamentale quanto l'integrità del segnale per garantire le prestazioni del sistema. I moderni sistemi RF e i circuiti digitali ad alta velocità richiedono un'erogazione di potenza pulita e stabile su frequenze da CC a decine di gigahertz. Il rumore dell'alimentatore modula direttamente i segnali RF, provoca jitter nei sistemi digitali e genera interferenze elettromagnetiche che possono causare problemi di conformità normativa. Questa guida completa esplora le tecniche avanzate per la progettazione di solide reti di distribuzione dell'energia (PDN) che soddisfano i severi requisiti delle odierne applicazioni ad alta frequenza.

1. Comprensione dei requisiti di alimentazione nei sistemi ad alta frequenza

I sistemi ad alta frequenza che utilizzano la tecnologia HF PCB devono affrontare sfide impegnative per l'erogazione di potenza. Gli amplificatori di potenza RF possono avere rapporti di corrente picco/media superiori a 10:1, richiedendo un'erogazione rapida di corrente per evitare cali di tensione. I processori che funzionano oltre 1 GHz creano transitori di corrente veloci che richiedono un'impedenza PDN estremamente bassa. A queste velocità, l'integrità dell'alimentazione e l'integrità del segnale sono strettamente collegate: piccole ondulazioni, come 50 mV, possono degradare l'EVM del trasmettitore RF di diversi punti percentuali o introdurre jitter nei collegamenti ad alta velocità, influenzando le prestazioni e l'affidabilità.

Gli effetti termici complicano ulteriormente la progettazione di PCB HF. Gli amplificatori RF a bassa efficienza dissipano la maggior parte della loro potenza sotto forma di calore, creando punti caldi che modificano il comportamento dei componenti. Le variazioni di temperatura possono alterare l'uscita del regolatore, i valori passivi e la polarizzazione dei transistor, rischiando l'instabilità. Un efficace progetto di alimentazione per PCB HF deve gestire sia le prestazioni elettriche che il controllo termico per mantenere un funzionamento costante in condizioni di alta frequenza e carico elevato.

2. Architettura della rete di distribuzione dell'alimentazione (PDN)

Un PDN ben progettato fornisce una bassa impedenza su tutte le frequenze di interesse, mantenendo stabilità ed efficienza. Le moderne architetture PDN impiegano approcci gerarchici con più stadi di regolazione ottimizzati per diverse gamme di frequenza.

Strategia di regolamentazione in più fasi

Lo stadio di regolazione primario converte la tensione di ingresso (tipicamente 12-48 V) in guide intermedie utilizzando regolatori di commutazione ottimizzati per l'efficienza:

Considerazioni sulla progettazione del regolatore a commutazione:

- Frequenza di commutazione: 500 kHz - 2 MHz tipica

- Ondulazione di uscita: <50 mV picco-picco

- Risposta transitoria: tempo di stabilizzazione di <10μs

- Obiettivo di efficienza: >90% a pieno carico

- Gestione EMI: schermatura e filtraggio essenziali

La regolazione secondaria fornisce un'alimentazione pulita per i circuiti sensibili:

Implementazione del regolatore lineare:

- Rumore ultrabasso: <10μV RMS (10 Hz - 100 kHz)

- PSRR: >60dB a 1 MHz

- Tensione di caduta: <200 mV per l'efficienza

- Progettazione termica: è necessario un dissipatore di calore adeguato

La regolazione del punto di carico (POL) posiziona i regolatori adiacenti ai carichi ad alta corrente:

- Riduce al minimo le perdite di distribuzione

- Riduce la caduta di tensione durante i transitori

- Consente l'ottimizzazione indipendente della tensione

- Semplifica il monitoraggio della corrente

Progettazione e ottimizzazione del piano di alimentazione

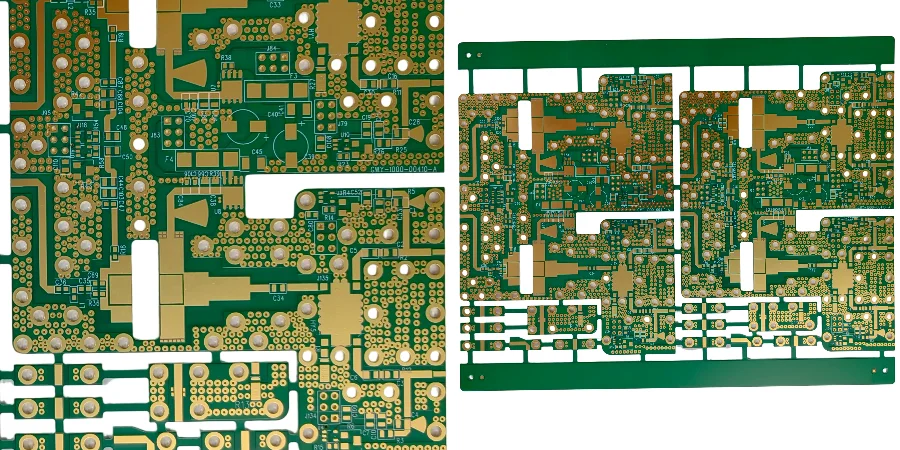

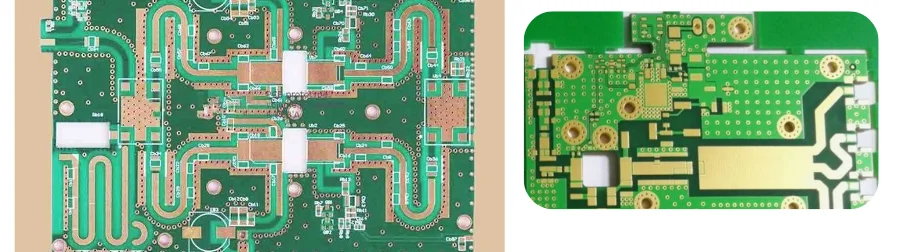

I piani di alimentazione negli stackup [PCB multistrato] (/products/multilayer-pcb) fungono da reti di distribuzione della corrente a bassa induttanza:

Calcolo della capacità piana: C = ε₀ × εr × A / h

Per piani da 100 mm × 100 mm con spaziatura di 0,1 mm su FR4: C = 8,85e-12 × 4,4 × 1e-2 / 1e-4 = 3,9nF

Questa capacità distribuita fornisce un disaccoppiamento ad alta frequenza superiore a 100 MHz, dove i condensatori discreti diventano inefficaci a causa dell'induttanza di montaggio.

Linee guida per la progettazione della coppia di aerei:

- Spaziatura minima di 0,1 mm per una capacità effettiva

- Utilizzare materiali ad alto εr tra i piani, quando possibile

- Evitare fessure e spaccature che aumentano l'induttanza

- Implementare la regola delle 20 ore per ridurre le radiazioni dei bordi

- Aggiungere vie di cucitura ogni λ/20 alla periferia del piano

3. Strategia di disaccoppiamento per applicazioni ad alta frequenza

Un disaccoppiamento efficace richiede un'attenta selezione dei componenti, il posizionamento e la progettazione dell'interconnessione per mantenere una bassa impedenza PDN nell'intero spettro di frequenze.

Selezione e caratterizzazione dei condensatori

I condensatori reali mostrano induttanza e resistenza parassite che limitano l'efficacia delle alte frequenze:

Impedenza vs. frequenza: Z = R + j(ωL - 1/ωC)

Frequenza di autorisonanza (SRF): f_SRF = 1 / (2π√(LC))

Al di sopra della SRF, i condensatori diventano induttivi e l'impedenza aumenta con la frequenza.

Parametri tipici del condensatore:

| Pacchetto | Capacità | ESL | SRF | Portata effettiva |

|---|---|---|---|---|

| Anno 1206 | 10μF | 1,2 nH | 1,5 MHz | CC - 1 MHz |

| 0805 | 1μF | 0,8 nH | 5,6 MHz | 100 kHz - 5 MHz |

| Codice: 0603 | 0,1 μF | 0,6 nH | 20 MHz | 1 MHz - 20 MHz |

| Codice: 0402 | 10nF | 0,4 nH | 80 MHz | 10 MHz - 80 MHz |

| Codice: 0201 | 1nF | 0,3 nH | 290 MHz | 50 MHz - 200 MHz |

Posizionamento e ottimizzazione del layout

Il posizionamento del condensatore influisce in modo critico sull'efficacia del disaccoppiamento:

Tramite l'impatto dell'induttanza: L_via = 0,2h[ln(4h/g) + 1] nH

Per via da 0,3 mm in scheda da 1,6 mm: L_via = 0,2 × 1,6[ln(4×1,6/0,3) + 1] = 1,2nH

Questa induttanza può dominare l'induttanza totale del circuito, annullando i vantaggi dei condensatori a bassa ESL.

Tecniche di ottimizzazione:

- Posizionare i condensatori entro 2 mm dai pin di alimentazione

- Utilizzare più vie per terminale del condensatore

- Implementare via-in-pad per un'induttanza minima

- Instradare l'alimentazione sui livelli adiacenti

- Mantieni la simmetria per la cancellazione differenziale del rumore

4. Gestione del rumore e delle interferenze dell'alimentatore

Il rumore dell'alimentazione degrada le prestazioni del sistema attraverso più meccanismi di accoppiamento. Una gestione efficace del rumore richiede la comprensione delle fonti, dei percorsi di accoppiamento e delle tecniche di mitigazione.

Soppressione del rumore di commutazione

I regolatori di commutazione generano rumore a banda larga con frequenza fondamentale alla velocità di commutazione e armoniche che si estendono fino a centinaia di megahertz:

Design del filtro di ingresso:

- Filtro modalità differenziale: LC passa-basso con f_c < f_sw/10

- Induttanza di modo comune: riduce le emissioni condotte

- Condensatori Y: forniscono il percorso di ritorno per la corrente di modo comune

- Rete di smorzamento: impedisce la risonanza del filtro

Ottimizzazione del filtro di uscita: Il filtraggio LC del secondo stadio raggiunge un'attenuazione aggiuntiva di 40 dB/decade:

L = V_out × D × (1-D) / (ΔI × f_sw) C = ΔI / (8 × f_sw × ΔV)

Per uscita a 3,3 V, carico 1 A, commutazione a 1 MHz: L = 2,2 μH, C = 22 μF per ripple di 50 mV

Tecniche di isolamento

I circuiti analogici e RF sensibili richiedono l'isolamento dal rumore digitale:

Separazione fisica:

- Mantieni una spaziatura di >5 mm tra i domini

- Utilizzare piani di alimentazione separati, ove possibile

- Instradamento dei segnali sensibili lontano dai nodi di commutazione

- Implementare anelli di protezione attorno ai circuiti critici

Filtraggio e disaccoppiamento:

- Manicotti di ferrite: 100Ω @ 100 MHz tipico

- Filtri Pi: attenuazione >40dB sopra il cutoff

- Condensatori passanti: eccellenti prestazioni ad alta frequenza

- Filtri attivi: per requisiti di rumorosità estremamente bassi

Gestione del piano di massa

Una corretta messa a terra impedisce l'accoppiamento del rumore mantenendo l'integrità del segnale:

Architettura di messa a terra a stella:

- Connessione a punto singolo tra domini

- Riduce al minimo i loop di massa

- Riduce l'accoppiamento a impedenza comune

- Adatto per sistemi a segnale misto

Messa a terra multipunto:

- Richiesto per frequenze >1 MHz

- Fornisce percorsi di ritorno a bassa impedenza

- Utilizza il piano di massa per la schermatura

- Implementa tramite cucitura per collegamenti aerei

5. Considerazioni termiche nei progetti RF ad alta potenza

La gestione termica influisce direttamente sull'efficacia della progettazione dell'alimentazione, in particolare per gli amplificatori di potenza RF e i circuiti digitali ad alta corrente.

Analisi della dissipazione di potenza

Calcola la dissipazione di potenza totale includendo tutte le fonti:

Amplificatore di potenza RF: P_dissipated = P_DC - P_RF = P_DC × (1 - η)

Per un'uscita di 10 W con un'efficienza del 40%: P_DC = 25 W, P_dissipated = 15 W

Regolatore di tensione: P_dissipated = (V_in - V_out) × I_out + I_q × V_in

Per la conversione da 5 V a 3,3 V a 2 A: P_dissipated = 1,7 × 2 + 0,005 × 5 = 3,4 W

Calcoli della resistenza termica

La temperatura di giunzione determina l'affidabilità e le prestazioni:

T_j = T_a + P × (R_jc + R_cs + R_sa)

Dove:

- R_jc: Giunzione a cassa (dalla scheda tecnica)

- R_cs: Custodia a lavello (materiale di interfaccia)

- R_sa: Sink-to-ambient (dissipatore di calore)

L'obiettivo T_j < 125 °C per il commercio < 110 °C per l'alta affidabilità.

Progettazione termica PCB

Il PCB stesso fornisce una significativa dissipazione del calore:

Array termici via:

- Diametro della via: 0,3-0,5 mm tipico

- Spaziatura: griglia da 1,0-1,5 mm

- Resistenza termica: ~50°C/W per via

- Riempimento con materiale termicamente conduttivo

Diffusione del rame:

- 1 oncia di rame: 70°C/W per quadrato

- 2 once di rame: 35°C/W per quadrato

- Utilizzare l'area di rame massima disponibile

- Collegamento ai piani interni per la diffusione

6. Perché scegliere HILPCB per la progettazione di potenza ad alta frequenza

HILPCB fornisce soluzioni complete per la progettazione di potenza per applicazioni ad alta frequenza impegnative:

- Competenza di progettazione: modellazione e ottimizzazione PDN per DC a 40 GHz

- Strumenti di simulazione: analisi dell'integrità dell'alimentazione utilizzando software standard del settore

- Capacità di produzione: rame pesante fino a 6 once, funzioni di gestione termica

- Selezione del materiale: Substrati termicamente conduttivi a bassa perdita

- Servizi di test: Misurazione dell'impedenza PDN, imaging termico

- Esperienza applicativa: amplificatori RF, PCB ad alta velocità, convertitori di potenza

I nostri servizi di progettazione dell'alimentazione hanno consentito:

- Stazioni base 5G con uscita RF da 100 W+

- Server ad alta velocità con impedenza PDN inferiore a 1 mΩ

- Radar per il settore automobilistico con funzionamento da -40 °C a +150 °C

- Comunicazioni satellitari con efficienza del >95%

- Apparecchiatura di prova con rumore RMS di <1μV

7. Domande frequenti (FAQ)

Q1: Di quanta capacità di disaccoppiamento ho bisogno per il mio progetto ad alta frequenza? A: L'impedenza PDN target determina i requisiti di capacità. Per i circuiti digitali, utilizzare 0,1 μF per pin di alimentazione più una capacità di massa di 10-100 μF per ampere di corrente. Per RF, aggiungere condensatori da 1-10 nF vicino ai dispositivi attivi. Utilizzare gli strumenti di analisi PDN per ottenere valori precisi.

Q2: Devo usare manicotti di ferrite negli alimentatori ad alta frequenza? R: I manicotti di ferrite filtrano efficacemente il rumore superiore a 10 MHz, ma aggiungono resistenza CC e possono causare instabilità con transitori di carico rapidi. Utilizzarli per isolare sezioni analogiche/RF, ma evitarli nei percorsi di alimentazione digitale ad alta corrente. Verificare sempre la stabilità con le perline installate.

Q3: Come posso prevenire le risonanze del piano di alimentazione? R: Le risonanze del piano di potenza si verificano a frequenze in cui le dimensioni del piano sono multipli uguali a λ/2. La mitigazione include: l'utilizzo di materiali dielettrici con perdita, l'aggiunta di disaccoppiamento distribuito, la segmentazione di piani di grandi dimensioni e l'implementazione della terminazione del bordo. Target prima risonanza al di sopra della frequenza operativa.

Q4: Qual è l'impatto dell'induttanza via sull'efficacia del disaccoppiamento? R: L'induttanza via (tipicamente 0,5-1,5 nH) può dominare l'induttanza totale di montaggio, limitando l'efficacia delle alte frequenze. Riduci al minimo utilizzando più vie (l'induttanza si riduce di 1/n), vie più corte (schede più sottili) e vie di diametro maggiore. Prendi in considerazione il via-in-pad per le applicazioni critiche.

Q5: Come si progetta la distribuzione dell'alimentazione per un radar automobilistico a 77 GHz? R: A 77 GHz, domina il disaccoppiamento on-die. Concentrati sulla fornitura di una CC pulita con un eccellente filtraggio delle basse frequenze (<100 MHz). Utilizza LDO dedicati per ogni blocco RF, implementa la distribuzione a stella per ridurre al minimo l'accoppiamento e mantiene l'impedenza di transizione die-to-board al di sotto di 50 mΩ.

Q6: Quali sono le cause dell'oscillazione del regolatore di tensione nelle applicazioni RF? R: L'accoppiamento RF nelle reti di feedback provoca oscillazione. La prevenzione include: schermatura dei nodi sensibili, utilizzo di condensatori feedforward per il margine di fase, instradamento delle tracce di feedback lontano dalla RF e aggiunta di perline di ferrite sulle linee di rilevamento. Verificare sempre la stabilità in condizioni di temperatura e carico.

Pronto a ottimizzare il tuo progetto di alimentazione ad alta frequenza?

I nostri esperti di integrità dell'alimentazione forniscono progettazione e analisi PDN complete per le applicazioni RF e ad alta velocità più esigenti. Contattaci per una consulenza sul tuo prossimo progetto.