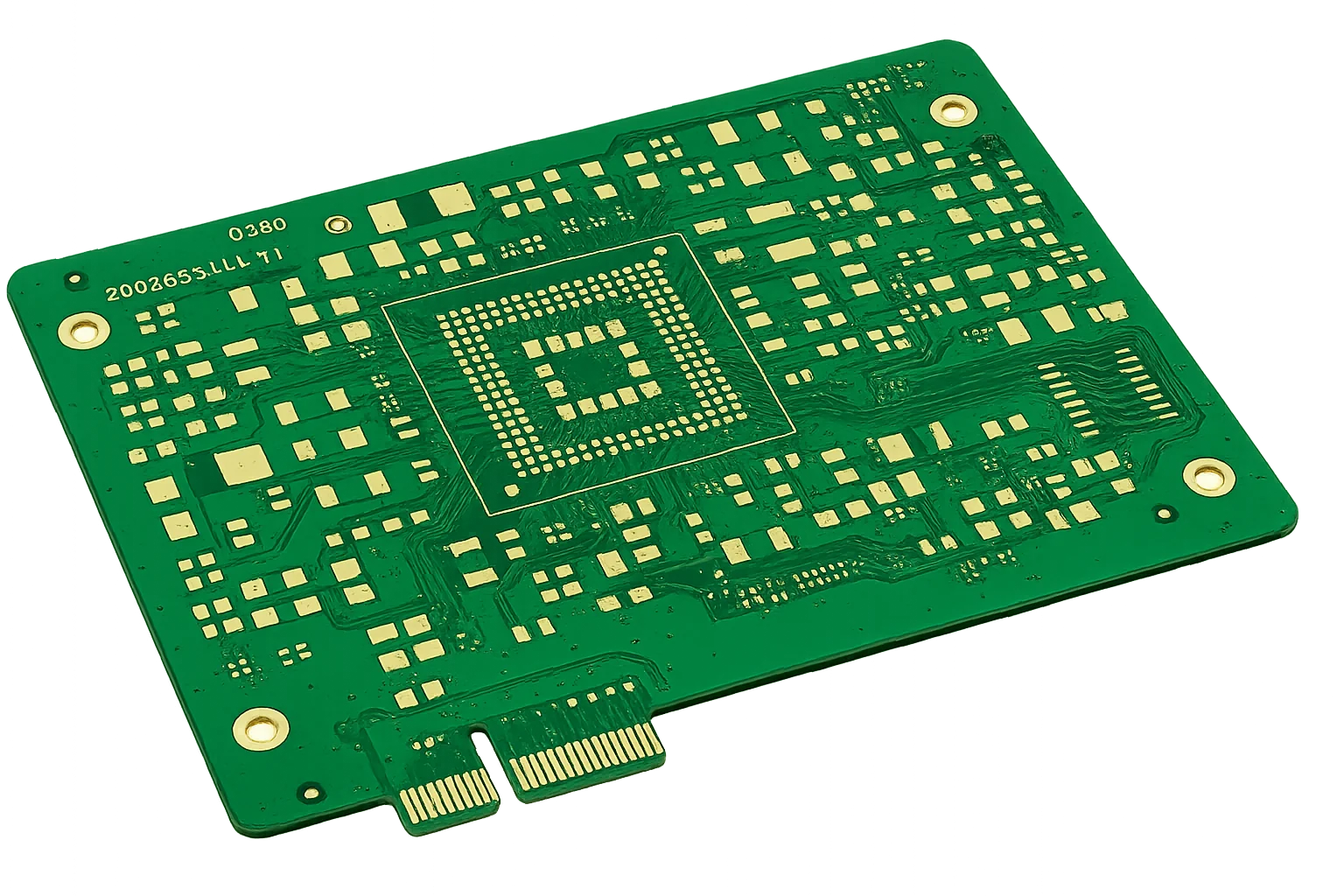

Produzione di PCB HDI | Microvia da 50–75 μm, Any-Layer, VIPPO | IATF 16949

PCB a interconnessione ad alta densità (HDI) con microvia laser da 50–75 μm (cinquanta a settantacinque micrometri), architetture da 1+N+1 a any-layer, via-in-pad placcato (VIPPO) e stackup a bassa perdita per 10–56 Gbps (dieci a cinquantasei gigabit al secondo). Controllo dell'impedenza ±5% (più/meno cinque percento) con validazione TDR. Tempi rapidi di 7 giorni (sette giorni) disponibili.

Selezione della tecnologia HDI e ingegneria del valore

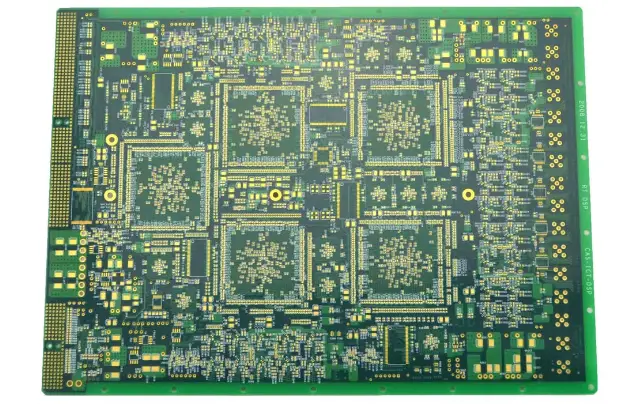

Architettura di stack-up per bilanciare densità e prestazioniL'adozione dell'HDI inizia quando il passo del BGA scende sotto 0.8 mm (zero punto otto millimetri) o il numero di strati supera i limiti economici. Valutiamo tre nodi decisionali: altezza dello stack di microvia (tipicamente limitata a due per affidabilità), cicli di laminazione sequenziale (1+N+1 vs 2+N+2 costo/beneficio) e transizioni di materiale quando le frequenze operative superano 5–8 GHz (cinque a otto gigahertz). Attraverso una sistematica ottimizzazione dello stack-up, lo spessore totale è comunemente ridotto del 25–40% (venticinque a quaranta percento) mantenendo l'affidabilità IPC-6012 Classe 3.

Le microvia laser di 50–75 μm (cinquanta a settantacinque micrometri) con rapporto d'aspetto ≤1:1 (minore o uguale a uno a uno) abilitano il fanout via-in-pad, riducendo l'induttanza parassita di ~40–60% (circa quaranta a sessanta percento) rispetto al routing a osso di cane. Per coppie differenziali >10–12 Gbps (maggiore di dieci a dodici gigabit al secondo), interconnessioni più corte preservano i margini dell'occhio e riducono lo skew del segnale. Per dettagli su progettazione delle via e correlazione dei test, consulta la nostra guida al controllo dell'impedenza e lo studio sull'affidabilità delle microvia.

Rischio critico: Un eccessivo stacking di microvia, un riempimento di resina insufficiente o una laminazione squilibrata possono causare vuoti, crepe nel barilato e formazione di filamenti anodici conduttivi (CAF) durante lo stress termico. Sovraperforazioni o rapporti d'aspetto elevati aumentano anche il rischio di fallimento nell'interfaccia via-cattura.

La nostra soluzione: Applichiamo gli standard di affidabilità delle microvia IPC-6016 e IPC-6012 Classe 3. Ogni struttura di build-up è simulata per l'espansione sull'asse z, riempita e planarizzata utilizzando placcatura in rame assistita da vuoto. L'analisi delle sezioni trasversali e i test di stress delle interconnessioni (IST) confermano l'integrità delle via impilate e un CPK di placcatura ≥ 1.33 (maggiore o uguale a uno punto tre tre). Per design ultra-densi, gli stack-up ibridi combinano PCB multistrato e PCB backplane per bilanciare routing e distribuzione di potenza.

- Diametro microvia: 50–75 μm (cinquanta a settantacinque micrometri), rapporto d'aspetto ≤1:1 (minore o uguale a uno a uno)

- Laminazione sequenziale: 1+N+1 fino a configurazioni any-layer

- VIPPO con profondità dell'avvallamento <10% (minore del dieci percento) dello spessore del pad

- Controllo dello skew delle coppie differenziali a ±5 ps (più/meno cinque picosecondi) in layout ottimizzati

- Stack-up ibridi con Df basso 0.005–0.012 (zero punto zero zero cinque a zero punto zero uno due) sugli strati critici

- Controllo della deformazione ≤0.7% (minore o uguale a zero punto sette percento) per BGA grandi

🚀 Richiesta Preventivo Rapido

📋 Ottieni Capacità Complete

Controllo e Validazione del Processo di Costruzione Sequenziale

Precisione di registrazione attraverso verifica di allineamento multi-faseCostruzioni multi-ciclo mantengono la registrazione degli strati entro ±25–50 μm (più/minus venticinque a cinquanta micrometri). UV-YAG a 355 nm (trecentocinquantacinque nanometri) fornisce un'ablazione uniforme su sistemi FR-4 high-Tg (170–180 °C — centosettanta a centottanta gradi Celsius) e a bassa perdita. La densità energetica è regolata in base a Dk/Df per prevenire la carbonizzazione e preservare pareti laterali pulite per la metallizzazione.

Il riempimento in rame è selezionato in base all'affidabilità: rame elettrolitico per profili termici automobilistici (−40 °C↔+125 °C — meno quaranta a più centoventicinque) e pasta conduttiva per costruzioni consumer ottimizzate per il costo. La ingegneria CAM pre-produzione applica l'analisi FEA per prevedere lo stress da CTE al ginocchio del microvia. La stabilità dimensionale è verificata otticamente in cinque posizioni per pannello secondo IPC-2226 Livello C.

- Laser CO₂ e UV con precisione del fascio ±10 μm (più/minus dieci micrometri)

- Uniformità dello strato di semina senza elettrodi ±10% (più/minus dieci percento)

- Controllo di allineamento a raggi X di microvia sovrapposti a risoluzione di 5 μm (cinque micrometri)

- IST secondo IPC-TM-650 2.6.26 (test di stress interconnessione) qualificato

Matrice di capacità e prestazioni HDI PCB

Finestre di processo ottimizzate per l'equilibrio affidabilità-costo

| Parametro | Capacità standard | Capacità avanzata | Standard |

|---|---|---|---|

Layer Count | 4–30 strati (da quattro a trenta) | Fino a 60+ strati (fino a sessanta più, any-layer) | IPC-2226 |

Base Materials | FR-4 High-Tg, materiali low-Dk/Df | Megtron 6/7, Isola I-Speed, Rogers RO4000 | IPC-4101 |

Board Thickness | 0.4–3.2 mm (zero punto quattro a tre punto due) | 0.2–6.0 mm (zero punto due a sei punto zero) | IPC-A-600 |

Min Trace/Space | 75/75 μm (3/3 mil; settantacinque per settantacinque micrometri) | 50/50 μm (2/2 mil; cinquanta per cinquanta micrometri) | IPC-2221 |

Min Hole Size (Laser) | 0.10 mm (4 mil; zero punto uno zero millimetri) | 0.05 mm (2 mil; zero punto zero cinque millimetri) | IPC-2226 |

Via Technology | Blind/Buried, Microvias (1+N+1, 2+N+2) | Stacked/Staggered, VIPPO, Any-Layer | IPC-6012 |

Aspect Ratio (Microvia) | 0.8:1 (zero punto otto a uno) | 1:1 (uno a uno) | IPC-2226 |

Max Panel Size | 500 × 400 mm (cinquecento per quattrocento millimetri) | 600 × 500 mm (seicento per cinquecento millimetri) | Manufacturing capability |

Impedance Control | ±10% (più/meno dieci percento) | ±5% (più/meno cinque percento) con TDR | IPC-2141 |

Surface Finish | HASL, ENIG, OSP, Immersion Silver | ENEPIG, Soft/Hard Gold, Selective OSP | IPC-4552/4556 |

Quality Testing | E-test, AOI, X-ray | 4-wire Kelvin, Cross-section, IST, HAST | IPC-9252 |

Certifications | ISO 9001, UL, RoHS | IATF 16949, ISO 13485, AS9100, MIL-PRF-31032 | Industry standards |

Lead Time | 7–15 giorni (da sette a quindici giorni) | 24 ore (ventiquattro ore) prototipo quick-turn | Production schedule |

Pronto a iniziare il tuo progetto PCB?

Che tu abbia bisogno di semplici prototipi o di produzioni complesse, le nostre capacità di produzione avanzate garantiscono qualità superiore e affidabilità. Ottieni il tuo preventivo in soli 30 minuti.

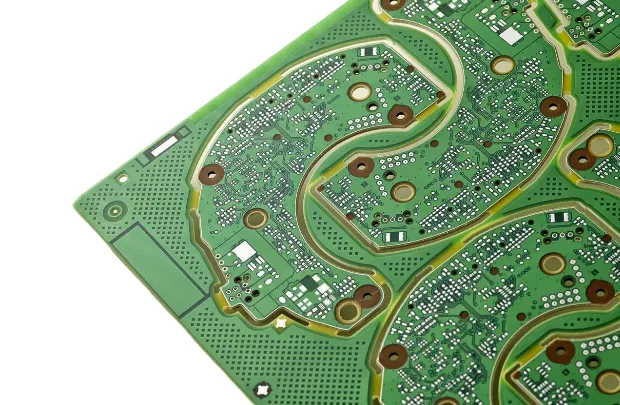

Architettura dello Stack-Up e Integrazione del Sistema Materiali

La progressione da 1+N+1 a 2+N+2 avviene tipicamente quando i BGA con passo 0,8 mm (zero virgola otto millimetri) superano i 400–600 pin. Modelliamo la risonanza degli stub delle vie intorno a 0,25λ (un quarto di lunghezza d'onda) vicino a 10 GHz (dieci gigahertz) e spostiamo le reti critiche su percorsi ciechi/back-drilled. Le transizioni a bassa perdita (Df 0,009–0,012) sono giustificate quando il budget di perdita di inserzione scende sotto ~0,8–1,0 dB/in (circa zero virgola otto a uno virgola zero decibel per pollice). Vedi produzione HDI e ottimizzazione delle vie cieche.

L'affidabilità delle microvie impilate dipende da un rame uniforme attraverso la placcatura sequenziale. Miriamo a ≥18–20 μm (maggiore o uguale a diciotto-venti micrometri) nel barile, verificato tramite sezione trasversale. Le pile sfalsate migliorano la vita a ciclo termico del 20–30% (venti-trenta percento) ma richiedono più area. Il CTE del riempimento VIPPO è regolato (≈45–55 ppm/°C — circa quarantacinque-cinquantacinque parti per milione per grado Celsius) per limitare lo stress delle giunzioni di saldatura; il riempimento in rame è selezionato quando la dissipazione del calore per via supera ~2 W (circa due watt).

Ottimizzazione della Sequenza di Costruzione e Finestre di Processo

La preparazione del nucleo mira a un restringimento <0,05% (inferiore a zero virgola zero cinque percento). Ogni ciclo SBU: laminazione 175–190 °C (centosettantacinque-centonovanta gradi Celsius), formazione di vie laser con pareti laterali di 70–80° (settanta-ottanta gradi), quindi rame chimico + elettrolitico. Il desmear utilizza permanganato regolato per minimizzare la recessione dielettrica rimuovendo completamente lo smear. Il Cpk del processo per l'anello di anulus e la spaziatura delle vie è mantenuto ≥1,33 (maggiore o uguale a uno virgola tre tre). La placcatura a impulsi inversi raggiunge un potere di lancio >80% (maggiore di ottanta percento). Dettagli nella nostra guida HDI.

Il QA post-laminazione include AOI fino a 10 μm (dieci micrometri), tomografia a raggi X per il neck-down delle microvie e test elettrici (flying-probe/fixture). Il Kelvin a 4 fili verifica la resistenza a ±1 mΩ (più/meno un milliohm) per il rilevamento di interconnessioni marginali.

Prestazioni ad Alta Velocità con Impedenza Controllata

La riduzione degli stub delle vie e l'accoppiamento stretto dei piani migliorano la perdita di ritorno. Per coppie differenziali >10 Gbps (maggiore di dieci gigabit al secondo), utilizziamo architetture cieche/back-drilled per eliminare gli stub risonanti. La selezione dei materiali passa a ultra-bassa perdita (Df 0,005–0,007) quando il prodotto dB/in-GHz si avvicina ai limiti. Il nostro modellamento dell'impedanza utilizza EM 3D per array di vie e transizioni, raggiungendo una tolleranza di produzione di ±5% (più/meno cinque percento) con correlazione dei coupon. Il rame a basso profilo (Rz <2 μm — inferiore a due micrometri) riduce la perdita del conduttore del 15–20% (quindici-venti percento). Dielettrici di costruzione sottili (50–75 μm) consentono un'inductance di loop PDN inferiore a 100 pH (cento picohenry).

Validazione dell'affidabilità: Termico, Umidità e IST

Cicli termici da −40 °C a +125 °C (meno quaranta a più centoventicinque) con soste di 15 minuti mirano a ≥1000 (maggiore o uguale a mille) cicli senza una variazione di resistenza >10% (maggiore del dieci percento). L'IST induce riscaldamento Joule per rilevare guasti incipienti (>500 cicli tipici a 150 °C — centocinquanta gradi Celsius). HAST 130 °C/85% RH (centotrenta gradi Celsius/ottantacinque percento di umidità relativa) per 96 h (novantasei ore) valuta la resistenza all'umidità.

Le sezioni SEM controllano la grana del rame, l'adesione e i vuoti; l'accettazione IPC-A-600 Classe 3 include una placcatura di avvolgimento ≥5 μm (maggiore o uguale a cinque micrometri) e nessuna crepa al ginocchio. Pulizia ionica ≤1.56 μg/cm² equivalente NaCl (minore o uguale a uno punto cinque sei microgrammi per centimetro quadrato). Test CAF a 65 °C/88% RH (sessantacinque gradi Celsius/ottantotto percento di umidità relativa) con 100 VDC (cento volt DC) per ≥500 h (maggiore o uguale a cinquecento ore).

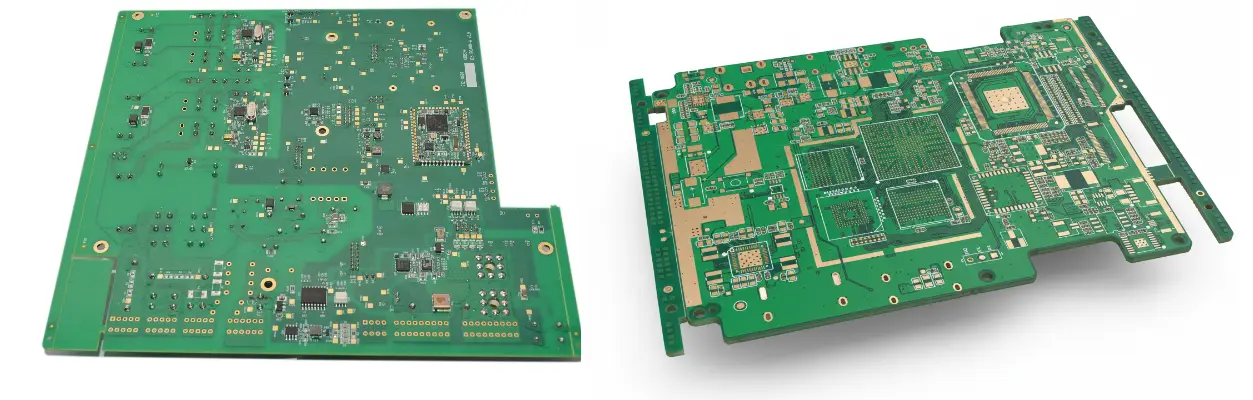

Strategie HDI Specifiche per Applicazioni

Automotive ADAS: 2+N+2 con strati RF selettivi a bassa perdita, perdita di inserzione <0.3 dB/in (minore di zero punto tre decibel per pollice) a 77 GHz (settantasette gigahertz), vie termiche riempite di rame che forniscono θJB <2 °C/W (minore di due gradi Celsius per watt).

Medico: miniaturizzazione any-layer con documentazione ISO 13485.

Datacom/5G: 25–56 Gbps (venticinque a cinquantasei gigabit al secondo) SERDES; vedi tecnologia PCB 5G.

Consumer: HDI selettivo solo dove richiesto dalla densità, riducendo i costi del 15–25% (quindici a venticinque percento).

Garanzia Ingegneristica e Certificazioni

Esperienza: programmi collaudati in produzione da 1+N+1 a any-layer con laminazione a zone controllate e registrazione LDI.

Competenza: TDR/VNA per modelli di transizione delle vie; SPC su placcatura e registrazione delle perforazioni; obiettivi Cpk ≥1.33 (maggiore o uguale a uno punto tre tre).

Autorevolezza: IPC Classe 3, IATF 16949, ISO 13485, AS9100; audit e documentazione end-to-end.

Affidabilità: MES traccia codici di lotto e serializzazione ai dati di test in linea; report IST/HAST disponibili per la qualificazione.

- Controlli di processo: spessore di placcatura, pressione/temperatura di laminazione, energia laser

- Tracciabilità: serializzazione delle unità, tracciamento dei lotti dei componenti, itinerario digitale

- Validazione: IST, HAST, revisioni microsezioni, coupon di impedenza

Domande frequenti

How do I choose between 1+N+1 and 2+N+2 HDI?

What limits stacked microvia reliability and how to mitigate?

When should I move to low-loss or ultra-low-loss materials?

Which factors drive HDI pricing the most?

Can you validate impedance to tight tolerances on HDI?

Sperimenta l'Eccellenza Manifatturiera

Processi di produzione avanzati garantiscono che ogni PCB soddisfi i più alti standard di qualità. Ottieni subito il tuo preventivo personalizzato.