Die Signalintegrität entscheidet über Erfolg oder Misserfolg in Hochfrequenz-PCB-Designs. Da die Datenraten 25 Gbit/s überschreiten und die Frequenzen über 40 GHz hinausgehen, erfordert die Aufrechterhaltung sauberer Signale systematische Ansätze für Design, Analyse und Validierung. Dieser Leitfaden bietet praktische Lösungen, um eine überragende Signalintegrität in anspruchsvollen Anwendungen zu erreichen.

Was ist Signalintegrität und warum ist sie beim Design von HF-Leiterplatten von entscheidender Bedeutung?

Die Signalintegrität bezieht sich auf die Qualität elektrischer Signale, während sie durch eine Leiterplatte fließen, und ist besonders kritisch bei der Konstruktion von HF-Leiterplatten (Hochfrequenz-Leiterplatten). Wenn die Signalfrequenzen zunehmen, bedeutet die Aufrechterhaltung der Signalintegrität, dass wichtige Parameter wie Amplitude, Timing und Wellenform erhalten bleiben. Eine Verzerrung dieser Parameter kann zu einer erheblichen Verschlechterung des Signals führen, insbesondere bei hohen Frequenzen, bei denen selbst kleinere Probleme zu Datenfehlern führen können.

Zu den wichtigsten Metriken für die Bewertung der Signalintegrität in HF-Leiterplatten gehören die Augenhöhe (die vertikale Öffnung für Bitentscheidungen, typischerweise >100 mV), die Augenbreite (der Timing-Spielraum, typischerweise >0,6 UI) und Jitter (Timing-Variationen, typischerweise <0,3 UI für die meisten Systeme). Auch die Bitfehlerrate (BER) ist mit einem Ziel von <10^-12 eine wichtige Maßnahme, die sicherstellt, dass das System Daten zuverlässig und fehlerfrei übertragen kann.

Mit zunehmender Frequenz steigen auch die Herausforderungen bei der Aufrechterhaltung der Signalintegrität. Bei HF-Leiterplatten, die mit 1-5 GHz betrieben werden, sind die Impedanzkontrolle und die Minimierung des Übersprechens mit einem Zielwert von >15 dB für die Rückflussdämpfung von entscheidender Bedeutung. Bei 5-20 GHz verlagert sich der Fokus auf die Minimierung von Verlusten und die Optimierung über Übergänge mit einer Einfügedämpfung von weniger als 3 dB. Bei 20-40 GHz wird die Oberflächenrauheit kritisch und erfordert einen Verlusttangens (Df) von weniger als 0,002. Bei Frequenzen über 40 GHz muss jeder Aspekt des PCB-Designs sorgfältig optimiert werden, um sicherzustellen, dass das Signal sauber und unverzerrt bleibt.

Analyse und Messung der Signalintegrität

Grundlagen der Augendiagramm-Analyse

Augendiagramme bieten eine umfassende Visualisierung der Signalqualität, indem sie mehrere Bitübergänge überlagern:

Kritische Augenparameter:

- Augenöffnung: Bestimmt den Rauschrahmen

- Kreuzungsprozentsatz: Zeigt die Tastverhältnisverzerrung an

- Anstiegs-/Abfallzeit: Zeigt Bandbreitenbeschränkungen an

- Jitter-Komponenten: Zufällig vs. deterministisch

Interpretieren von Augendiagrammen:

- Weit geöffnetes Auge: Gute Signalintegrität

- Vertikale Schließung: Amplitudenrauschen, Übersprechen

- Horizontaler Verschluss: Übermäßiges Zittern

- Mehrere Ösen (PAM4): Erfordert 3 durchsichtige Öffnungen

Anforderungen an die Messung:

- Oszilloskop-Bandbreite: >2,5× Signalfrequenz

- Sample-Größe: >1 Million Wellenformen

- Richtiges Antasten: Minimieren Sie Belastungseffekte

Analyse des Zeit- und Frequenzbereichs

TDR/TDT-Messungen:

- Deckt Impedanzdiskontinuitäten auf

- Lokalisiert Problemzonen

- Charakterisiert über Übergänge

- Validiert Simulationsmodelle

S-Parameter-Analyse:

- S11/S22: Rückflussdämpfung (mindestens <-10dB)

- S21: Einfügedämpfung (anwendungsabhängig)

- S31/41: Übersprech-Isolation (>30dB)

- Mixed-Mode: Differentielle Charakterisierung

Häufige Probleme und Lösungen bei der Signalintegrität

Verwalten von Übersprechen in dichten Layouts

Das Übersprechen verschlechtert sich, wenn die Kantengeschwindigkeiten abnehmen und die Routing-Dichte zunimmt. Sie erfolgt durch kapazitive und induktive Kopplung, was zu Interferenzen am nahen Ende (NEXT) und am fernen Ende (FEXT) führt.

Übersprechmechanismen:

- Kapazitiv: Kopplung des elektrischen Feldes zwischen Leiterbahnen

- Induktiv: Magnetfeldkopplung zwischen Leiterbahnen

- Nahes Ende (NEXT): Interferenz an der Quelle

- Gegenstelle (FEXT): Interferenz am Empfänger

Strategien zur Risikominderung:

- 3W Abstand: Einfach zu implementieren mit 10-15 dB Isolationsverstärkung und niedrigen Kosten.

- Guard Traces: Bietet eine Isolierung von 15-20 dB bei moderater Implementierungskomplexität und moderaten Kosten.

- Über Zaun: Erreicht eine Isolierung von 20-30 dB, ist aber komplexer und mit mittleren Kosten verbunden.

- Separate Layer: Bietet eine Isolierung von >40 dB, erfordert jedoch ein sorgfältiges Design und verursacht hohe Kosten.

Best Practices:

- Verlegen Sie Verfolgungen senkrecht auf benachbarten Layern.

- Minimieren Sie parallele Verfolgungsläufe, um die Kopplung zu reduzieren.

- Verwenden Sie nach Möglichkeit differentielle Signalisierung, um die Störfestigkeit zu verbessern.

- Implementieren Sie ein geeignetes Stackup-Design, um Übersprechen zu minimieren.

Kontrolle von Reflexionen und Impedanz

Reflexionen durch Impedanzdiskontinuitäten führen zu Signalverschlechterungen und Datenfehlern. Häufige Ursachen für diese Diskontinuitäten sind Via-Übergänge, Steckerschnittstellen, Änderungen der Leiterbahnbreite und Übergänge der Referenzebene.

Lösungen:

- Optimieren Sie über Antipad-Abmessungen, um reibungslose Übergänge zu gewährleisten.

- Entwerfen Sie geeignete Startmechanismen an den Schnittstellen, um die Impedanz anzupassen.

- Verwenden Sie allmähliche Verjüngungen für Leiterbahnen, um abrupte Impedanzänderungen zu verhindern.

- Behalten Sie kontinuierliche Referenzebenen über alle Schichten bei, um Signalreflexionen zu reduzieren.

Techniken zur Jitter-Reduzierung

Übermäßiger Jitter schränkt die Augenbreite ein und kann Bitfehler verursachen, die zu einer schlechten Signalqualität führen. Jitter setzt sich in der Regel aus zufälligem Jitter (RJ) und deterministischem Jitter (DJ) zusammen, wobei der Gesamt-Jitter (TJ) die Summe beider Komponenten ist.

Jitter-Komponenten:

- Zufälliger Jitter (RJ): In der Regel 1-2 ps RMS.

- Deterministischer Jitter (DJ)**: Normalerweise 5-20 ps Spitze.

- Gesamter Jitter (TJ): TJ = DJ + 14×RJ (bei Bitfehlerrate 10^-12).

Reduktionsstrategien:

- Verwenden Sie Taktquellen mit geringem Jitter, um Timing-Fehler zu minimieren.

- Minimieren Sie Diskrepanzen bei der Leiterbahnlänge, um Signalverzögerungen zu vermeiden.

- Kontrollieren Sie das Rauschen der Stromversorgung, um Jitter-induzierte Fehler zu reduzieren.

- Implementieren Sie eine ordnungsgemäße Terminierung, um die Signalintegrität zu erhalten.

- Fügen Sie bei Bedarf eine Entzerrung hinzu, um die Signalverschlechterung auszugleichen.

Best Practices für die Integrität hochfrequenter Signale

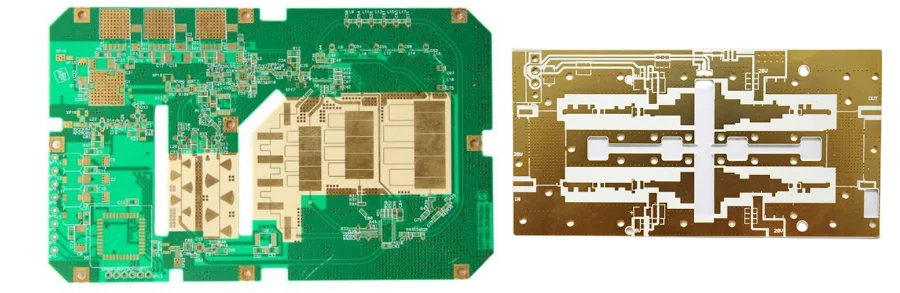

Optimiertes PCB-Stack-up-Design

Ein richtig konzipierter Stackup bildet die Grundlage für die Signalintegrität:

Schlüsselprinzipien:

- Benachbarte Masse-/Versorgungsebenen für jede Signalschicht

- Symmetrischer Aufbau verhindert Verzug

- Dünne Dielektrika für eine enge Kopplung

- Konsistente Impedanz über alle Schichten hinweg

Beispiel für einen 8-lagigen High-Speed-Stack-up:

- L1/L8: Mikrostreifensignale (kontrollierte Impedanz)

- L2/L7: Grundflächen (durchgehend)

- L3/L6: Stripline-Hochgeschwindigkeitspaare

- L4/L5: Strom-/Massekern

Implementierung von Differentialpaaren

Die differentielle Signalisierung bietet eine überlegene Störfestigkeit:

Design-Anforderungen:

- Längenanpassung: <0,025 mm innerhalb des Paares

- Gleichmäßiger Abstand: Kopplung beibehalten

- Symmetrisches Routing: Gleiche parasitäre Eigenschaften

- Keine Aufteilung zwischen Paaren

Häufige Anwendungen:

- PCIe: 85 Ω differenziell

- Ethernet: 100Ω differenziell

- USB 3.0: 90 Ω differenziell

- HDMI: 100Ω differenziell

Über Optimierungsstrategien

Durchkontaktierungen wirken sich erheblich auf die Signalintegrität oberhalb von 5 GHz aus:

Optimierungstechniken:

- Übergänge minimieren: Routen Sie nach Möglichkeit auf einer einzigen Ebene

- Rückbohren: Stichproben >0,5 mm bei >10 GHz entfernen

- HDI Microvias: Einsatz für >20 GHz Anwendungen

- Ground Vias: Innerhalb von 1 mm von Signaldurchkontaktierungen platzieren

Die Rolle der Leistungsintegrität für die Signalqualität

Das Rauschen der Stromversorgung wirkt sich durch mehrere Mechanismen direkt auf die Signalintegrität aus:

Anforderungen an das PDN-Design

** Berechnung der Zielimpedanz:** Ztarget = Vripple / (0,5 × Itransient)

Für 1V Versorgung mit 50mV Welligkeit und 10A Transiente: Ztarget = 0,05 / 5 = 10mΩ

** Erreichen der Zielimpedanz:**

- Bulk-Kondensatoren: 100-1000μF

- Keramische Entkopplung: 0,1-10 μF

- Hochfrequenz: 10-100nF

- Eingebettete Kapazität: <1nF

Entkopplungsstrategie

Platzierungsrichtlinien:

- Innerhalb von 2 mm von Stromanschlüssen für >1 GHz

- Mehrere Durchkontaktierungen für niedrige Induktivität

- Direkte Anbindung an die Massefläche

- Über das Brett verteilt

Simulations- und Verifikationswerkzeuge

Pre-Layout-Analyse

Wesentliche Simulationen:

- Planung des Kanalbudgets

- Erkundung der Topologie

- Wesentliche Kompromisse

- Optimierung der Terminierung

Anforderungen an das Werkzeug:

- 2D-Feldlöser für schnelle Impedanz

- 3D-EM für komplexe Strukturen

- Schaltungssimulation für die Systemanalyse

- Statistische Analyse für den Ertrag

Post-Layout-Verifizierung

Ablauf der Validierung:

- Parasiten des Layouts extrahieren

- 3D-Strukturen einbinden

- Eckenanalyse ausführen

- Generieren von Augendiagrammen

- Überprüfen der Spezifikationen

Korrelationsgenauigkeit:

- Impedanz: ±5%

- Verlust: ±10%

- Übersprechen: ±15%

- Erfordert genaue Modelle

Warum sollten Sie sich für HILPCB für die Signalintegrität entscheiden?

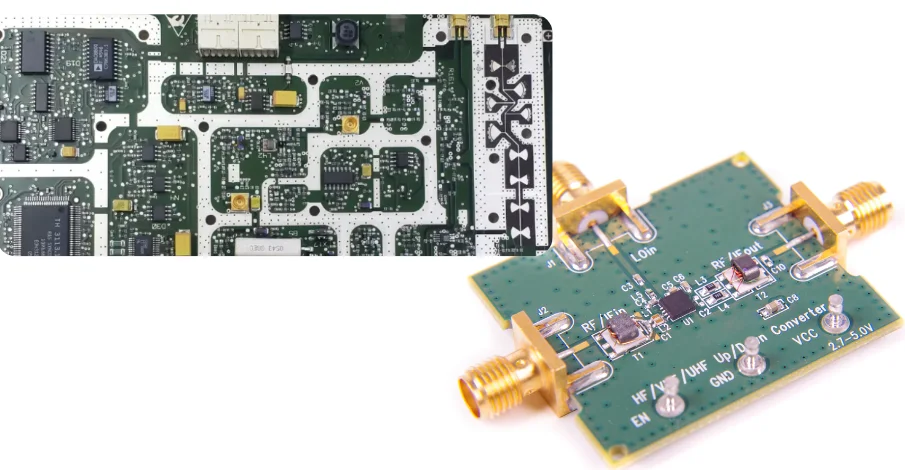

HILPCB bietet umfassende Lösungen für die Signalintegrität für Hochfrequenzanwendungen:

- Design Services: SI-Analyse vor dem Layout

- Simulation: HFSS-, CST-, Sigrity-Tools

- Materialien: Komplettes HF-/Mikrowelleninventar

- Testen: TDR, VNA bis 40 GHz

- Erfahrung: 5G, Radar, HPC-Anwendungen

- Support: Kompetente technische Beratung

Häufig gestellte Fragen

F1: Was verursacht Probleme mit der Signalintegrität bei hohen Frequenzen? A: Zu den Hauptursachen gehören Impedanzdiskontinuitäten, übermäßiges Übersprechen, frequenzabhängige Verluste und Rauschen bei der Stromversorgung. Die Probleme verschlimmern sich mit schnelleren Kantenraten und höheren Frequenzen.

F2: Woher weiß ich, ob ich Probleme mit der Signalintegrität habe? A: Suchen Sie nach Diagrammen mit geschlossenem Auge, hoher BER (>10^-12), übermäßigem Jitter (>0,3 UI), zeitweiligen Fehlern oder nicht bestandenen Konformitätstests.

F3: Wann sollte ich mir Gedanken über die Signalintegrität machen? A: SI ist in Betracht zu ziehen, wenn die Frequenzen 100 MHz überschreiten, die Anstiegszeiten unter 1 ns fallen oder die Leiterbahnlängen bei Betriebsfrequenz λ/10 überschreiten.

F4: Was ist der Unterschied zwischen NEXT und FEXT? A: NEXT wird am Quellende angezeigt und ist in der Regel schlechter. FEXT erscheint am anderen Ende und akkumuliert sich mit gekoppelter Länge. Stripline minimiert FEXT.

F5: Wie viel trägt die SI-Analyse zur Designzeit bei? A: Eine ordnungsgemäße SI-Analyse trägt 20-30 % zum ursprünglichen Design bei, spart aber insgesamt 40-50 %, indem sie die Anzahl der Prototyp-Iterationen reduziert.

F6: Was ist für die Signalintegrität am wichtigsten? A: Die kontrollierte Impedanz ist von grundlegender Bedeutung, gefolgt von einem ordnungsgemäßen Aufbaudesign, minimierten Diskontinuitäten und einer angemessenen Leistungsabgabe.