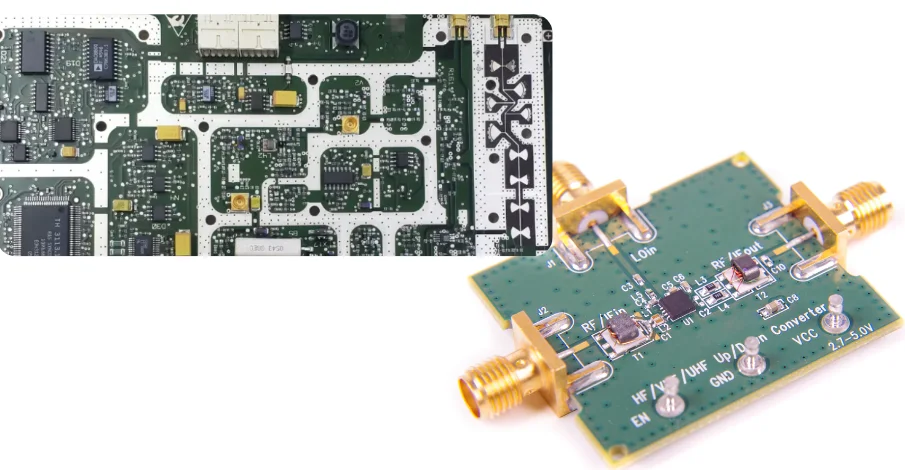

Signal integrity determines success or failure in high-frequency PCB designs. As data rates exceed 25 Gbps and frequencies push beyond 40 GHz, maintaining clean signals requires systematic approaches to design, analysis, and validation. This guide provides practical solutions for achieving superior signal integrity in demanding applications.

What is Signal Integrity and Why It's Critical in HF PCB Design

Signal integrity refers to the quality of electrical signals as they travel through a PCB, and it is especially critical in HF PCB (high-frequency PCB) design. As signal frequencies increase, maintaining signal integrity means preserving important parameters such as amplitude, timing, and waveform shape. Distortion in these parameters can lead to significant signal degradation, especially at high frequencies where even minor issues can cause data errors.

The key metrics for evaluating signal integrity in HF PCBs include eye height (the vertical opening for bit decisions, typically >100mV), eye width (the timing margin, typically >0.6 UI), and jitter (timing variations, typically <0.3 UI for most systems). The bit error rate (BER) is also an important measure, with a target of <10^-12, ensuring that the system can transmit data reliably without errors.

As the frequency increases, so do the challenges in maintaining signal integrity. For HF PCBs operating at 1-5 GHz, impedance control and minimizing crosstalk are crucial, with a return loss target of >15dB. At 5-20 GHz, the focus shifts to minimizing loss and optimizing via transitions, with an insertion loss of less than 3dB. At 20-40 GHz, surface roughness becomes critical, requiring a loss tangent (Df) of less than 0.002. For frequencies above 40 GHz, every aspect of the PCB design needs to be carefully optimized to ensure that the signal remains clean and undistorted.

How to Analyze and Measure Signal Integrity

Eye Diagram Analysis Fundamentals

Eye diagrams provide comprehensive visualization of signal quality by overlaying multiple bit transitions:

Critical Eye Parameters:

- Eye Opening: Determines noise margin

- Crossing Percentage: Indicates duty cycle distortion

- Rise/Fall Time: Shows bandwidth limitations

- Jitter Components: Random vs deterministic

Interpreting Eye Diagrams:

- Wide open eye: Good signal integrity

- Vertical closure: Amplitude noise, crosstalk

- Horizontal closure: Excessive jitter

- Multiple eyes (PAM4): Requires 3 clear openings

Measurement Requirements:

- Oscilloscope bandwidth: >2.5× signal frequency

- Sample size: >1 million waveforms

- Proper probing: Minimize loading effects

Time and Frequency Domain Analysis

TDR/TDT Measurements:

- Reveals impedance discontinuities

- Locates problem areas

- Characterizes via transitions

- Validates simulation models

S-Parameter Analysis:

- S11/S22: Return loss (<-10dB minimum)

- S21: Insertion loss (application dependent)

- S31/41: Crosstalk isolation (>30dB)

- Mixed-mode: Differential characterization

Common Signal Integrity Problems and Solutions

Managing Crosstalk in Dense Layouts

Crosstalk worsens as edge rates decrease and routing density increases. It occurs through capacitive and inductive coupling, leading to near-end (NEXT) and far-end (FEXT) interference.

Crosstalk Mechanisms:

- Capacitive: Electric field coupling between traces

- Inductive: Magnetic field coupling between traces

- Near-end (NEXT): Interference at the source

- Far-end (FEXT): Interference at the receiver

Mitigation Strategies:

- 3W Spacing: Easy to implement with 10-15 dB isolation gain and low cost.

- Guard Traces: Offers 15-20 dB isolation, with moderate implementation complexity and cost.

- Via Fencing: Achieves 20-30 dB isolation but is more complex and comes with medium cost.

- Separate Layers: Provides >40 dB isolation but requires careful design and incurs high costs.

Best Practices:

- Route traces perpendicular on adjacent layers.

- Minimize parallel trace runs to reduce coupling.

- Use differential signaling where possible for better noise immunity.

- Implement proper stackup design to minimize crosstalk.

Controlling Reflections and Impedance

Reflections from impedance discontinuities lead to signal degradation and data errors. Common sources of these discontinuities include via transitions, connector interfaces, trace width changes, and reference plane transitions.

Solutions:

- Optimize via antipad dimensions to ensure smooth transitions.

- Design proper launch mechanisms at interfaces to match impedance.

- Use gradual tapers for traces to prevent abrupt impedance changes.

- Maintain continuous reference planes across all layers to reduce signal reflections.

Jitter Reduction Techniques

Excessive jitter limits eye width and can cause bit errors, leading to poor signal quality. Jitter is typically made up of random jitter (RJ) and deterministic jitter (DJ), where total jitter (TJ) is the sum of both components.

Jitter Components:

- Random Jitter (RJ): Typically 1-2 ps RMS.

- Deterministic Jitter (DJ): Usually 5-20 ps peak.

- Total Jitter (TJ): TJ = DJ + 14×RJ (at Bit Error Rate 10^-12).

Reduction Strategies:

- Use low-jitter clock sources to minimize timing errors.

- Minimize trace length mismatches to avoid signal delay.

- Control power supply noise to reduce jitter-induced errors.

- Implement proper termination to maintain signal integrity.

- Add equalization when necessary to compensate for signal degradation.

Best Practices for High-frequency Signal Integrity

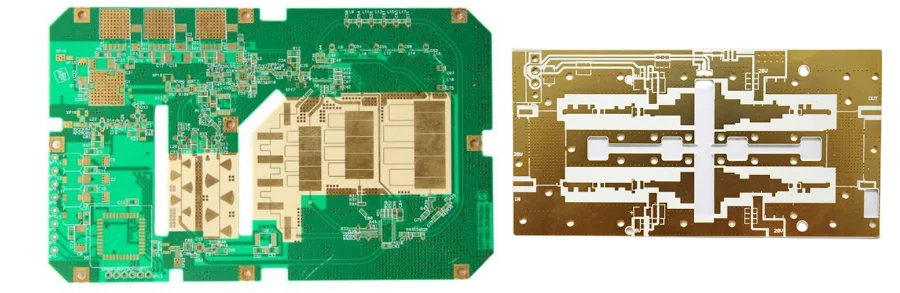

Optimized PCB Stack-up Design

A properly designed stackup forms the foundation for signal integrity:

Key Principles:

- Adjacent ground/power planes for every signal layer

- Symmetric construction prevents warpage

- Thin dielectrics for tight coupling

- Consistent impedance across layers

Example 8-Layer High-Speed Stack-up:

- L1/L8: Microstrip signals (controlled impedance)

- L2/L7: Ground planes (continuous)

- L3/L6: Stripline high-speed pairs

- L4/L5: Power/ground core

Differential Pair Implementation

Differential signaling provides superior noise immunity:

Design Requirements:

- Length matching: <0.025mm within pair

- Consistent spacing: Maintain coupling

- Symmetric routing: Equal parasitics

- No splits between pairs

Common Applications:

- PCIe: 85Ω differential

- Ethernet: 100Ω differential

- USB 3.0: 90Ω differential

- HDMI: 100Ω differential

Via Optimization Strategies

Vias significantly impact signal integrity above 5 GHz:

Optimization Techniques:

- Minimize Transitions: Route on single layer when possible

- Backdrilling: Remove stubs >0.5mm at >10 GHz

- HDI Microvias: Use for >20 GHz applications

- Ground Vias: Place within 1mm of signal vias

Power Integrity's Role in Signal Quality

Power supply noise directly affects signal integrity through multiple mechanisms:

PDN Design Requirements

Target Impedance Calculation: Ztarget = Vripple / (0.5 × Itransient)

For 1V supply with 50mV ripple and 10A transient: Ztarget = 0.05 / 5 = 10mΩ

Achieving Target Impedance:

- Bulk capacitors: 100-1000μF

- Ceramic decoupling: 0.1-10μF

- High-frequency: 10-100nF

- Embedded capacitance: <1nF

Decoupling Strategy

Placement Guidelines:

- Within 2mm of power pins for >1 GHz

- Multiple vias for low inductance

- Direct ground plane connection

- Distributed across board

Simulation and Verification Tools

Pre-Layout Analysis

Essential Simulations:

- Channel budget planning

- Topology exploration

- Material trade-offs

- Termination optimization

Tool Requirements:

- 2D field solvers for quick impedance

- 3D EM for complex structures

- Circuit simulation for system analysis

- Statistical analysis for yield

Post-Layout Verification

Validation Flow:

- Extract layout parasitics

- Include 3D structures

- Run corner analysis

- Generate eye diagrams

- Verify specifications

Correlation Accuracy:

- Impedance: ±5%

- Loss: ±10%

- Crosstalk: ±15%

- Requires accurate models

Why Choose HILPCB for Signal Integrity

HILPCB provides comprehensive signal integrity solutions for high-frequency applications:

- Design Services: Pre-layout SI analysis

- Simulation: HFSS, CST, Sigrity tools

- Materials: Complete RF/microwave inventory

- Testing: TDR, VNA to 40 GHz

- Experience: 5G, radar, HPC applications

- Support: Expert engineering consultation

Frequently Asked Questions

Q1: What causes signal integrity problems at high frequencies? A: Primary causes include impedance discontinuities, excessive crosstalk, frequency-dependent losses, and power supply noise. Problems worsen with faster edge rates and higher frequencies.

Q2: How do I know if I have signal integrity issues? A: Look for closed eye diagrams, high BER (>10^-12), excessive jitter (>0.3 UI), intermittent failures, or failing compliance tests.

Q3: When should I worry about signal integrity? A: Consider SI when: frequencies exceed 100 MHz, rise times drop below 1ns, or trace lengths exceed λ/10 at operating frequency.

Q4: What's the difference between NEXT and FEXT? A: NEXT appears at the source end and is typically worse. FEXT appears at the far end and accumulates with coupled length. Stripline minimizes FEXT.

Q5: How much does SI analysis add to design time? A: Proper SI analysis adds 20-30% to initial design but saves 40-50% overall by reducing prototype iterations.

Q6: What's most important for signal integrity? A: Controlled impedance is fundamental, followed by proper stackup design, minimized discontinuities, and adequate power delivery.