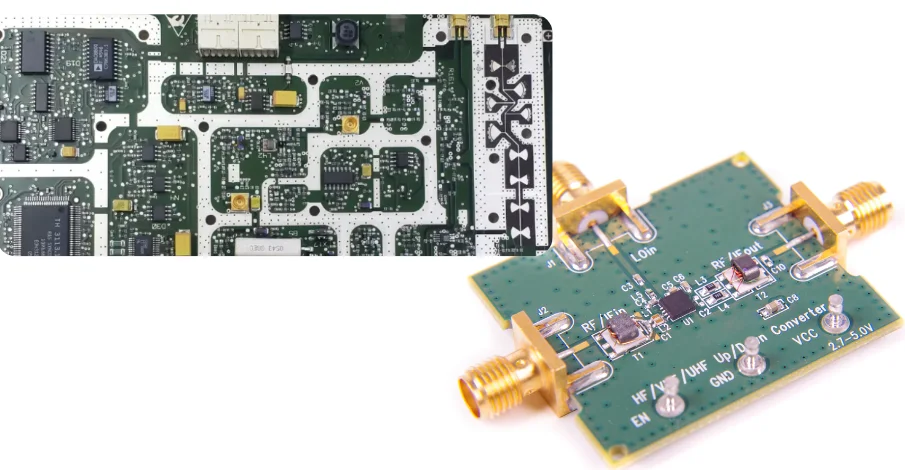

L'intégrité du signal détermine le succès ou l'échec dans les conceptions de PCB haute fréquence. Alors que les débits de données dépassent 25 Gbps et que les fréquences atteignent plus de 40 GHz, maintenir des signaux propres nécessite des approches systématiques de conception, d'analyse et de validation. Ce guide fournit des solutions pratiques pour atteindre une intégrité du signal supérieure dans des applications exigeantes.

Qu'est-ce que l'intégrité du signal et pourquoi est-elle critique dans la conception PCB HF ?

L'intégrité du signal fait référence à la qualité des signaux électriques lorsqu'ils traversent un PCB, et elle est particulièrement critique dans la conception de PCB HF (PCB haute fréquence). À mesure que les fréquences des signaux augmentent, maintenir l'intégrité du signal signifie préserver des paramètres importants tels que l'amplitude, le timing et la forme de l'onde. Une distorsion de ces paramètres peut entraîner une dégradation significative du signal, surtout à haute fréquence où même des problèmes mineurs peuvent causer des erreurs de données.

Les métriques clés pour évaluer l'intégrité du signal dans les PCB HF incluent la hauteur de l'œil (l'ouverture verticale pour les décisions de bit, typiquement >100mV), la largeur de l'œil (la marge de timing, typiquement >0,6 UI) et le gigue (variations de timing, typiquement <0,3 UI pour la plupart des systèmes). Le taux d'erreur binaire (BER) est également une mesure importante, avec une cible de <10^-12, garantissant que le système peut transmettre des données de manière fiable sans erreurs.

À mesure que la fréquence augmente, les défis pour maintenir l'intégrité du signal augmentent également. Pour les PCB HF fonctionnant à 1-5 GHz, le contrôle d'impédance et la minimisation de la diaphonie sont cruciaux, avec une cible de perte de retour >15dB. À 5-20 GHz, l'accent est mis sur la minimisation des pertes et l'optimisation des transitions via, avec une perte d'insertion inférieure à 3dB. À 20-40 GHz, la rugosité de surface devient critique, nécessitant une tangente de perte (Df) inférieure à 0,002. Pour les fréquences supérieures à 40 GHz, chaque aspect de la conception du PCB doit être soigneusement optimisé pour garantir que le signal reste propre et non déformé.

Comment analyser et mesurer l'intégrité du signal

Principes fondamentaux de l'analyse du diagramme de l'œil

Les diagrammes de l'œil fournissent une visualisation complète de la qualité du signal en superposant plusieurs transitions de bits :

Paramètres critiques de l'œil :

- Ouverture de l'œil : Détermine la marge de bruit

- Pourcentage de croisement : Indique une distorsion du cycle de service

- Temps de montée/descente : Montre les limitations de bande passante

- Composants du gigue : Aléatoire vs déterministe

Interprétation des diagrammes de l'œil :

- Œil largement ouvert : Bonne intégrité du signal

- Fermeture verticale : Bruit d'amplitude, diaphonie

- Fermeture horizontale : Gigue excessif

- Multiples yeux (PAM4) : Nécessite 3 ouvertures claires

Exigences de mesure :

- Bande passante de l'oscilloscope : >2,5× la fréquence du signal

- Taille d'échantillon : >1 million de formes d'onde

- Sondage approprié : Minimiser les effets de charge

Analyse dans les domaines temporel et fréquentiel

Mesures TDR/TDT :

- Révèle les discontinuités d'impédance

- Localise les zones problématiques

- Caractérise les transitions via

- Valide les modèles de simulation

Analyse des paramètres S :

- S11/S22 : Perte de retour (<-10dB minimum)

- S21 : Perte d'insertion (dépendante de l'application)

- S31/41 : Isolation de la diaphonie (>30dB)

- Mode mixte : Caractérisation différentielle

Problèmes courants d'intégrité du signal et solutions

Gestion de la diaphonie dans les layouts denses

La diaphonie s'aggrave à mesure que les taux de bord diminuent et que la densité de routage augmente. Elle se produit par couplage capacitif et inductif, entraînant des interférences près de l'extrémité (NEXT) et loin de l'extrémité (FEXT).

Mécanismes de diaphonie :

- Capacitif : Couplage de champ électrique entre traces

- Inductif : Couplage de champ magnétique entre traces

- Près de l'extrémité (NEXT) : Interférence à la source

- Loin de l'extrémité (FEXT) : Interférence au récepteur

Stratégies d'atténuation :

- Espacement 3W : Facile à implémenter avec un gain d'isolation de 10-15 dB et un faible coût.

- Traces de garde : Offre 15-20 dB d'isolation, avec une complexité d'implémentation et un coût modérés.

- Clôture de vias : Atteint 20-30 dB d'isolation mais est plus complexe et a un coût moyen.

- Couches séparées : Fournit >40 dB d'isolation mais nécessite une conception minutieuse et a un coût élevé.

Bonnes pratiques :

- Routez les traces perpendiculairement sur les couches adjacentes.

- Minimisez les parcours parallèles de traces pour réduire le couplage.

- Utilisez la signalisation différentielle lorsque possible pour une meilleure immunité au bruit.

- Implémentez une conception de stackup appropriée pour minimiser la diaphonie.

Contrôle des réflexions et de l'impédance

Les réflexions dues aux discontinuités d'impédance entraînent une dégradation du signal et des erreurs de données. Les sources courantes de ces discontinuités incluent les transitions via, les interfaces de connecteurs, les changements de largeur de trace et les transitions de plan de référence.

Solutions :

- Optimisez les dimensions des antipads via pour assurer des transitions fluides.

- Conçoivez des mécanismes de lancement appropriés aux interfaces pour correspondre à l'impédance.

- Utilisez des rétrécissements graduels pour les traces pour éviter les changements abrupts d'impédance.

- Maintenez des plans de référence continus sur toutes les couches pour réduire les réflexions de signal.

Techniques de réduction du gigue

Un gigue excessif limite la largeur de l'œil et peut causer des erreurs de bits, entraînant une mauvaise qualité de signal. Le gigue est généralement composé de gigue aléatoire (RJ) et de gigue déterministe (DJ), où le gigue total (TJ) est la somme des deux composants.

Composants du gigue :

- Gigue aléatoire (RJ) : Typiquement 1-2 ps RMS.

- Gigue déterministe (DJ) : Généralement 5-20 ps en crête.

- Gigue total (TJ) : TJ = DJ + 14×RJ (à un taux d'erreur binaire de 10^-12).

Stratégies de réduction :

- Utilisez des sources d'horloge à faible gigue pour minimiser les erreurs de timing.

- Minimisez les déséquilibres de longueur de trace pour éviter les retards de signal.

- Contrôlez le bruit de l'alimentation pour réduire les erreurs induites par le gigue.

- Implémentez une terminaison appropriée pour maintenir l'intégrité du signal.

- Ajoutez une égalisation si nécessaire pour compenser la dégradation du signal.

Bonnes pratiques pour l'intégrité du signal haute fréquence

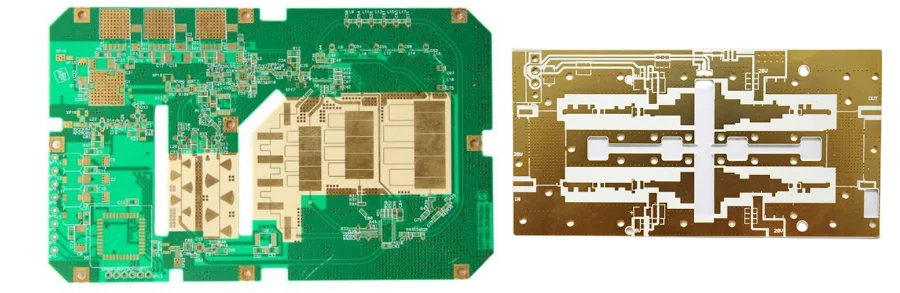

Conception optimisée du stackup PCB

Un stackup bien conçu forme la base de l'intégrité du signal :

Principes clés :

- Plans de masse/alimentation adjacents pour chaque couche de signal

- Construction symétrique pour éviter le gauchissement

- Diélectriques minces pour un couplage serré

- Impédance cohérente sur toutes les couches

Exemple de stackup 8 couches haute vitesse :

- L1/L8 : Signaux microstrip (impédance contrôlée)

- L2/L7 : Plans de masse (continus)

- L3/L6 : Paires différentielles stripline

- L4/L5 : Noyau alimentation/masse

Implémentation de paires différentielles

La signalisation différentielle offre une meilleure immunité au bruit :

Exigences de conception :

- Correspondance de longueur : <0,025mm dans la paire

- Espacement cohérent : Maintenir le couplage

- Routage symétrique : Parasitiques égaux

- Pas de séparation entre les paires

Applications courantes :

- PCIe : 85Ω différentiel

- Ethernet : 100Ω différentiel

- USB 3.0 : 90Ω différentiel

- HDMI : 100Ω différentiel

Stratégies d'optimisation des vias

Les vias impactent significativement l'intégrité du signal au-dessus de 5 GHz :

Techniques d'optimisation :

- Minimiser les transitions : Routez sur une seule couche si possible

- Backdrilling : Supprimez les moignons >0,5mm à >10 GHz

- Microvias HDI : Utilisez pour les applications >20 GHz

- Vias de masse : Placez à moins de 1mm des vias de signal

Rôle de l'intégrité de puissance dans la qualité du signal

Le bruit de l'alimentation affecte directement l'intégrité du signal par plusieurs mécanismes :

Exigences de conception du PDN

Calcul de l'impédance cible : Ztarget = Vripple / (0,5 × Itransient)

Pour une alimentation de 1V avec une ondulation de 50mV et un transitoire de 10A : Ztarget = 0,05 / 5 = 10mΩ

Atteindre l'impédance cible :

- Condensateurs bulk : 100-1000μF

- Découplage céramique : 0,1-10μF

- Haute fréquence : 10-100nF

- Capacité embarquée : <1nF

Stratégie de découplage

Lignes directrices de placement :

- À moins de 2mm des broches d'alimentation pour >1 GHz

- Multiples vias pour une faible inductance

- Connexion directe au plan de masse

- Répartis sur la carte

Outils de simulation et de vérification

Analyse pré-layout

Simulations essentielles :

- Planification du budget de canal

- Exploration de topologie

- Compromis matériaux

- Optimisation de terminaison

Exigences des outils :

- Solveurs 2D pour une impédance rapide

- EM 3D pour des structures complexes

- Simulation de circuit pour l'analyse système

- Analyse statistique pour le rendement

Vérification post-layout

Flux de validation :

- Extraire les parasitiques du layout

- Inclure les structures 3D

- Exécuter une analyse de coin

- Générer des diagrammes de l'œil

- Vérifier les spécifications

Précision de corrélation :

- Impédance : ±5%

- Perte : ±10%

- Diaphonie : ±15%

- Nécessite des modèles précis

Pourquoi choisir HILPCB pour l'intégrité du signal

HILPCB fournit des solutions complètes d'intégrité du signal pour les applications haute fréquence :

- Services de conception : Analyse SI pré-layout

- Simulation : Outils HFSS, CST, Sigrity

- Matériaux : Inventaire complet RF/micro-ondes

- Tests : TDR, VNA jusqu'à 40 GHz

- Expérience : Applications 5G, radar, HPC

- Support : Consultation d'ingénierie experte

Foire aux questions

Q1 : Quelles sont les causes des problèmes d'intégrité du signal à haute fréquence ? R : Les causes principales incluent les discontinuités d'impédance, une diaphonie excessive, les pertes dépendantes de la fréquence et le bruit de l'alimentation. Les problèmes s'aggravent avec des taux de bord plus rapides et des fréquences plus élevées.

Q2 : Comment savoir si j'ai des problèmes d'intégrité du signal ? R : Recherchez des diagrammes de l'œil fermés, un BER élevé (>10^-12), un gigue excessif (>0,3 UI), des échecs intermittents ou des tests de conformité échoués.

Q3 : Quand dois-je m'inquiéter de l'intégrité du signal ? R : Considérez l'IS lorsque : les fréquences dépassent 100 MHz, les temps de montée descendent en dessous de 1ns, ou les longueurs de trace dépassent λ/10 à la fréquence de fonctionnement.

Q4 : Quelle est la différence entre NEXT et FEXT ? R : NEXT apparaît à l'extrémité source et est généralement pire. FEXT apparaît à l'extrémité distante et s'accumule avec la longueur couplée. Le stripline minimise FEXT.

Q5 : Combien l'analyse SI ajoute-t-elle au temps de conception ? R : Une analyse SI appropriée ajoute 20-30 % à la conception initiale mais économise 40-50 % globalement en réduisant les itérations de prototype.

Q6 : Qu'est-ce qui est le plus important pour l'intégrité du signal ? R : L'impédance contrôlée est fondamentale, suivie par une conception de stackup appropriée, des discontinuités minimisées et une alimentation en puissance adéquate.