在 HILPCB,我们制造全系列的高速 PCB——从标准数字板到先进的差分信号解决方案——服务于信号完整性不容谈判的行业。在高速差分系统中,一个因素决定性能的成败:100 欧姆阻抗控制。

想象一下:尖端的 DDR5 内存系统通过了每次模拟。优质组件、完美的布线、细致的时序分析。但一旦组装完毕,它就会失败——出现数据损坏、眼图崩溃、内存接口变得不可靠。

通常,根本原因不是控制器或内存,而是不受控制的差分阻抗。

了解无形挑战

在千兆位数据速率下,差分对表现为具有复杂电磁相互作用的耦合传输线。与100欧姆差分阻抗的任何偏差都会引入信号反射,产生共模噪声,并降低时序裕度。这些影响会破坏数据完整性,增加误码率,并损害系统可靠性。

精度要求极其苛刻。仅 5-10 欧姆的失配就会消耗关键的时序预算,产生符号间干扰,并破坏高速差分系统中的相位关系。对于 DDR5 内存、USB 3.2 或 10G 以太网等应用,精确的 100 欧姆差分控制是实现可靠数据传输的基础。

高速数字:与物理赛跑

DDR5 内存接口代表了 100 欧姆差分阻抗控制的终极挑战。当数据速率达到 6400 MT/s 时,每个位转换发生在 150 皮秒内。在这些速度下,10% 的阻抗失配会通过反射和偏斜消耗 40% 的时序裕量。

考虑到现代存储器通道通过多个PCB层进行路由,需要通过转换来控制阻抗,复杂性会成倍增加。每次层的变化都会引入潜在的不连续性,必须通过精确的过孔设计、背钻技术,有时还需要先进的 HDI 微孔来管理这些不连续性。

卓越制造:从理论到现实

HILPCB 的 100 欧姆差动控制方法

在 HILPCB,我们开发了一种系统方法,将 100 欧姆的差异要求从设计约束转化为制造规范。此过程从电磁仿真开始,一直持续到生产验证。

生产前模拟和验证

我们的工程团队采用 3D 电磁仿真来预测整个叠层的差分阻抗行为。我们对走线耦合效应、参考平面接近度和过孔过渡影响进行建模,以确保在制造开始前 100 欧姆精度。

经常被忽视的一个关键因素是 FR4 PCB 材料中的玻璃编织效应。周期性玻璃纤维结构产生局部介电常数变化,导致差分阻抗沿单对变化 ±5Ω。对于关键应用,我们指定铺展玻璃结构或采用旋转技术来最大限度地减少这种影响。

提供精确度的过程控制

实现一致的 100 欧姆差分阻抗需要对制造变量的痴迷关注。我们的生产系统监控和控制:

- 走线宽度和间距均匀性 跨面板区域 ±0.5 mil

- 介电厚度一致性通过受控层压保持 ±5% 的公差

- 镀铜均匀性确保迹线横截面一致

- 环境控制保持 22°C ±1°C 温度和 45% ±5% 湿度

我们在实际生产几何测试试样上使用差分 TDR 测量和高达 20 GHz 的完整 S 参数表征来验证 100 欧姆性能。

关键应用的先进技术

一些应用需要超出标准能力的 100 欧姆差分控制。对于这些情况,我们提供专门的解决方案:

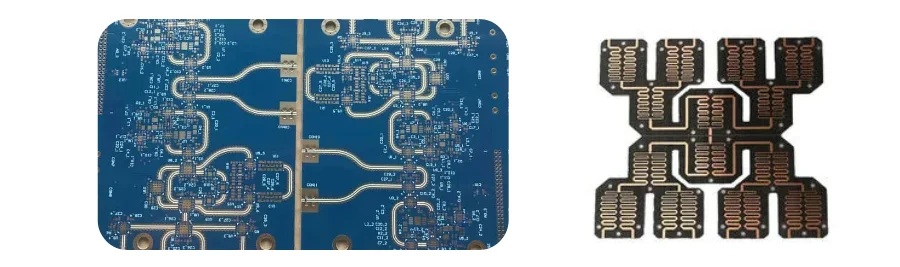

HDI PCB 技术可在紧凑的设计中实现复杂的差分布线,同时保持精确的 100 欧姆控制。顺序层压和微孔可在不影响阻抗精度的情况下实现最佳走线放置。

高速PCB叠层优化利用先进的材料和层排列来实现卓越的100欧姆差分性能,同时最大限度地减少串扰和EMI。

嵌入式元件集成将精密电阻器和电容器直接放置在 PCB 基板中,消除端接点的阻抗不连续性并提高整体信号完整性。

100 欧姆差分设计的 PCB 基板选择

用于差分信号的高级材料选项

- 超低倾斜材料 — 通过稳定的介电性能和一致的玻璃编织结构最大限度地减少对内偏斜;对于 DDR 和高速串行接口至关重要。

- 低损耗层压板 — 减少插入损耗并提高眼图性能;Nelco N4000-13 SI 等材料为 100 欧姆差分应用提供了出色的性能。

- 受控 Dk 玻璃 — 介电常数针对 100 欧姆差分阻抗进行了优化,频率变化最小,可在宽带宽内实现一致的性能。

环境稳定因素

100 欧姆差分阻抗必须在各种工作条件下保持稳定:

- 高速计算系统经常会经历显着的温度变化,这些变化可能会改变差分阻抗并影响时序裕度。

- 湿度变化会影响介电常数,并可能导致敏感应用中的阻抗漂移。

- 通过叠层优化和材料选择进行设计补偿,可在整个环境范围内保持稳定的 100 欧姆性能。

测试和验证:信任但验证

过程监控,实现 100 欧姆精度

真正的差分阻抗控制在制造过程中开始,而不是在制造之后开始。我们的生产线包含多个验证点:

成像后:光学测量确认差分对宽度和间距符合设计目标 蚀刻后:横截面分析验证蚀刻均匀性和最终导体几何形状 层压后:介电厚度测量确保差分对和参考平面之间的间距一致 最终测试:使用具有生产代表性的测试结构进行全面的差分阻抗验证

先进的表征方法

对于突破 100 欧姆差分性能极限的应用,标准 TDR 测量是不够的。我们采用复杂的表征技术:

差分 S 参数分析表征跨频率的阻抗行为,同时测量共模抑制和串扰性能。这些数据可以优化过孔过渡和连接器接口。

生产数据的统计分析确定了工艺参数与 100 欧姆差分性能之间的相关性。这种持续改进的方法使大批量生产的一致性达到了行业领先的一致性。

刚柔结合 PCB 验证 确保通过柔性区域和刚柔结合过渡保持 100 欧姆差分阻抗,这对于移动和可穿戴应用至关重要。

常见陷阱以及如何避免它们

破坏 100 欧姆差动控制的关键设计缺陷

即使拥有出色的制造,某些设计错误也会从一开始就破坏 100 欧姆差分阻抗:

- 参考平面不连续性:差分对下方接地层的分裂或间隙会产生严重的阻抗不连续性,无法在制造中校正。始终在关键的 100 欧姆差分布线下方保持连续的参考平面。

- 不匹配的过孔转换:通过不同过孔结构布线的差分对将存在阻抗和时序不匹配。设计通孔转换以保持 100 欧姆阻抗和配对匹配。

- 忽略对内间距:差分对内走线间距的微小变化可能会导致显着的 100 欧姆阻抗变化。在整个路线长度上保持一致的间距。

需要预测的制造变化

了解现实的制造公差可以实现更好的 100 欧姆差分设计裕度:

- 走线宽度:精密工艺典型值 ±0.5 mil;标准生产 ±1 mil

- 走线间距:先进的光刻技术可达到 ±0.3 mil;±0.5 mil 标准

- 介电厚度:受控材料为 ±5%;标准预浸料为 ±10%

- 铜厚度:典型值 ±10%;影响阻抗和时序

设计提示:在仿真工具中对这些公差进行建模,并与您的 PCB 制造商合作,将 100 欧姆差分目标与其工艺能力对齐。

与 HILPCB 合作,实现卓越的 100 欧姆差分

成功的 100 欧姆差分阻抗控制需要的不仅仅是制造能力,还需要对电磁物理和实际 PCB 生产现实的深入了解。在 HILPCB,我们将理论专业知识与成熟的制造经验相结合,为您最苛刻的应用提供一致、可靠的 100 欧姆差分性能。

我们的承诺不仅限于满足规格。我们在整个设计过程中与您合作,提供:

- 设计审查和优化,确保 100 欧姆差分可制造性

- 根据您的具体速度和环境要求提供材料选择指导

- 原型验证,具有全面的差异测试和文档

- 批量生产,具有统计过程控制和持续改进

- 故障分析并在出现挑战时采取纠正措施

无论您是在设计下一代内存系统、高速串行接口还是先进的网络设备,精确的 100 欧姆差分阻抗控制都可以决定成败。不要让这个关键参数碰运气。