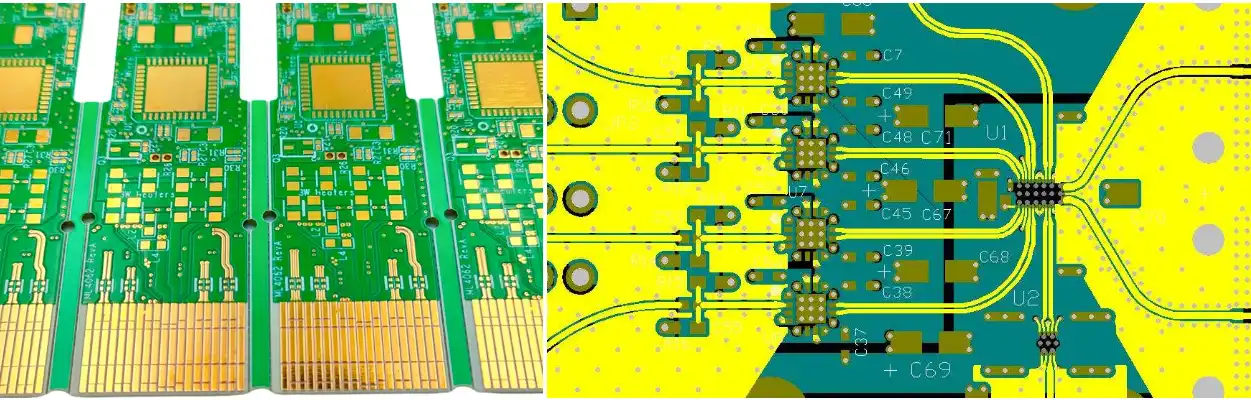

高速PCB制造 | 25–112 Gbps | PCIe Gen5/Gen6 | 阻抗±5%

适用于PAM4/NRZ通道的高速数字PCB:25–112 Gbps(每秒25至112千兆比特)SerDes、PCIe Gen5/Gen6、背钻、低损耗与超低损耗堆叠,以及通过TDR/VNA验证的±5%(正负5%)阻抗控制。7天(7天)快速打样原型。

通道优化与损耗预算管理

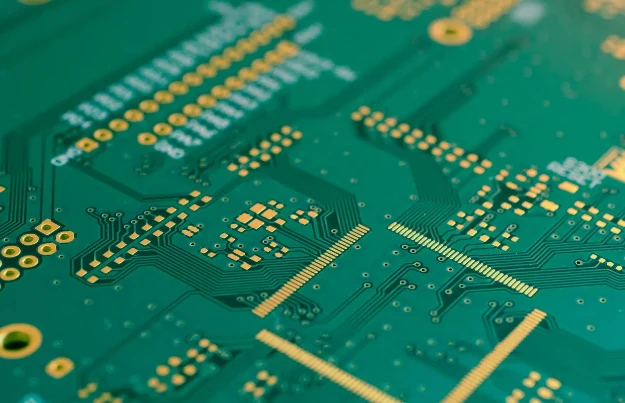

为PAM4/NRZ通道设计最大眼高和BER余量当上升时间降至100–200 ps(100至200皮秒)以下或数据速率超过10 Gbps(每秒10千兆比特)时,互连行为将主导系统整体性能。我们的高速设计聚焦三大支柱:插入损耗(材料Df 0.001–0.004——0.001至0.004)、阻抗控制(目标容差±5%——正负5%)以及电源分配网络(PDN)阻抗。通过采用受控阻抗设计和背钻去除残余桩,我们保持开放眼高和受控抖动,以满足CTLE/DFE均衡预算及低至10⁻¹²(每1万亿比特1个错误)的BER目标。

材料选择需同时满足损耗预算和信号传输距离。例如,Megtron 6(在10 GHz下Df≈0.002)支持12–15英寸(12至15英寸)的28 Gbps NRZ传输。

Tachyon 100G和Isola I-Speed配合低粗糙度铜箔可将56–112 Gbps(每秒56至112千兆比特)PAM4通道延伸至20–25英寸(20至25英寸)。与标准箔相比,低轮廓铜(Ra ≤1.5 µm——小于或等于1.5微米)可降低3–8%(3至8百分比)的插入损耗。关于介质优化,请参阅我们的高频材料指南和HDI PCB堆叠选项。

关键风险:不良过孔转换、未受控的参考平面变更或纤维编织效应可能导致偏移、模式转换及超出恢复能力的眼图闭合。电镀厚度不均还会加剧过孔桩共振和回波损耗,降低通道合规性。

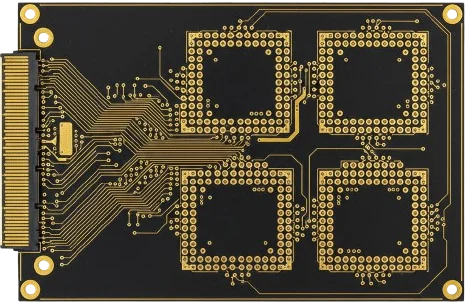

我们的解决方案:我们采用信号完整性仿真,结合S参数和3D场求解器进行布局前验证。通过背钻和TDR/VNA关联验证过孔优化,确保阻抗变化保持在±3%(正负3%)以内。每个设计均按IEEE 802.3/CEI规范进行时域反射(TDR)和眼图验证。针对超长距离或混合信号系统,结合背板PCB与高频PCB的混合构建可实现平衡的信号完整性和热控制。

- 差分阻抗85/90/100 Ω(欧姆)±5%(正负5%)经TDR验证

- 材料Df 0.001–0.004 @10 GHz(10吉赫兹下0.001至0.004)

- 背钻残余桩<10 mil(小于10密耳)适用于56 Gbps及以上

- 纤维编织偏移抑制:±7°(正负7度)布线或采用展纤玻璃

- PDN目标阻抗建模以满足瞬态电流需求

- 长度匹配容差5–10 mil(5至10密耳)

🚀 快速报价请求

🔧 获取完整制造能力

确定性制造实现可重复的S参数

统计过程控制与对位精度确保批次间一致性我们通过补偿介质厚度和走线宽度,将生产阻抗变化控制在±5%(正负5%)以内。LDI将走线宽度控制在标称值的±10%(正负10%);层间对位精度保持在±25–50 µm(正负25至50微米)。多深度背钻技术使残余桩长度<10–15 mil(小于10至15密耳),适用于25–28 Gbps;112 Gbps目标值约5 mil(约5密耳)。

顺序层压支持混合叠层(关键区域使用超低/低损耗材料,其他区域使用FR-4),在保持通道预算的同时将材料成本降低30–50%(30至50百分比)。树脂流动控制可防止玻璃纤维暴露导致局部Dk变化。参见高频/高速制造流程。对于同一设计中的大功率配电层,请评估我们的厚铜PCB能力以确保PDN稳健性。

- LDI走线宽度控制±10%(正负10%)

- 多深度背钻配合截面验证

- 混合叠层:超低损耗材料与标准材料结合

- 层间对位精度±25–50 µm(正负25至50微米)

- 低粗糙度铜箔附着(采用氧化物替代方案)

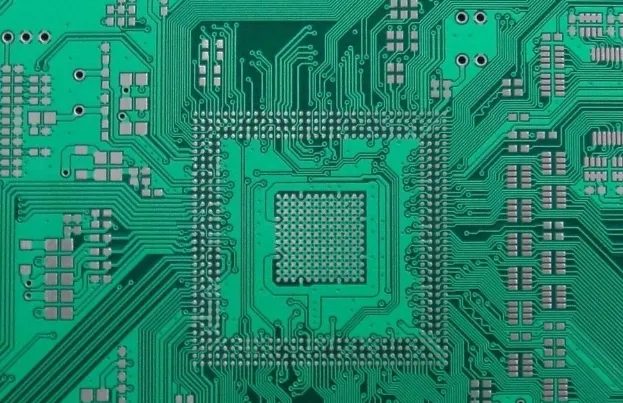

高速数字PCB技术规格

针对10 Gbps NRZ至112 Gbps PAM4(每秒10至112千兆比特)优化

| 参数 | 标准能力 | 高级能力 | 标准 |

|---|---|---|---|

层数 | 2–20层 | 最高48层 | IPC-2221 |

基材 | Isola I-Speed、RO4350B | Megtron 6/7、Tachyon 100G、PTFE | IPC-4103 |

板厚 | 0.8–2.4毫米(0.8至2.4毫米) | 0.4–5.0毫米(0.4至5.0毫米;厚度公差±5%——正负5%) | IPC-A-600 |

铜厚 | 0.5–2盎司(0.5至2盎司) | 最高5盎司(最高5盎司;PDN层) | IPC-4562 |

最小线宽/间距 | 75/75微米(3/3密耳) | 50/50微米(2/2密耳) | IPC-2221 |

介电常数(Dk) | 3.0–4.5(3.0至4.5) | <3.0(小于3.0;PTFE级) | 材料数据表 |

损耗角正切(Df) | <0.005 @10 GHz(10吉赫兹下小于0.005) | ≤0.002 @10 GHz(10吉赫兹下小于或等于0.002) | 材料数据表 |

阻抗控制 | ±10%(正负10%) | ±5%(正负5%) | IPC-2141 |

表面处理 | ENIG、化学沉银 | ENEPIG、软/硬金 | IPC-4552/4556 |

质量测试 | TDR、AOI、电测 | VNA、眼图、抖动分析 | IPC-9252 |

认证 | ISO 9001、UL、IPC Class 3 | IATF 16949、AS9100 | 行业标准 |

交付周期 | 7–15天(7至15天) | 5天(5天)加急 | 生产计划 |

准备开始您的PCB项目了吗?

无论您需要简单的原型还是复杂的生产运行,我们先进的制造能力确保卓越的质量和可靠性。30分钟内获取您的报价。

性能验证与统计过程控制

35 ps(35皮秒)上升沿的TDR可将阻抗变化定位至±2毫米(正负2毫米)。矢量网络分析仪测量DC–40 GHz(直流至40吉赫兹)时Sdd21不确定度为±0.1 dB(正负0.1分贝)。一致性检查包括:铜厚±10%(正负10%)、介质厚度±5%(正负5%)及几何尺寸符合设计目标。背钻残留长度通过切片确认。IPC Class 3工艺标准与统计过程控制确保关键制程能力指数Cpk≥1.33(大于或等于1.33)。

工程保证与认证

经验: 25–112 Gbps量产项目,具备背钻、盲埋孔和低粗糙度铜箔技术。

专长: 针对过孔/连接器的场求解器与3D电磁仿真;阻抗/对位/电镀的SPC控制;Cpk ≥1.33(大于或等于1.33)。

权威认证: IPC-6012 Class 3、IATF 16949、AS9100;随时可审计的文档体系。

可靠性: MES系统将批次码和序列号与TDR/VNA数据关联;提供批次报告。

- 工艺控制:介质层厚度、对位精度、铜箔粗糙度、背钻残留量

- 可追溯性:序列化、批次追踪、数字化流程单

- 验证手段:TDR/VNA测试、切片分析、温湿度应力测试

常见问题

何时应从FR-4转向低损耗或超低损耗材料?

背钻与顺序层压(盲埋孔)如何选择?

如何估算PDN目标阻抗?

标准FR-4能支持25 Gbps吗?

如何减轻纤维编织效应偏差?

哪种表面处理最适合高速应用?

体验先进的PCB制造卓越

从简单的原型到复杂的生产运行,我们的世界级工厂提供卓越的质量、快速的周转和有竞争力的价格。加入数千名信任我们PCB制造需求的满意客户。