Power integrity in high-frequency PCB design has become as critical as signal integrity for ensuring system performance. Modern RF systems and high-speed digital circuits demand clean, stable power delivery across frequencies from DC to tens of gigahertz. Power supply noise directly modulates RF signals, causes jitter in digital systems, and generates electromagnetic interference that can cause regulatory compliance failures. This comprehensive guide explores advanced techniques for designing robust power distribution networks (PDN) that meet the stringent requirements of today's high-frequency applications.

1. Understanding Power Requirements in High-frequency Systems

High-frequency systems using HF PCB technology face demanding power delivery challenges. RF power amplifiers can have peak-to-average current ratios above 10:1, requiring rapid current delivery to avoid voltage droop. Processors running beyond 1 GHz create fast current transients that demand ultra-low PDN impedance. At these speeds, power integrity and signal integrity are closely linked—small ripples, like 50 mV, can degrade RF transmitter EVM by several percent or introduce jitter in high-speed links, impacting performance and reliability.

Thermal effects further complicate HF PCB design. Low-efficiency RF amplifiers dissipate most of their power as heat, creating hot spots that shift component behavior. Temperature changes can alter regulator output, passive values, and transistor bias, risking instability. Effective HF PCB power design must manage both electrical performance and thermal control to maintain consistent operation under high-frequency, high-load conditions.

2. Power Distribution Network (PDN) Architecture

A well-designed PDN provides low impedance across all frequencies of interest while maintaining stability and efficiency. Modern PDN architectures employ hierarchical approaches with multiple regulation stages optimized for different frequency ranges.

Multi-Stage Regulation Strategy

The primary regulation stage converts input voltage (typically 12-48V) to intermediate rails using switching regulators optimized for efficiency:

Switching Regulator Design Considerations:

- Switching frequency: 500 kHz - 2 MHz typical

- Output ripple: <50mV peak-to-peak

- Transient response: <10μs settling time

- Efficiency target: >90% at full load

- EMI management: Shielding and filtering essential

Secondary regulation provides clean power for sensitive circuits:

Linear Regulator Implementation:

- Ultra-low noise: <10μV RMS (10 Hz - 100 kHz)

- PSRR: >60dB at 1 MHz

- Dropout voltage: <200mV for efficiency

- Thermal design: Adequate heatsinking required

Point-of-load (POL) regulation places regulators adjacent to high-current loads:

- Minimizes distribution losses

- Reduces voltage droop during transients

- Enables independent voltage optimization

- Simplifies current monitoring

Power Plane Design and Optimization

Power planes in multilayer PCB stackups serve as low-inductance current distribution networks:

Plane Capacitance Calculation: C = ε₀ × εr × A / h

For 100mm × 100mm planes with 0.1mm spacing on FR4: C = 8.85e-12 × 4.4 × 1e-2 / 1e-4 = 3.9nF

This distributed capacitance provides high-frequency decoupling above 100 MHz where discrete capacitors become ineffective due to mounting inductance.

Plane Pair Design Guidelines:

- Minimum 0.1mm spacing for effective capacitance

- Use high-εr materials between planes when possible

- Avoid slots and splits that increase inductance

- Implement 20-H rule to reduce edge radiation

- Add stitching vias every λ/20 at plane periphery

3. Decoupling Strategy for High-frequency Applications

Effective decoupling requires careful component selection, placement, and interconnect design to maintain low PDN impedance across the entire frequency spectrum.

Capacitor Selection and Characterization

Real capacitors exhibit parasitic inductance and resistance that limit high-frequency effectiveness:

Impedance vs. Frequency: Z = R + j(ωL - 1/ωC)

Self-resonant frequency (SRF): f_SRF = 1 / (2π√(LC))

Above SRF, capacitors become inductive and impedance increases with frequency.

Typical Capacitor Parameters:

| Package | Capacitance | ESL | SRF | Effective Range |

|---|---|---|---|---|

| 1206 | 10μF | 1.2nH | 1.5 MHz | DC - 1 MHz |

| 0805 | 1μF | 0.8nH | 5.6 MHz | 100 kHz - 5 MHz |

| 0603 | 0.1μF | 0.6nH | 20 MHz | 1 MHz - 20 MHz |

| 0402 | 10nF | 0.4nH | 80 MHz | 10 MHz - 80 MHz |

| 0201 | 1nF | 0.3nH | 290 MHz | 50 MHz - 200 MHz |

Placement and Layout Optimization

Capacitor placement critically affects decoupling effectiveness:

Via Inductance Impact: L_via = 0.2h[ln(4h/d) + 1] nH

For 0.3mm via in 1.6mm board: L_via = 0.2 × 1.6[ln(4×1.6/0.3) + 1] = 1.2nH

This via inductance can dominate total loop inductance, negating benefits of low-ESL capacitors.

Optimization Techniques:

- Place capacitors within 2mm of power pins

- Use multiple vias per capacitor terminal

- Implement via-in-pad for minimum inductance

- Route power on adjacent layers

- Maintain symmetry for differential noise cancellation

4. Managing Power Supply Noise and Interference

Power supply noise degrades system performance through multiple coupling mechanisms. Effective noise management requires understanding sources, coupling paths, and mitigation techniques.

Switching Noise Suppression

Switching regulators generate broadband noise with fundamental frequency at the switching rate and harmonics extending to hundreds of megahertz:

Input Filter Design:

- Differential mode filter: LC lowpass with f_c < f_sw/10

- Common mode choke: Reduces conducted emissions

- Y-capacitors: Provide return path for common-mode current

- Damping network: Prevents filter resonance

Output Filter Optimization: Second-stage LC filtering achieves additional 40dB/decade attenuation:

L = V_out × D × (1-D) / (ΔI × f_sw) C = ΔI / (8 × f_sw × ΔV)

For 3.3V output, 1A load, 1 MHz switching: L = 2.2μH, C = 22μF for 50mV ripple

Isolation Techniques

Sensitive analog and RF circuits require isolation from digital noise:

Physical Separation:

- Maintain >5mm spacing between domains

- Use separate power planes where possible

- Route sensitive signals away from switching nodes

- Implement guard rings around critical circuits

Filtering and Decoupling:

- Ferrite beads: 100Ω @ 100 MHz typical

- Pi-filters: >40dB attenuation above cutoff

- Feed-through capacitors: Excellent high-frequency performance

- Active filters: For ultra-low noise requirements

Ground Plane Management

Proper grounding prevents noise coupling while maintaining signal integrity:

Star Grounding Architecture:

- Single point connection between domains

- Minimizes ground loops

- Reduces common-impedance coupling

- Suitable for mixed-signal systems

Multipoint Grounding:

- Required for frequencies >1 MHz

- Provides low-impedance return paths

- Uses ground plane for shielding

- Implements via stitching for plane connections

5. Thermal Considerations in High-Power RF Designs

Thermal management directly impacts power design effectiveness, particularly for RF power amplifiers and high-current digital circuits.

Power Dissipation Analysis

Calculate total power dissipation including all sources:

RF Power Amplifier: P_dissipated = P_DC - P_RF = P_DC × (1 - η)

For 10W output at 40% efficiency: P_DC = 25W, P_dissipated = 15W

Voltage Regulator: P_dissipated = (V_in - V_out) × I_out + I_q × V_in

For 5V to 3.3V conversion at 2A: P_dissipated = 1.7 × 2 + 0.005 × 5 = 3.4W

Thermal Resistance Calculations

Junction temperature determines reliability and performance:

T_j = T_a + P × (R_jc + R_cs + R_sa)

Where:

- R_jc: Junction-to-case (from datasheet)

- R_cs: Case-to-sink (interface material)

- R_sa: Sink-to-ambient (heatsink)

Target T_j < 125°C for commercial, < 110°C for high reliability.

PCB Thermal Design

The PCB itself provides significant heat dissipation:

Thermal Via Arrays:

- Via diameter: 0.3-0.5mm typical

- Spacing: 1.0-1.5mm grid

- Thermal resistance: ~50°C/W per via

- Fill with thermally conductive material

Copper Spreading:

- 1 oz copper: 70°C/W per square

- 2 oz copper: 35°C/W per square

- Use maximum copper area available

- Connect to internal planes for spreading

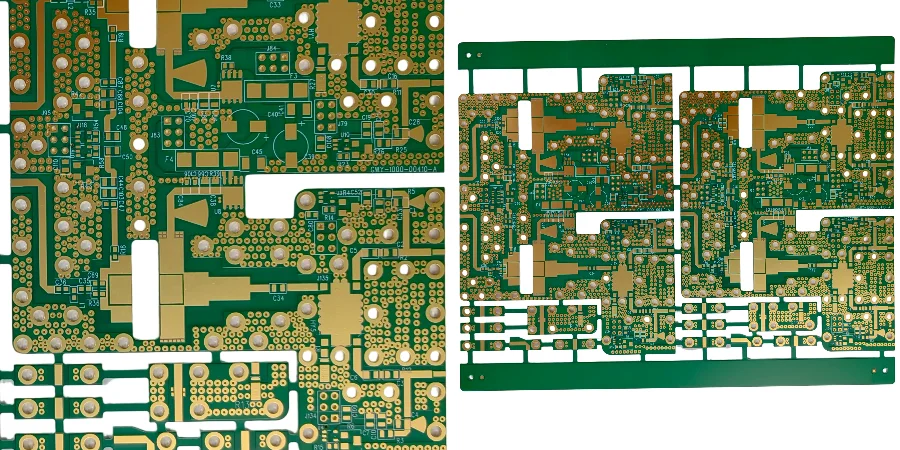

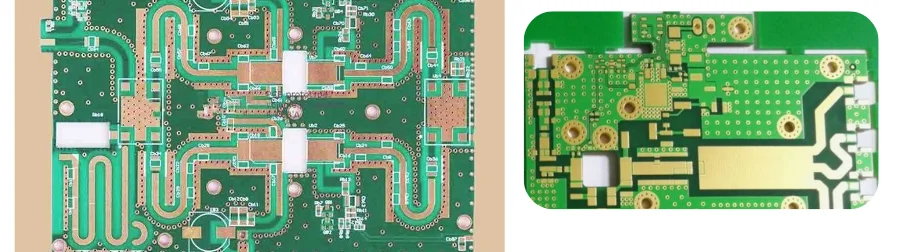

6. Why Choose HILPCB for High-frequency Power Design

HILPCB provides comprehensive power design solutions for demanding high-frequency applications:

- Design Expertise: PDN modeling and optimization for DC to 40 GHz

- Simulation Tools: Power integrity analysis using industry-standard software

- Manufacturing Capabilities: Heavy copper up to 6 oz, thermal management features

- Material Selection: Low-loss, thermally conductive substrates

- Testing Services: PDN impedance measurement, thermal imaging

- Application Experience: RF amplifiers, high-speed PCB, power converters

Our power design services have enabled:

- 5G base stations with 100W+ RF output

- High-speed servers with sub-1mΩ PDN impedance

- Automotive radar with -40°C to +150°C operation

- Satellite communications with >95% efficiency

- Test equipment with <1μV RMS noise

7. Frequently Asked Questions (FAQ)

Q1: How much decoupling capacitance do I need for my high-frequency design?

A: Target PDN impedance determines capacitance requirements. For digital circuits, use 0.1μF per power pin plus bulk capacitance of 10-100μF per amp of current. For RF, add 1-10nF capacitors near active devices. Use PDN analysis tools for precise values.

Q2: Should I use ferrite beads in high-frequency power supplies?

A: Ferrite beads effectively filter noise above 10 MHz but add DC resistance and can cause instability with fast load transients. Use them for isolating analog/RF sections but avoid them in high-current digital power paths. Always verify stability with beads installed.

Q3: How do I prevent power plane resonances?

A: Power plane resonances occur at frequencies where plane dimensions equal multiples of λ/2. Mitigation includes: using lossy dielectric materials, adding distributed decoupling, segmenting large planes, and implementing edge termination. Target first resonance above operating frequency.

Q4: What's the impact of via inductance on decoupling effectiveness?

A: Via inductance (typically 0.5-1.5nH) can dominate the total mounting inductance, limiting high-frequency effectiveness. Minimize by using multiple vias (inductance reduces as 1/n), shorter vias (thinner boards), and larger diameter vias. Consider via-in-pad for critical applications.

Q5: How do I design power distribution for 77 GHz automotive radar?

A: At 77 GHz, on-die decoupling dominates. Focus on providing clean DC with excellent low-frequency filtering (<100 MHz). Use dedicated LDOs for each RF block, implement star distribution to minimize coupling, and maintain die-to-board transition impedance below 50mΩ.

Q6: What causes voltage regulator oscillation in RF applications?

A: RF coupling into feedback networks causes oscillation. Prevention includes: shielding sensitive nodes, using feedforward capacitors for phase margin, routing feedback traces away from RF, and adding ferrite beads on sense lines. Always verify stability across temperature and load conditions.

Ready to Optimize Your High-frequency Power Design?

Our power integrity experts provide comprehensive PDN design and analysis for the most demanding RF and high-speed applications. Contact us for consultation on your next project.