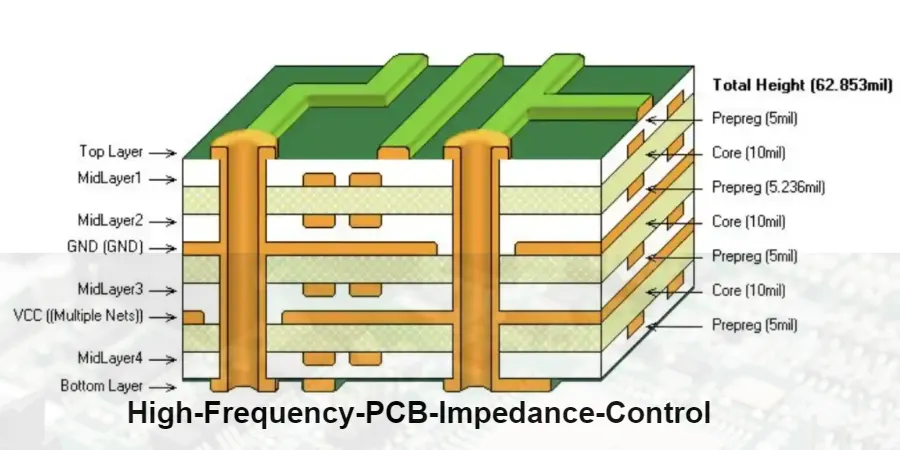

层叠层构成了每个 HF PCB 设计的基础,决定了信号完整性、功率传输和电磁性能。随着工作频率超过 10 GHz 且数据速率超过 25 Gbps,叠层设计对于系统成功变得越来越重要。优化良好的叠层可确保受控阻抗、最大限度地减少串扰、提供有效的屏蔽并实现可靠的制造。本综合指南探讨了设计高性能 PCB 叠层的原理、方法和实际考虑因素,以满足现代射频和高速数字系统的苛刻要求。

1. 叠层设计在高频PCB中的关键作用

层叠层设计直接影响高频PCB性能的各个方面。与叠层主要影响布线密度和成本的低频设计不同,高频应用需要仔细考虑电磁场分布、信号传播和供电网络。

在 1 GHz 以上的频率下,PCB 叠层决定了特性阻抗容差,典型目标为 ±5%,需要精确控制介电厚度和材料特性。信号完整性取决于保持一致的参考平面,中断会导致阻抗不连续,从而产生超过可接受限值的反射。层间串扰随频率呈指数级增长,因此适当的层分配和屏蔽对于实现 >40 dB 隔离要求至关重要。

叠层还定义了热管理功能,热通孔和铜分布会影响高功率射频放大器的结温。对于超过 10 层的 多层 PCB 设计,机械稳定性变得至关重要,需要平衡的结构以防止可能导致装配故障的翘曲。制造良率与叠层复杂性直接相关,因为腐蚀性尺寸会推动工艺能力并增加缺陷率。

2. 最佳性能的材料选择策略

为每一层选择合适的材料需要平衡电气性能、热性能、机械稳定性和成本。高频设计通常采用混合叠层,将优质射频材料与标准 FR4 相结合,用于非关键层。

高频衬底选项

对于承载频率高于 1 GHz 的信号层,低损耗材料变得必不可少:

罗杰斯 RO4000 系列在 40 GHz 下提供出色的性能:

- RO4003C:εr=3.38±0.05,Df=0.0027(10 GHz)

- RO4350B:εr=3.48±0.05,10 GHz 时 Df=0.0037

- 温度稳定,兼容FR4加工

- 费用:3-4×标准FR4

聚四氟乙烯基材料,实现终极性能:

- 罗杰斯 RT/硬质合金 5880:εr=2.20,Df=0.0009

- Taconic TLY-5:εr=2.20,Df=0.0009

- 卓越的稳定性,最低的损耗

- 成本:8-10×标准FR4

高级碳氢化合物陶瓷平衡性能和成本:

- I-Tera MT40 系统:εr=3.45,df=0.0031

- 松下 Megtron 6:εr=3.61,Df=0.004

- 无铅兼容,稳定至 20 GHz

- 费用:2-3×标准FR4

预浸料和芯材选择

预浸料的选择对阻抗控制和可靠性有重大影响:

- 将预浸料εr与芯材相匹配(±0.1公差)

- 用于精细特征的低流量预浸料

- 高 Tg (>170°C),用于无铅组装

- 可控树脂含量,确保厚度一致

芯材提供机械稳定性:

- 厚度公差±标准 10%,临界 ±5%

- 匹配的 CTE 以防止差异扩张

- 玻璃样式影响 εr 均匀性(首选涂抹玻璃)

3. 不同应用的叠层配置

不同的应用需要优化叠层配置,平衡性能要求和制造限制。

4 层高频叠层

简单的设计受益于经济高效的 4 层配置:

Layer 1: Signal/Components (50Ω microstrip)

Prepreg: 0.2mm RO4450F (εr=3.52)

Layer 2: Ground Plane

Core: 1.0mm FR4 (εr=4.4)

Layer 3: Power Plane

Prepreg: 0.2mm RO4450F

Layer 4: Signal (50Ω microstrip)

Total thickness: 1.524mm (60 mil)

优势:

- 低成本、标准加工

- 适用于 <6 GHz 的频率

- 简单的阻抗控制

- 适用于许多无线应用

局限性:

- 布线密度有限

- 适度的串扰隔离

- 可进行功率平面共振

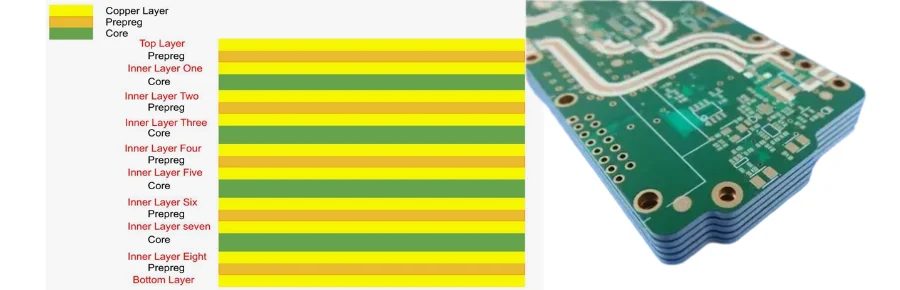

8 层高速数字叠层

复杂的 高速 PCB 设计需要更复杂的叠层:

L1: Signal (Microstrip)

0.1mm Prepreg

L2: Ground

0.2mm Core

L3: Signal (Stripline)

0.1mm Prepreg

L4: Signal (Stripline)

0.3mm Core

L5: Power

0.3mm Core

L6: Ground

0.1mm Prepreg

L7: Signal (Stripline)

0.2mm Core

L8: Signal (Microstrip)

Total: 1.6mm

好处:

- 多个布线层以提高密度

- 层间屏蔽性极佳

- 分布式电源/接地对

- 全程受控阻抗

高级毫米波叠加

毫米波应用需要专门的配置:

L1: RF Signal (77 GHz radar)

0.127mm RO3003 (εr=3.0)

L2: Ground

0.254mm RO4350B

L3: Digital/Power

0.360mm FR4

L4: Ground

0.360mm FR4

L5: Digital

0.254mm RO4350B

L6: Ground

0.127mm RO3003

L7: RF Signal

Total: 1.524mm

特征:

- 用于射频层的超低损耗材料

- 用于成本优化的混合结构

- 对称结构可防止翘曲

- 定义过孔背钻区域

4. 叠层设计中的阻抗规划和控制

要在所有信号层上实现一致的阻抗,需要在叠层设计过程中进行仔细规划。每种传输线类型(微带线、带状线和共面波导)都有必须满足的独特要求。

微带阻抗优化

外层的微带可轻松检修组件,但需要仔细控制:

目标:50Ω ±5%

- 根据介电高度计算走线宽度

- 考虑阻焊效应 (+2-3Ω)

- 考虑高频下的铜粗糙度

- 蚀刻因子补偿计划

RO4003C的计算示例:

- 介电高度:0.203mm(8密耳)

- 走线宽度:0.432 毫米(17 密耳)

- 实现阻抗:50.2Ω

带状线配置

Stripline 提供卓越的屏蔽和一致的阻抗:

好处:

- 无频散

- 更好的串扰隔离(提高 >6dB)

- 防止外部干扰

- 一致的εr(无空气接口)

设计注意事项:

- 平面之间的居中走线以实现对称

- 保持 2:1 的最小高宽比

- 考虑玻璃编织效果

- 仔细规划通过过渡

差分对实现

高速差分信号需要特别注意:

- 边耦合与宽边耦合布线

- 目标100Ω差分(50Ω奇模)

- 通过层转换保持耦合

- 配对内的匹配传播延迟

5. 电源和接地层策略

有效的配电和接地对于高频性能至关重要。叠层必须提供低阻抗电力传输,同时保持信号完整性。

电源/接地层配对

相邻的电源层和接地层会产生分布式电容:

电容计算: C = ε₀ × εr × A / d

对于间距为 0.1 毫米的 100 毫米× 100 毫米平面: C = 8.85 × 4.4 × 10,000 / 0.1 = 3.9nF

这提供了高频去耦,降低了电源噪声并提高了信号完整性。

平面分配策略

针对不同频率优化平面放置:

数字部分:紧密的电源/接地耦合

- 0.1mm 间距,用于 >1 GHz 工作

- 单层多电压域

- 带桥式电容器的分体式平面

射频部分:连续接地层

- RF 走线下无分裂

- 隔离防护环

- 板边缘的过孔围栏

混合信号:独立的模拟/数字接地

- 星点连接

- 用于HF隔离的铁氧体磁珠

- 跨分割仔细布线

通过叠层进行 EMI 控制

正确的叠层设计可显着降低电磁辐射:

- 在平面之间埋藏高速信号

- 对平面尺寸实施 20-H 规则

- 以λ/20的间隔添加缝合过孔

- 使用边缘电镀改善屏蔽

6. 为什么选择HILPCB进行高频PCB叠层设计

HILPCB 提供针对高频应用优化的全面叠层设计和制造服务:

- 专家咨询:射频和信号完整性工程师审查您的要求

- 材料库存:全系列高频层压板库存

- 仿真服务:预构建建模和阻抗预测

- 制造能力:2-40层,阻抗控制±3%

- 验证测试:TDR、横截面和可靠性测试

- 快速周转:24 小时叠加提案,5 天原型

我们的经验涵盖:

- 5G 基础设施和小型基站

- 汽车雷达 (24/77 GHz)

- 高速计算 (56 Gbps+)

- 航空航天和国防系统

- 测试和测量设备

7. 常见问题解答(FAQ)

**Q1:我的高频设计需要多少层? 答:取决于电路的复杂性和频率。简单的射频电路在 6 GHz 以下的 4 层上工作。复杂的数字+射频系统通常需要 8-12 层。在 20 GHz 以上,请考虑使用 6+ 层进行适当的屏蔽和布线。

**Q2:我应该在整个叠层中使用相同的材料吗? 答:不一定。仅在需要的地方(通常是外层和关键信号层)使用射频材料的混合叠层可以在保持性能的同时降低 40-60% 的成本。确保 CTE 匹配以防止可靠性问题。

**Q3:叠层如何影响阻抗容差? 答:叠层直接通过介电厚度和εr确定阻抗。更薄的电介质可提供更严格的阻抗控制,但需要更细的走线宽度。目标厚度公差为 ±10%,用于 ±5% 阻抗控制。

**Q4:不对称叠加有什么影响? 答:不对称叠层在装配过程中会导致翘曲,可能超过 0.75% 的弯曲/扭曲限制。它们还会造成不均匀的应力分布。除非绝对必要,否则始终使用对称叠加,然后实施补偿策略。

**Q5:如何最大限度地减少层间串扰? 答:垂直于相邻信号层布线,保持信号层之间的接地层,使用更薄的电介质与参考层更紧密地耦合,并实施适当的过孔屏蔽。敏感信号的目标隔离度为 >35dB。

**Q6:什么时候应该使用顺序层压? 答:对于具有堆叠或交错过孔的 HDI PCB 来说,顺序层压是必要的,从磁芯构建以创建复杂的过孔结构。它对于高密度设计至关重要,但会增加 20-30% 的制造成本。

**准备好优化您的 PCB 叠层了吗?

我们的工程团队专门为要求苛刻的射频和高速应用设计高性能叠层。就您的下一个项目获得专家咨询。