Die Leistungsintegrität im Design von Hochfrequenz-Leiterplatten ist für die Sicherstellung der Systemleistung ebenso wichtig geworden wie die Signalintegrität. Moderne HF-Systeme und digitale Hochgeschwindigkeitsschaltungen erfordern eine saubere, stabile Stromversorgung über Frequenzen von Gleichstrom bis zu mehreren zehn Gigahertz. Das Rauschen der Stromversorgung moduliert HF-Signale direkt, verursacht Jitter in digitalen Systemen und erzeugt elektromagnetische Störungen, die zu Fehlern bei der Einhaltung gesetzlicher Vorschriften führen können. In diesem umfassenden Leitfaden werden fortschrittliche Techniken für die Entwicklung robuster Stromverteilungsnetze (PDN) untersucht, die die strengen Anforderungen heutiger Hochfrequenzanwendungen erfüllen.

1. Verständnis der Leistungsanforderungen in Hochfrequenzsystemen

Hochfrequenzsysteme, die die HF-PCB-Technologie verwenden, stehen vor anspruchsvollen Herausforderungen bei der Stromversorgung. HF-Leistungsverstärker können ein Spitzen-zu-Mittelwert-Stromverhältnis von über 10:1 aufweisen, was eine schnelle Stromabgabe erfordert, um Spannungseinbrüche zu vermeiden. Prozessoren, die mit mehr als 1 GHz betrieben werden, erzeugen schnelle Stromtransienten, die eine extrem niedrige PDN-Impedanz erfordern. Bei diesen Geschwindigkeiten sind die Leistungsintegrität und die Signalintegrität eng miteinander verknüpft – kleine Welligkeiten, wie z. B. 50 mV, können die EVM des HF-Senders um mehrere Prozent verschlechtern oder Jitter in Hochgeschwindigkeitsverbindungen verursachen, was sich auf die Leistung und Zuverlässigkeit auswirkt.

Thermische Effekte erschweren das Design von HF-Leiterplatten zusätzlich. HF-Verstärker mit geringem Wirkungsgrad geben den größten Teil ihrer Leistung als Wärme ab und erzeugen Hotspots, die das Verhalten der Komponenten verändern. Temperaturänderungen können den Ausgang des Reglers, die passiven Werte und die Transistorvorspannung verändern, wodurch die Gefahr einer Instabilität besteht. Ein effektives Leistungsdesign für HF-Leiterplatten muss sowohl die elektrische Leistung als auch die thermische Kontrolle verwalten, um einen konsistenten Betrieb unter Hochfrequenz- und Hochlastbedingungen zu gewährleisten.

2. Architektur des Stromverteilungsnetzes (PDN)

Ein gut konzipiertes PDN bietet eine niedrige Impedanz über alle interessierenden Frequenzen bei gleichzeitiger Beibehaltung von Stabilität und Effizienz. Moderne PDN-Architekturen verwenden hierarchische Ansätze mit mehreren Regelungsstufen, die für unterschiedliche Frequenzbereiche optimiert sind.

Mehrstufige Regulierungsstrategie

Die primäre Regelstufe wandelt die Eingangsspannung (typischerweise 12-48 V) mit Hilfe von Schaltreglern, die für den Wirkungsgrad optimiert sind, in Zwischenschienen um:

Überlegungen zum Design des Schaltreglers:

- Schaltfrequenz: 500 kHz - 2 MHz typisch

- Ausgangswelligkeit: <50 mV Spitze-Spitze

- Einschwingverhalten: <10μs Einschwingzeit

- Effizienzziel: >90 % bei Volllast

- EMI-Management: Abschirmung und Filterung unerlässlich

Die Sekundärregelung sorgt für saubere Energie für empfindliche Stromkreise:

** Implementierung des Linearreglers:**

- Extrem geringes Rauschen: <10 μV RMS (10 Hz - 100 kHz)

- PSRR: >60dB bei 1 MHz

- Dropout-Spannung: <200mV für Effizienz

- Thermisches Design: Angemessener Kühlkörper erforderlich

Die Point-of-Load-Regelung (POL) platziert die Regler in der Nähe von Hochstromlasten:

- Minimiert Verteilungsverluste

- Reduziert den Spannungsabfall bei Transienten

- Ermöglicht eine unabhängige Spannungsoptimierung

- Vereinfacht die Stromüberwachung

Design und Optimierung von Power Plane

Leistungsebenen in mehrschichtigen PCB-Aufbauten dienen als Stromverteilungsnetze mit niedriger Induktivität:

** Berechnung der Ebenenkapazität:** C = ε₀ × εr × A/h

Für 100-mm- × 100-mm-Ebenen mit einem Abstand von 0,1 mm auf FR4: C = 8,85e-12 × 4,4 × 1e-2 / 1e-4 = 3,9nF

Diese verteilte Kapazität ermöglicht eine Hochfrequenz-Entkopplung oberhalb von 100 MHz, bei der diskrete Kondensatoren aufgrund der montierten Induktivität unwirksam werden.

Designrichtlinien für Flugzeugpaare:

- Minimaler Abstand von 0,1 mm für effektive Kapazität

- Verwenden Sie nach Möglichkeit Materialien mit hohem εr zwischen den Ebenen

- Vermeiden Sie Schlitze und Splits, die die Induktivität erhöhen

- Implementierung der 20-H-Regel zur Reduzierung der Kantenstrahlung

- Fügen Sie alle λ/20 Stitching-Durchkontaktierungen am Ebenenumfang hinzu

3. Entkopplungsstrategie für hochfrequente Anwendungen

Eine effektive Entkopplung erfordert eine sorgfältige Auswahl der Komponenten, die Platzierung und das Verbindungsdesign, um eine niedrige PDN-Impedanz über das gesamte Frequenzspektrum aufrechtzuerhalten.

Auswahl und Charakterisierung von Kondensatoren

Reale Kondensatoren weisen parasitäre Induktivitäten und Widerstände auf, die den Wirkungsgrad von Hochfrequenzen einschränken:

Impedanz vs. Frequenz: Z = R + j(ωL - 1/ωC)

Eigenresonanzfrequenz (SRF): f_SRF = 1 / (2π√(LC))

Oberhalb der SRF werden Kondensatoren induktiv und die Impedanz nimmt mit der Frequenz zu.

Typische Kondensatorparameter:

| Paket | Kapazität | ESL | SRF | Effektive Reichweite |

|---|---|---|---|---|

| Nr. 1206 | 10μF | 1,2 nH | 1,5 MHz | Gleichstrom - 1 MHz |

| Nr. 0805 | 1μF | 0,8 nH | 5,6 MHz | 100 kHz - 5 MHz |

| Nr. 0603 | 0,1 μF | 0,6 nH | 20 MHz | 1 MHz - 20 MHz |

| Nr. 0402 | 10nF | 0,4 nH | 80 MHz | 10 MHz - 80 MHz |

| Nr. 0201 | 1nF | 0,3 nH | 290 MHz | 50 MHz - 200 MHz |

Platzierungs- und Layoutoptimierung

Die Platzierung des Kondensators wirkt sich entscheidend auf die Entkopplungseffektivität aus:

Über Induktivitätsaufprall: L_via = 0,2 h[ln(4 h/d) + 1] nH

Für 0,3 mm Durchkontaktierung in 1,6 mm Platine: L_via = 0,2 × 1,6[ln(4×1,6/0,3) + 1] = 1,2 nH

Diese Via-Induktivität kann die Gesamtschleifeninduktivität dominieren, wodurch die Vorteile von Kondensatoren mit niedrigem ESL-Wert zunichte gemacht werden.

Optimierungstechniken:

- Platzieren Sie die Kondensatoren innerhalb von 2 mm von den Stromanschlüssen

- Verwenden Sie mehrere Durchkontaktierungen pro Kondensatoranschluss

- Implementierung von Via-in-Pad für minimale Induktivität

- Routing der Stromversorgung auf benachbarten Schichten

- Beibehaltung der Symmetrie für differentielle Geräuschunterdrückung

4. Umgang mit Rauschen und Interferenzen der Stromversorgung

Das Geräusch der Stromversorgung verschlechtert die Systemleistung durch mehrere Kopplungsmechanismen. Ein effektives Lärmmanagement erfordert das Verständnis von Quellen, Kopplungspfaden und Minderungstechniken.

Schalten der Rauschunterdrückung

Schaltregler erzeugen breitbandiges Rauschen mit einer Grundfrequenz bei einer Schaltrate und Oberschwingungen, die bis zu Hunderten von Megahertz reichen:

** Design des Eingangsfilters:**

- Gegentaktfilter: LC-Tiefpass mit f_c < f_sw/10

- Gleichtaktdrossel: Reduziert leitungsgebundene Emissionen

- Y-Kondensatoren: Bereitstellung eines Rückkanals für Gleichtaktstrom

- Dämpfungsnetzwerk: Verhindert Filterresonanzen

Optimierung des Ausgangsfilters: Die LC-Filterung der zweiten Stufe erreicht eine zusätzliche Dämpfung von 40 dB/Dekade:

L = V_out × D × (1-D) / (ΔI × f_sw) C = ΔI / (8 × f_sw × ΔV)

Für 3,3V Ausgang, 1A Last, 1 MHz Schaltung: L = 2,2 μH, C = 22 μF für 50 mV Welligkeit

Isolationstechniken

Empfindliche Analog- und HF-Schaltungen erfordern eine Isolierung von digitalem Rauschen:

Physische Trennung:

- Halten Sie einen Abstand von >5 mm zwischen den Domänen ein

- Verwenden Sie nach Möglichkeit separate Antriebsebenen

- Leiten Sie empfindliche Signale von den Schaltknoten weg

- Implementieren Sie Schutzringe um kritische Stromkreise

Filtern und Entkoppeln:

- Ferritperlen: 100 Ω @ 100 MHz typisch

- Pi-Filter: >40dB Dämpfung über Cutoff

- Durchgangskondensatoren: Exzellente Hochfrequenzleistung

- Aktive Filter: Für extrem geringe Geräuschanforderungen

Verwaltung der Bodenebene

Eine ordnungsgemäße Erdung verhindert eine Rauschkopplung bei gleichzeitiger Aufrechterhaltung der Signalintegrität:

Sternen-Erdungsarchitektur:

- Single-Point-Verbindung zwischen Domains

- Minimiert Masseschleifen

- Reduziert die Kopplung mit gemeinsamer Impedanz

- Geeignet für Mixed-Signal-Systeme

** Mehrpunkt-Erdung:**

- Erforderlich für Frequenzen >1 MHz

- Bietet niederohmige Rückwege

- Verwendet Massefläche zur Abschirmung

- Anbaugeräte über Stitching für ebene Verbindungen

5. Thermische Überlegungen bei Hochleistungs-HF-Designs

Das Wärmemanagement wirkt sich direkt auf die Effektivität des Leistungsdesigns aus, insbesondere bei HF-Leistungsverstärkern und digitalen Hochstromschaltungen.

Analyse der Verlustleistung

Berechnen Sie die Gesamtverlustleistung einschließlich aller Quellen:

** HF-Leistungsverstärker:** P_dissipated = P_DC - P_RF = P_DC × (1 - η)

Für eine Ausgangsleistung von 10 W bei einem Wirkungsgrad von 40 %: P_DC = 25 W, P_dissipated = 15 W

Spannungsregler: P_dissipated = (V_in - V_out) × I_out + I_q × V_in

Für die Umwandlung von 5 V in 3,3 V bei 2 A: P_dissipated = 1,7 × 2 + 0,005 × 5 = 3,4 W

Berechnungen des Wärmewiderstands

Die Sperrschichttemperatur bestimmt die Zuverlässigkeit und Leistung:

T_j = T_a + P × (R_jc + R_cs + R_sa)

Wo:

- R_jc: Junction-to-Case (aus Datenblatt)

- R_cs: Case-to-Sink (Interface-Material)

- R_sa: Senke zu Umgebungstemperatur (Kühlkörper)

Das Ziel T_j < 125 °C für gewerbliche < 110 °C für hohe Zuverlässigkeit.

Thermisches Design von Leiterplatten

Die Leiterplatte selbst sorgt für eine erhebliche Wärmeableitung:

Thermische Via-Arrays:

- Via-Durchmesser: 0,3-0,5 mm typisch

- Abstand: 1,0-1,5 mm Raster

- Thermischer Widerstand: ~50°C/W pro Via

- Füllung mit wärmeleitfähigem Material

Kupfer-Ausbreitung:

- 1 Unze Kupfer: 70 °C/W pro Quadrat

- 2 oz Kupfer: 35°C/W pro Quadrat

- Maximal verfügbare Kupferfläche nutzen

- Verbinden Sie sich mit internen Ebenen zum Verteilen

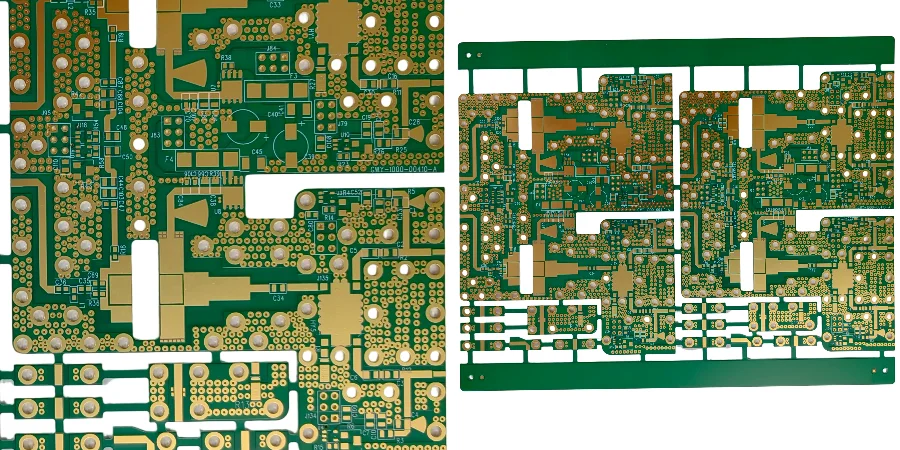

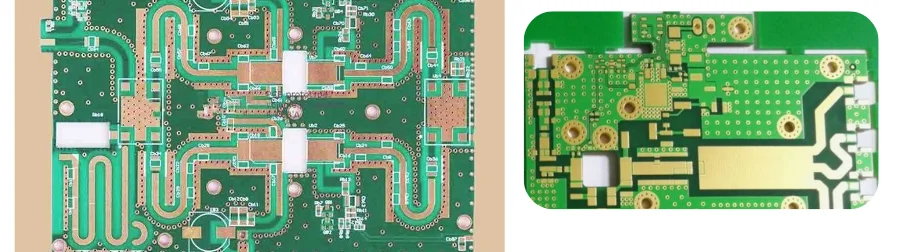

6. Warum sollten Sie sich für HILPCB für das Hochfrequenz-Leistungsdesign entscheiden?

HILPCB bietet umfassende Lösungen für das Power-Design für anspruchsvolle Hochfrequenzanwendungen:

- Design-Expertise: PDN-Modellierung und -Optimierung für DC bis 40 GHz

- Simulationswerkzeuge: Analyse der Netzintegrität mit branchenüblicher Software

- Fertigungskapazitäten: Schweres Kupfer bis zu 6 Unzen, Wärmemanagementfunktionen

- Materialauswahl: Verlustarme, wärmeleitende Substrate

- Prüfdienstleistungen: PDN-Impedanzmessung, Wärmebildtechnik

- Anwendungserfahrung: HF-Verstärker, Hochgeschwindigkeits-Leiterplatten, Leistungswandler

Unsere Power-Design-Dienstleistungen haben Folgendes ermöglicht:

- 5G-Basisstationen mit 100W+ HF-Ausgang

- Hochgeschwindigkeitsserver mit einer PDN-Impedanz von unter 1 mΩ

- Automotive-Radar mit -40°C bis +150°C Betrieb

- Satellitenkommunikation mit >95% Wirkungsgrad

- Prüfmittel mit <1μV RMS Rauschen

7. Häufig gestellte Fragen (FAQ)

F1: Wie viel Entkopplungskapazität benötige ich für mein Hochfrequenzdesign? A: Die PDN-Zielimpedanz bestimmt die Kapazitätsanforderungen. Verwenden Sie für digitale Schaltungen 0,1 μF pro Leistungspin plus eine Bulk-Kapazität von 10-100 μF pro Ampere Strom. Fügen Sie für HF 1-10nF-Kondensatoren in der Nähe aktiver Geräte hinzu. Verwenden Sie PDN-Analysewerkzeuge, um präzise Werte zu erhalten.

F2: Sollte ich Ferritperlen in Hochfrequenz-Netzteilen verwenden? A: Ferritperlen filtern effektiv Rauschen über 10 MHz, fügen jedoch einen Gleichstromwiderstand hinzu und können bei schnellen Lasttransienten zu Instabilität führen. Verwenden Sie sie zur Isolierung von Analog-/HF-Abschnitten, aber vermeiden Sie sie in digitalen Hochstrom-Strompfaden. Überprüfen Sie die Stabilität immer mit installierten Perlen.

F3: Wie verhindere ich Resonanzen im Leistungsbereich? A: Resonanzen in der Leistungsebene treten bei Frequenzen auf, bei denen die Ebenenabmessungen gleich einem Vielfachen von λ/2 sind. Zu den Abhilfemaßnahmen gehören: die Verwendung verlustbehafteter dielektrischer Materialien, das Hinzufügen einer verteilten Entkopplung, die Segmentierung großer Ebenen und die Implementierung eines Kantenabschlusses. Zielt auf die erste Resonanz oberhalb der Betriebsfrequenz ab.

F4: Welchen Einfluss hat die Via-Induktivität auf die Entkopplungseffektivität? A: Die Via-Induktivität (typischerweise 0,5-1,5 nH) kann die Gesamtinduktivität dominieren und den Hochfrequenzwirkungsgrad einschränken. Minimieren Sie durch die Verwendung mehrerer Durchkontaktierungen (Induktivität reduziert sich um 1/n), kürzeren Durchkontaktierungen (dünnere Platinen) und Durchkontaktierungen mit größerem Durchmesser. Ziehen Sie Via-in-Pad für kritische Anwendungen in Betracht.

F5: Wie entwerfe ich die Stromverteilung für 77-GHz-Automotive-Radar? A: Bei 77 GHz dominiert die On-Die-Entkopplung. Konzentrieren Sie sich auf die Bereitstellung von sauberem Gleichstrom mit hervorragender Niederfrequenzfilterung (<100 MHz). Verwenden Sie dedizierte LDOs für jeden HF-Block, implementieren Sie eine Sternverteilung, um die Kopplung zu minimieren, und halten Sie die Die-to-Board-Übergangsimpedanz unter 50 mΩ.

F6: Was verursacht Schwingungen von Spannungsreglern in HF-Anwendungen? A: Die HF-Einkopplung in Rückkopplungsnetzwerke verursacht Schwingungen. Zu den Vorbeugungsmaßnahmen gehören: Abschirmung empfindlicher Knoten, Verwendung von Feedforward-Kondensatoren für den Phasenrand, Verlegung von Rückkopplungsspuren weg von HF und Hinzufügen von Ferritperlen auf Messleitungen. Überprüfen Sie immer die Stabilität unter Temperatur- und Lastbedingungen.

Sind Sie bereit, Ihr Hochfrequenz-Leistungsdesign zu optimieren?

Unsere Experten für Leistungsintegrität bieten ein umfassendes PDN-Design und eine umfassende Analyse für die anspruchsvollsten HF- und Hochgeschwindigkeitsanwendungen. Kontaktieren Sie uns für eine Beratung zu Ihrem nächsten Projekt.