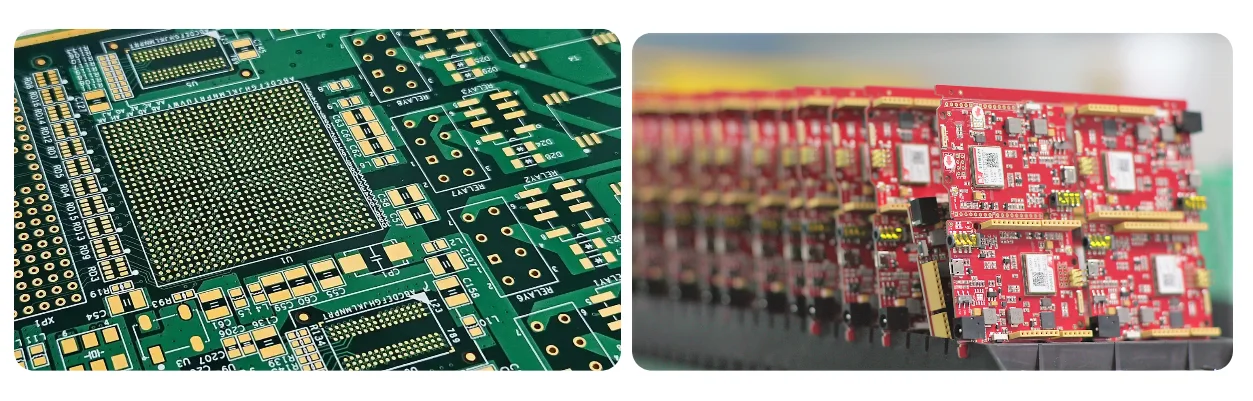

Mehrschichtige & HDI Leiterplattenfertigung | 4–64 Lagen, Impedanzkontrolle ±5% (plus/minus fünf Prozent)

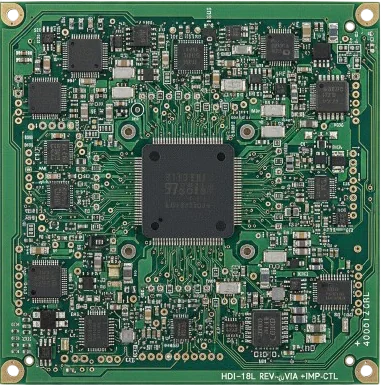

Hochdichte mehrschichtige und HDI Leiterplatten mit sequentieller Laminierung, gestapelten Mikrovias und Impedanzkontrolle ±5% (plus/minus fünf Prozent). Die Registrierung beträgt typischerweise ±15–25 μm (plus/minus fünfzehn bis fünfundzwanzig Mikrometer). Optimiert für Hochgeschwindigkeitsdesigns mit TDR-verifizierten Coupons.

Stackup-Architektur & Registrierungspräzision

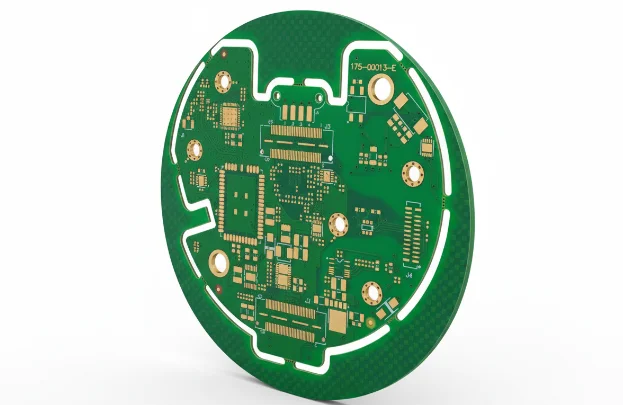

Optische/Röntgen-Ausrichtung für zuverlässige Hochlagen-BauweisenDesigns mit hoher Lagenzahl erfordern Stackups, die Signalintegrität, Stromverteilung und Herstellbarkeit ausbalancieren. Unser Ingenieurteam korreliert Feldlöser-Simulationen mit kontrollierten Impedanz-Stackups und Testcoupons, um Differenzziele bei 85/90/100 Ω innerhalb von ±5% (plus/minus fünf Prozent) zu halten. Optische Registrierung und Röntgenziele erreichen eine Schicht-zu-Schicht-Ausrichtung typischerweise innerhalb von ±15–25 µm (plus/minus fünfzehn bis fünfundzwanzig Mikrometer), was die Via-Zuverlässigkeit über 20 Lagen hinaus schützt.

Materialoptionen reichen von standardmäßigem FR-4 bis zu verlustarmen Systemen für Hochgeschwindigkeits-PCB-Kanäle. Hybride Stackups platzieren hochwertige Dielektrika nur dort, wo sie benötigt werden, was oft die Materialkosten um 30–50% (dreißig bis fünfzig Prozent) senkt, während die Signalintegrität erhalten bleibt. Für dichte Verbindungen reduzieren HDI-PCB-Architekturen mit Any-Layer-Mikrovias die Lagenzahl ohne Leistungseinbußen.

Kritisches Risiko: Inkonsistenter Dielektrika-Fluss oder asymmetrische Laminierung können Z-Achsen-CTE-Spannung, harzarme Hohlräume oder leitende anodische Filament (CAF)-Wachstum zwischen den Schichten verursachen – häufige Fehlerquellen in Mehrlagenplatinen über 16–20 Lagen.

Unsere Lösung: Wir setzen Laminierungsprozesskontrolle mit Presszyklusüberwachung, Harzfluss-SPC und Vakuumentgasung ein, um gleichmäßige Dielektrika-Füllung zu gewährleisten. Jeder Aufbau wird mit TMA-Expansionsdaten und Querschnittsinspektion validiert, um die Z-Achsen-Zuverlässigkeit zu bestätigen. Stackup-Symmetrie und Kupferbalance minimieren Verzug, während Signalintegritätsmodellierung Impedanz- und Verlustvorhersagen mit gemessenen Coupondaten abstimmt.

Für mission-kritische Systeme – Telekommunikations-Backplanes, Verteidigungs- oder Automobilsteuereinheiten – erweitern unsere Backplane-PCB-Plattformen die Mehrlagenzuverlässigkeit auf über 40 Lagen mit kontrollierten Harzaushärtungsprofilen und Pressfit-Toleranzvalidierung. Entdecken Sie weitere thermische und mechanische Leitlinien in thermisches Management im PCB-Design.

- Lagenanzahl bis zu 64 (vierundsechzig)

- Registrierungsgenauigkeit typischerweise ±15–25 μm

- Mikrovia-Seitenverhältnis unter 1:1 (eins zu eins)

- Impedanztoleranz ±5% erreichbar

- CAF-Minderung und Harzsysteme mit Td >340 °C (größer als dreihundertvierzig)

- Verzugskontrolle typischerweise <0,75% (weniger als null Komma sieben fünf Prozent)

🚀 Schnelle Angebotsanfrage

📋 Vollständige Fähigkeiten erhalten

Sequenzielle Laminierung & Via-Technologien

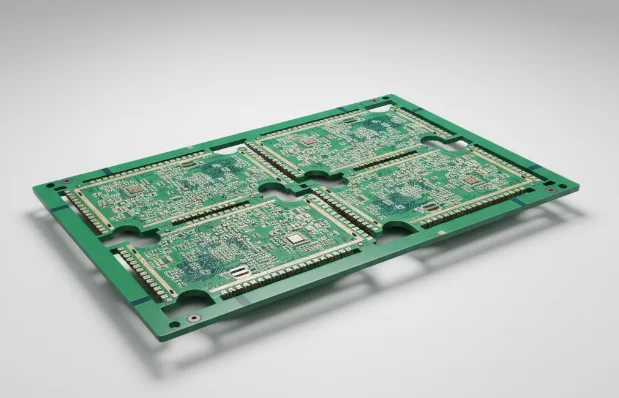

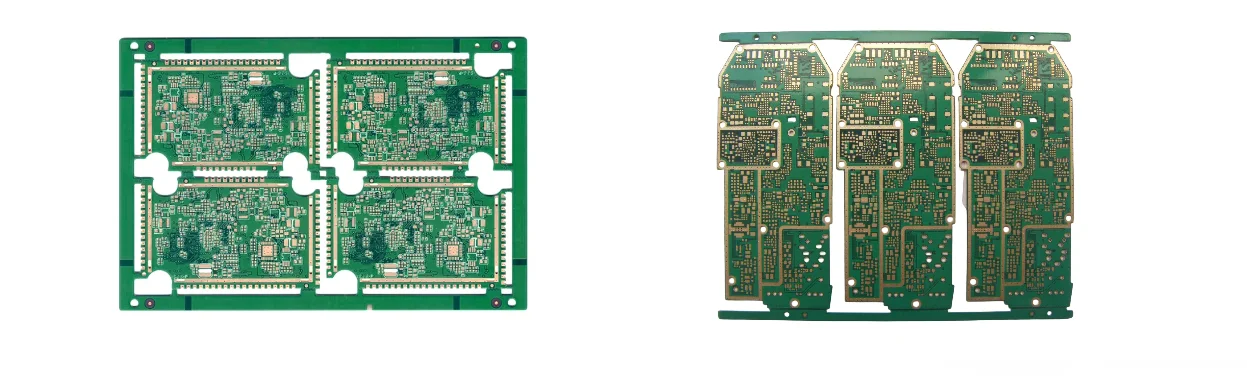

Mehrstufiger Aufbau mit umfassender ProzessüberprüfungSequenzielle Laminierung ermöglicht Verdrahtungsdichten, die mit herkömmlichen Aufbauten nicht erreichbar sind. Jeder Zyklus verwendet gestuften Druck/Temperatur mit typischerweise 10–20% (zehn bis zwanzig Prozent) Harzfluss, um die dielektrische Dicke für die Impedanz zu stabilisieren. UV-Laser-Mikrovias, üblicherweise 75–125 μm (fünfundsiebzig bis einhundertfünfundzwanzig Mikrometer), werden tiefenkontrolliert innerhalb ±5 μm und entschmiert für saubere Metallisierung. Via-Füllungen umfassen nichtleitendes Harz (planarisiert ±5 μm) oder Kupferfüllung für ~10× (zehnmal) thermische/elektrische Leitung in Strompfaden—siehe fortgeschrittene Via-Technologien.

Inline AOI erkennt Innenlagenmerkmale bis zu 25 μm; Röntgen überprüft die Registrierung; TDR auf Coupons validiert die Impedanz vor der Freigabe. IST (Interconnect Stress Test) Zyklen typischerweise 200–500 (zweihundert bis fünfhundert) überprüfen die Robustheit; Mikroschnitte bestätigen ≥20 μm (größer oder gleich zwanzig Mikrometer) Fassungskupfer. Für Langstrecken-Backplanes, koordinieren Sie mit Backplane PCB Teams über Backdrill- und Steckerstrategie.

- Mikrovia-Durchmesser 75–125 μm üblich

- Kupfergefüllte Mikrovias für 10× thermischen Gewinn

- IST 200–500 Zyklen (zweihundert bis fünfhundert)

- Mindestfassungskupfer 20 μm (zwanzig Mikrometer)

- Ionische Kontamination ≤1.56 μg/cm² (kleiner oder gleich eins Komma fünf sechs)

- Prozess Cpk typischerweise ≥1.33 (größer oder gleich eins Komma drei drei)

Mehrschichtige & HDI PCB Technische Spezifikationen

Umfassende Fähigkeiten für komplexe Hochgeschwindigkeits-/Hochdichte-Designs

| Parameter | Standardfähigkeit | Erweiterte Fähigkeit | Standard |

|---|---|---|---|

Layer Count | 4–12 Schichten (vier bis zwölf) | Bis zu 64 Schichten (bis zu vierundsechzig) | IPC-2221 |

Base Materials | FR-4 Tg 150–180 °C (einhundertfünfzig bis einhundertachtzig) | Megtron/Rogers/Isola niedriger Verlust | IPC-4101 |

Board Thickness | 0.6–3.2 mm (null Komma sechs bis drei Komma zwei) | Bis zu 8.0 mm (bis zu acht) | IPC-A-600 |

Copper Weight | 0.5–2 oz (siebzehn bis siebzig Mikrometer) | Bis zu 4 oz (bis zu vier) | IPC-4562 |

Min Trace/Space | 75/75 μm (3/3 mil; fünfundsiebzig mal fünfundsiebzig) | 25/25 μm (1/1 mil; fünfundzwanzig mal fünfundzwanzig) | IPC-2221 |

Min Hole Size | 0.15 mm (sechs mil) mechanisch | 0.05 mm (zwei mil) Laser | IPC-2222 |

Via Technology | Durchkontaktierung, blinde/vergrabene | Mikrovias, gestapelte Vias, Via-in-Pad | IPC-6012 |

Max Panel Size | 571.5 × 609.6 mm | 571.5 × 1200 mm | Manufacturing capability |

Impedance Control | ±10% (plus/minus zehn Prozent) | ±5% (plus/minus fünf Prozent) | IPC-2141 |

Surface Finish | ENIG, OSP, Immersionsilber | ENEPIG, Hart-/Weichgold | IPC-4552/4556 |

Quality Testing | 100% E-Test, AOI | Impedanz (TDR), Röntgen, Mikroschnitt | IPC-9252 |

Certifications | ISO 9001, UL, RoHS/REACH | IATF 16949, AS9100, ISO 13485 | Industry standards |

Lead Time | 5–7 Tage (fünf bis sieben) | 3 Tage Express (drei Tage) | Production schedule |

Bereit, Ihr PCB-Projekt zu starten?

Ob Sie einfache Prototypen oder komplexe Produktionsläufe benötigen, unsere fortschrittlichen Fertigungskapazitäten gewährleisten überlegene Qualität und Zuverlässigkeit. Erhalten Sie Ihr Angebot in nur 30 Minuten.

Signalintegritätsdesign & Via-Strategie

Halten Sie den Abstand von Differenzialpaaren auf ~2× (zweimal) der Leiterbahnbreite und platzieren Sie Erdungs-Via-Zäune innerhalb von ~1× (einmal) des Via-Durchmessers für Rückstrompfadkontinuität über 1 GHz (ein Gigahertz). Rückgebohrte Stummel auf <10 mil (weniger als zehn mil) für Verbindungen über 10 Gbps (zehn Gigabit pro Sekunde). Stromversorgungsebenen-Trennungen müssen Rückströme erhalten; die klassische 20H-Regel kann Kantenstrahlung für EMC reduzieren. Unser DFM-Review validiert diese vor der Freigabe.

- Dk/Df-Stabilitätsprüfungen von −40 bis +125 °C (minus vierzig bis plus einhundertfünfundzwanzig)

- Via-Stummel-Resonanzprüfung über 5 GHz

- Thermische Entlastung für Starkkupferebenen

- ICT-Zugang mit Ziel ≥95% (größer oder gleich fünfundneunzig Prozent)

Kompletter Prozessfluss mit Qualitätssicherungspunkten

Innenlagenabbildung auf 75 μm (fünfundsiebzig Mikrometer) Standard und 25 μm (fünfundzwanzig) fortgeschritten. AOI deckt 100% der Innenlagen ab; Laminierung verwendet Vakuumpressen, die 185–195 °C (einhundertfünfundachtzig bis einhundertfünfundneunzig) erreichen, mit abgestuftem Druck, um Harzmangel zu vermeiden. Nachlaminierungs-Röntgen bestätigt ±15–25 μm Ausrichtung. Mechanisches Bohren verwendet 300k RPM-Spindeln; Galvanisierung baut 25–35 μm (fünfundzwanzig bis fünfunddreißig) in Bohrungen auf. Für HDI-Iterationen wiederholen sich Laminierungs-/Bohrzyklen mit Metrologie in jeder Phase.

Tests umfassen Fliegende-Sonde/Fixture-E-Test, TDR-Impedanzkorrelation, Mikroschnitte und IST. Daten sind mit Losbegleitern verknüpft und werden für 7–10 Jahre (sieben bis zehn Jahre) für Automobil-/Luftfahrtprogramme aufbewahrt. Für System-Level-Builds und Gehäuse siehe Box Build Assembly.

Impedanzkontrolle mit feldgeprüfter Modellierung

Randcoupons unterziehen sich TDR mit ±2 Ω (plus/minus zwei Ohm) typischer Genauigkeit, um Solver-Vorhersagen zu validieren. Standard FR-4 Df ~0,015–0,020 bei 1 GHz (ein Gigahertz) gegenüber Low-Loss 0,002–0,005 erweitert die Kanallänge. Glattes Kupfer (Rz <2 μm) verbessert Einfügedämpfung ~10–20% (zehn bis zwanzig Prozent) über 5 GHz. Siehe unsere Impedanzkontrolle Methode und High-Speed-Co-Design mit High-Speed-PCB.

Zuverlässigkeitsvalidierung & SPC-Überwachung

Thermische Zyklen −40↔+125 °C (minus vierzig bis plus einhundertfünfundzwanzig) für 500–1000 Zyklen mit Widerstandsdrift <10% (weniger als zehn Prozent). HAST 130 °C/85% RH prüft Feuchtigkeitsrisiken; SIR bestätigt ≥10^8 Ω (größer oder gleich eins mal zehn hoch acht Ohm). SPC verfolgt Ausrichtung, Lochposition, Plattierungsdicke und Impedanz; Erstmuster bestätigen typischerweise Abmessungen ±0,05 mm und Impedanz innerhalb ±5%.

Anwendungsspezifische Implementierungsstrategien

Telekommunikation/Datenkommunikation: 24–32 Lagen mit Low-Loss-Dielektrika und Rückbohrung für 25+ Gbps.

Luftfahrt/Verteidigung: IPC Klasse 3 Dokumentation und erweiterte Losaufbewahrung.

Industrie/Stromversorgung: 2–4 oz Ebenen; kombinieren Sie nach Bedarf mit Heavy-Copper-PCB. Für Langstrecken-Chassis koordinieren Sie mit Backplane-PCB.

Technische Absicherung & Zertifizierungen

Erfahrung: Volumenmultilayer-/HDI-Aufbauten mit typischer Registrierung von ±15–25 μm und durch Coupons verifizierter Impedanz.

Expertise: Sequenzielle Laminierung, Mikrovia-Füllung, Backdrill-Steuerung und Cpk ≥1,33 (größer oder gleich eins Komma drei drei).

Autorität: Hergestellt nach IPC-6012 Klasse 3; siehe IPC Klasse 3 Hinweise.

Verlässlichkeit: MES-Rückverfolgbarkeit (von Charge bis zur Einheit) mit TDR/IST/Mikroschnitt-Berichten auf Anfrage.

- Kontrollen: Harzfluss, Dielektrikumsdicke, Bohrungsregistrierung

- Rückverfolgbarkeit: Digitaler Traveler und Chargenberichte

- Validierung: TDR, IST, Querschnitte, ionische und SIR

Häufig gestellte Fragen

How many layers can you reliably manufacture?

Which via options are recommended for high speed?

How is impedance verified in production?

Which materials should I choose for 10–28+ Gbps?

Do you support box-level builds after fabrication?

Erleben Sie Fertigungsexzellenz

Fortschrittliche Fertigungsprozesse gewährleisten, dass jede PCB den höchsten Qualitätsstandards entspricht. Erhalten Sie sofort Ihr individuelles Angebot.