Fabrication de PCB HDI | Microvias de 50–75 μm, Any-Layer, VIPPO | IATF 16949

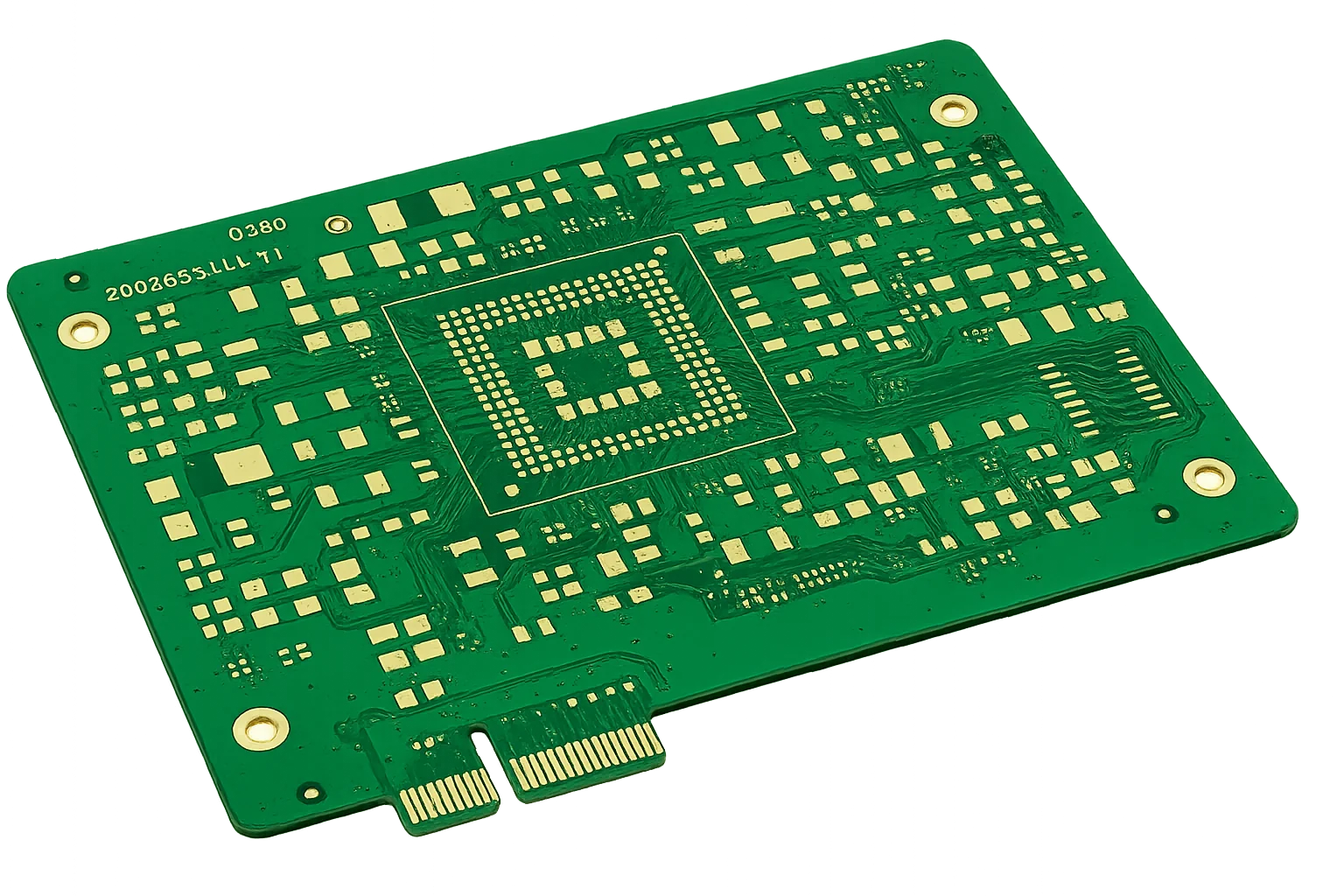

Circuits imprimés à interconnexion haute densité (HDI) avec microvias laser de 50–75 μm (cinquante à soixante-quinze micromètres), architectures 1+N+1 à any-layer, via-in-pad plaqué (VIPPO) et empilements à faible perte pour 10–56 Gbps (dix à cinquante-six gigabits par seconde). Contrôle d'impédance ±5 % (plus ou moins cinq pour cent) avec validation TDR. Délai rapide de 7 jours (sept jours) disponible.

Sélection de la technologie HDI et ingénierie de la valeur

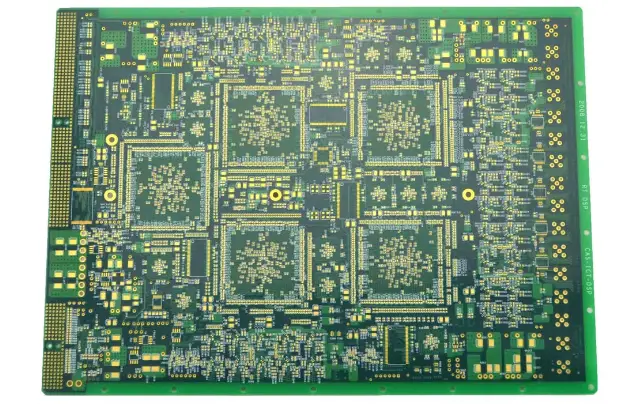

Architecture d'empilement pour un équilibre densité-performanceL'adoption de l'HDI commence lorsque le pas des BGA tombe en dessous de 0,8 mm (zéro virgule huit millimètres) ou que le nombre de couches dépasse les limites économiques. Nous évaluons trois nœuds de décision : la hauteur d'empilement des microvias (généralement limitée à deux niveaux pour la fiabilité), les cycles de stratification séquentielle (1+N+1 contre 2+N+2 coût/bénéfice), et les transitions de matériaux lorsque les fréquences de fonctionnement dépassent 5–8 GHz (cinq à huit gigahertz). Grâce à une optimisation systématique de la construction, l'épaisseur totale est généralement réduite de 25–40 % (vingt-cinq à quarante pour cent) tout en maintenant la fiabilité IPC-6012 Classe 3.

Les microvias laser de 50–75 μm (cinquante à soixante-quinze micromètres) avec un rapport d'aspect ≤1:1 (inférieur ou égal à un pour un) permettent un via-in-pad fanout, réduisant l'inductance parasite d'environ 40–60 % (environ quarante à soixante pour cent) par rapport au routage en os de chien. Pour les paires différentielles >10–12 Gbps (supérieur à dix à douze gigabits par seconde), des interconnexions plus courtes préservent les marges de l'œil et réduisent le décalage du signal. Pour une corrélation détaillée entre la conception des vias et les tests, consultez notre guide contrôle d'impédance et notre étude sur la fiabilité des microvias.

Risque critique : Un empilement excessif de microvias, un remplissage de résine médiocre ou une stratification déséquilibrée peuvent provoquer des vides, des fissures de barillet et la formation de filaments anodiques conducteurs (CAF) lors de contraintes thermiques. Un sur-perçage ou des rapports d'aspect élevés augmentent également le risque de défaillance à l'interface via-capture.

Notre solution : Nous appliquons les normes de fiabilité des microvias IPC-6016 et IPC-6012 Classe 3. Chaque structure d'empilement est simulée pour l'expansion en axe z, remplie et planarisée à l'aide d'un placage de cuivre sous vide. L'analyse en coupe transversale et les tests de contrainte d'interconnexion (IST) confirment l'intégrité des vias empilés et un CPK de placage ≥ 1,33 (supérieur ou égal à un virgule trois trois). Pour les conceptions ultra-denses, les empilements hybrides combinent des circuits imprimés multicouches et des circuits imprimés backplane pour un équilibre entre routage et distribution d'alimentation.

- Diamètre des microvias : 50–75 μm (cinquante à soixante-quinze micromètres), rapport d'aspect ≤1:1 (inférieur ou égal à un pour un)

- Stratification séquentielle : configurations 1+N+1 à travers toutes les couches

- VIPPO avec une profondeur de fossette <10 % (inférieure à dix pour cent) de l'épaisseur du plot

- Contrôle du décalage des paires différentielles à ±5 ps (plus/moins cinq picosecondes) dans les configurations optimisées

- Empilements hybrides avec un Df faible de 0,005–0,012 (zéro virgule zéro zéro cinq à zéro virgule zéro un deux) sur les couches critiques

- Contrôle du gauchissement ≤0,7 % (inférieur ou égal à zéro virgule sept pour cent) pour les BGA de grande taille

🚀 Demande de Devis Rapide

📋 Obtenir Capacités Complètes

Contrôle et Validation du Processus de Construction Séquentielle

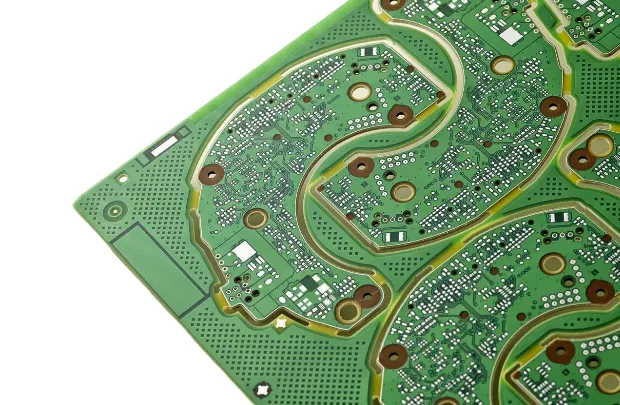

Précision d'alignement grâce à une vérification multi-étapesLes constructions multi-cycles maintiennent l'alignement des couches à ±25–50 μm (plus ou moins vingt-cinq à cinquante micromètres). Le laser UV-YAG à 355 nm (trois cent cinquante-cinq nanomètres) assure une ablation uniforme sur les systèmes FR-4 haute Tg (170–180 °C — cent soixante-dix à cent quatre-vingts degrés Celsius) et à faible perte. La densité d'énergie est ajustée en fonction de Dk/Df pour éviter la carbonisation et préserver des parois latérales propres pour la métallisation.

Le remplissage en cuivre est choisi en fonction de la fiabilité : cuivre électrolytique pour les profils thermiques automobiles (−40 °C↔+125 °C — moins quarante à plus cent vingt-cinq degrés) et pâte conductrice pour les constructions grand public optimisées en coût. L'ingénierie CAM en pré-production utilise l'analyse par éléments finis pour prédire les contraintes de CTE au niveau des microvias. La stabilité dimensionnelle est vérifiée optiquement à cinq emplacements par panneau selon la norme IPC-2226 Niveau C.

- Lasers CO₂ et UV avec une précision de faisceau de ±10 μm (plus ou moins dix micromètres)

- Uniformité de la couche de départ sans électrolyse ±10% (plus ou moins dix pour cent)

- Vérification d'alignement par rayons X des vias empilés à une résolution de 5 μm (cinq micromètres)

- Test de stress d'interconnexion (IST) selon IPC-TM-650 2.6.26 qualifié

Matrice de Capacité et de Performance des PCB HDI

Fenêtres de processus optimisées pour un équilibre fiabilité-coût

| Paramètre | Capacité Standard | Capacité Avancée | Standard |

|---|---|---|---|

Layer Count | 4–30 couches (quatre à trente) | Jusqu'à 60+ couches (jusqu'à soixante plus, any-layer) | IPC-2226 |

Base Materials | FR-4 haute Tg, matériaux faible Dk/Df | Megtron 6/7, Isola I-Speed, Rogers RO4000 | IPC-4101 |

Board Thickness | 0.4–3.2 mm (zéro point quatre à trois point deux) | 0.2–6.0 mm (zéro point deux à six point zéro) | IPC-A-600 |

Min Trace/Space | 75/75 μm (3/3 mil; soixante-quinze par soixante-quinze micromètres) | 50/50 μm (2/2 mil; cinquante par cinquante micromètres) | IPC-2221 |

Min Hole Size (Laser) | 0.10 mm (4 mil; zéro point un zéro millimètres) | 0.05 mm (2 mil; zéro point zéro cinq millimètres) | IPC-2226 |

Via Technology | Blind/Buried, Microvias (1+N+1, 2+N+2) | Stacked/Staggered, VIPPO, Any-Layer | IPC-6012 |

Aspect Ratio (Microvia) | 0.8:1 (zéro point huit à un) | 1:1 (un à un) | IPC-2226 |

Max Panel Size | 500 × 400 mm (cinq cents par quatre cents millimètres) | 600 × 500 mm (six cents par cinq cents millimètres) | Manufacturing capability |

Impedance Control | ±10% (plus/moins dix pour cent) | ±5% (plus/moins cinq pour cent) avec TDR | IPC-2141 |

Surface Finish | HASL, ENIG, OSP, Immersion Silver | ENEPIG, Soft/Hard Gold, Selective OSP | IPC-4552/4556 |

Quality Testing | E-test, AOI, X-ray | 4-wire Kelvin, Cross-section, IST, HAST | IPC-9252 |

Certifications | ISO 9001, UL, RoHS | IATF 16949, ISO 13485, AS9100, MIL-PRF-31032 | Industry standards |

Lead Time | 7–15 jours (sept à quinze jours) | 24 heures (vingt-quatre heures) prototype rapide | Production schedule |

Prêt à démarrer votre projet PCB ?

Que vous ayez besoin de prototypes simples ou de productions complexes, nos capacités de fabrication avancées garantissent une qualité supérieure et une fiabilité. Obtenez votre devis en seulement 30 minutes.

Architecture d'empilement et intégration du système de matériaux

La progression de 1+N+1 à 2+N+2 se produit généralement lorsque les BGAs avec un pas de 0,8 mm (zéro virgule huit millimètre) dépassent 400–600 broches. Nous modélisons la résonance des vias autour de 0,25λ (un quart de longueur d'onde) près de 10 GHz (dix gigahertz) et déplaçons les réseaux critiques vers des chemins aveugles/back-drillés. Les transitions à faible perte (Df 0,009–0,012) sont justifiées une fois que le budget d'insertion-perte tombe en dessous de ~0,8–1,0 dB/pouce (environ zéro virgule huit à un virgule zéro décibels par pouce). Voir fabrication HDI et optimisation des vias aveugles.

La fiabilité des microvias empilés dépend d'un cuivre uniforme à travers un placage séquentiel. Nous visons ≥18–20 μm (supérieur ou égal à dix-huit à vingt micromètres) au niveau du barillet, vérifié par coupe transversale. Les empilements décalés améliorent la durée de vie en cycle thermique de 20–30% (vingt à trente pour cent) mais nécessitent plus d'espace. Le CTE de remplissage VIPPO est ajusté (≈45–55 ppm/°C — environ quarante-cinq à cinquante-cinq parties par million par degré Celsius) pour limiter la contrainte des joints de soudure ; le remplissage en cuivre est sélectionné lorsque la dissipation de chaleur par via dépasse ~2 W (environ deux watts).

Optimisation de la séquence de construction et fenêtres de processus

La préparation du noyau cible un retrait <0,05% (inférieur à zéro virgule zéro cinq pour cent). Chaque cycle SBU : stratification 175–190 °C (cent soixante-quinze à cent quatre-vingt-dix degrés Celsius), formation de vias laser avec des parois latérales de 70–80° (soixante-dix à quatre-vingts degrés), puis cuivre sans électrode + électrolytique. Le désmear utilise du permanganate ajusté pour minimiser la récession diélectrique tout en éliminant complètement le smear. Le Cpk du processus pour l'anneau annulaire et l'espacement des vias est maintenu ≥1,33 (supérieur ou égal à un virgule trois trois). Le placage par impulsion inverse atteint un pouvoir de projection >80% (supérieur à quatre-vingts pour cent). Détails dans notre guide HDI.

Le QA post-stratification inclut l'AOI jusqu'à 10 μm (dix micromètres), la tomographie par rayons X pour le rétrécissement des microvias, et les tests électriques (flying-probe/fixture). Le Kelvin à 4 fils vérifie la résistance à ±1 mΩ (plus/moins un milliohm) pour la détection des interconnexions marginales.

Performance haute vitesse grâce à l'impédance contrôlée

La réduction des moignons de vias et le couplage serré des plans améliorent la perte de retour. Pour les paires différentielles >10 Gbps (supérieures à dix gigabits par seconde), nous utilisons des architectures aveugles/back-drillées pour éliminer les moignons résonants. La sélection des matériaux se tourne vers les ultra-faibles pertes (Df 0,005–0,007) lorsque le produit dB/in-GHz approche des limites. Notre modélisation d'impédance utilise l'EM 3D pour les réseaux de vias et les transitions, atteignant une tolérance de production de ±5% (plus/moins cinq pour cent) avec corrélation par coupon. Le cuivre à profil bas (Rz <2 μm — inférieur à deux micromètres) réduit la perte conductrice de 15–20% (quinze à vingt pour cent). Les diélectriques de construction minces (50–75 μm) permettent une inductance de boucle PDN inférieure à 100 pH (cent picohenries).

Validation de fiabilité : Thermique, Humidité et IST

Cyclage thermique de −40 °C à +125 °C (moins quarante à plus cent vingt-cinq) avec des paliers de 15 minutes ciblant ≥1000 (supérieur ou égal à mille) cycles sans changement de résistance >10 % (supérieur à dix pour cent). L'IST induit un échauffement Joule pour détecter les défaillances naissantes (>500 cycles typiques à 150 °C — cent cinquante degrés Celsius). HAST 130 °C/85 % HR (cent trente degrés Celsius/quatre-vingt-cinq pour cent d'humidité relative) pendant 96 h (quatre-vingt-seize heures) valide la résistance à l'humidité.

Les coupes au MEB vérifient les grains de cuivre, l'adhésion et les vides ; l'acceptation IPC-A-600 Classe 3 inclut un plaquage d'enveloppe ≥5 μm (supérieur ou égal à cinq micromètres) et aucune fissure au genou. Propreté ionique ≤1,56 μg/cm² équivalent NaCl (inférieur ou égal à un virgule cinq six microgrammes par centimètre carré). Test CAF à 65 °C/88 % HR (soixante-cinq degrés Celsius/quatre-vingt-huit pour cent d'humidité relative) avec 100 VCC (cent volts continu) pendant ≥500 h (supérieur ou égal à cinq cents heures).

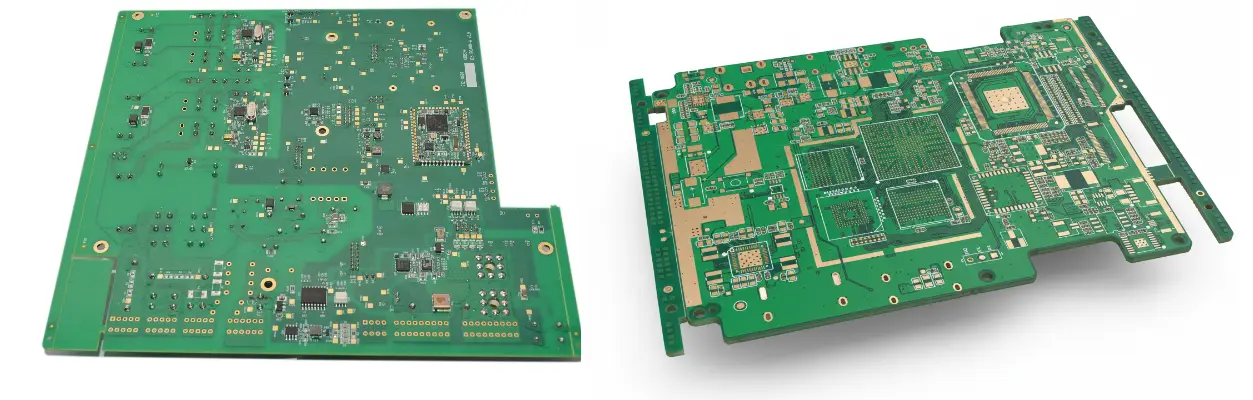

Stratégies HDI spécifiques aux applications

Automobile ADAS : 2+N+2 avec des couches RF à faible perte sélectives, perte d'insertion <0,3 dB/po (inférieur à zéro virgule trois décibels par pouce) à 77 GHz (soixante-dix-sept gigahertz), vias thermiques remplis de cuivre offrant θJB <2 °C/W (inférieur à deux degrés Celsius par watt).

Médical : miniaturisation any-layer avec documentation ISO 13485.

Datacom/5G : 25–56 Gbit/s (vingt-cinq à cinquante-six gigabits par seconde) SERDES ; voir Technologie PCB 5G.

Grand public : HDI sélectif uniquement là où la densité l'exige, réduisant les coûts de 15–25 % (quinze à vingt-cinq pour cent).

Assurance ingénierie et certifications

Expérience : programmes éprouvés en production de 1+N+1 à any-layer avec stratification à zones contrôlées et enregistrement LDI.

Expertise : TDR/VNA pour les modèles de transition de vias ; SPC sur le plaquage et l'enregistrement des perçages ; objectifs Cpk ≥1,33 (supérieur ou égal à un virgule trois trois).

Autorité : IPC Classe 3, IATF 16949, ISO 13485, AS9100 ; audits et documentation de bout en bout.

Fiabilité : MES suit les codes de lot et la sérialisation jusqu'aux données de test en ligne ; rapports IST/HAST disponibles pour la qualification.

- Contrôles de processus : épaisseur de plaquage, pression/température de stratification, énergie laser

- Traçabilité : sérialisation des unités, suivi des lots de composants, dossier numérique

- Validation : IST, HAST, examens de microsections, coupons d'impédance

Questions fréquentes

How do I choose between 1+N+1 and 2+N+2 HDI?

What limits stacked microvia reliability and how to mitigate?

When should I move to low-loss or ultra-low-loss materials?

Which factors drive HDI pricing the most?

Can you validate impedance to tight tolerances on HDI?

Découvrez l'Excellence de Fabrication

Des processus de fabrication avancés garantissent que chaque PCB répond aux normes de qualité les plus élevées. Obtenez instantanément votre devis personnalisé.