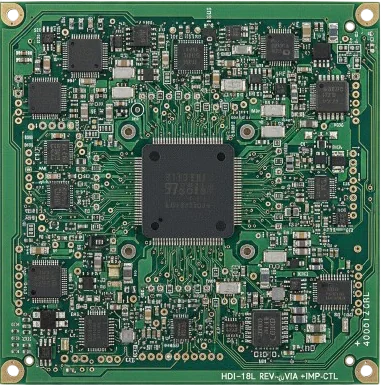

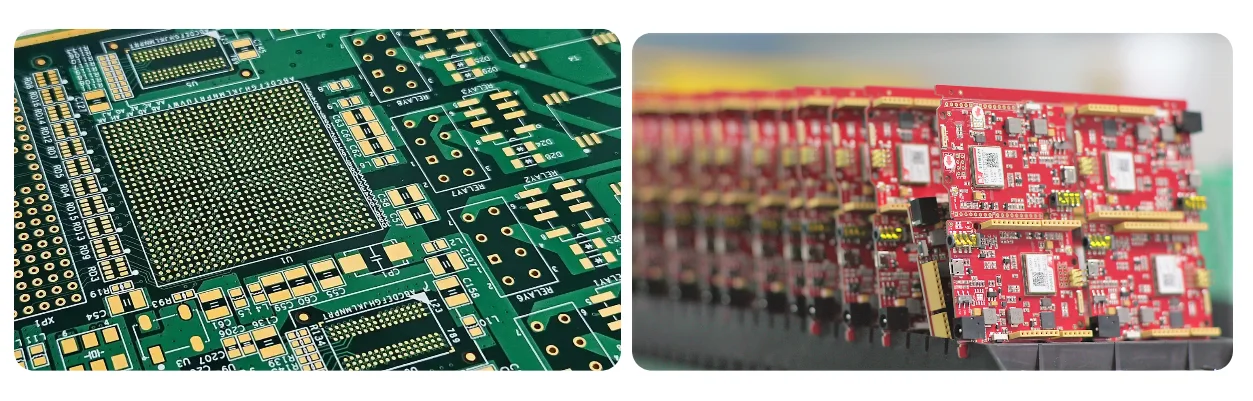

Fabrication de PCB multicouches et HDI | 4–64 couches, contrôle d'impédance ±5% (plus ou moins cinq pour cent)

PCB multicouches et HDI haute densité avec laminage séquentiel, microvias empilés et contrôle d'impédance ±5% (plus ou moins cinq pour cent). Enregistrement typiquement ±15–25 μm (plus ou moins quinze à vingt-cinq micromètres). Optimisé pour les conceptions haute vitesse avec coupons vérifiés par TDR.

Architecture d'empilement et précision d'enregistrement

Alignement optique/radiographique pour des constructions multicouches fiablesLes conceptions à grand nombre de couches exigent des empilements qui équilibrent l'intégrité du signal, la distribution d'alimentation et la fabricabilité. Notre équipe d'ingénieurs corrèle les simulations de résolution de champ avec des empilements à impédance contrôlée et des coupons de test pour maintenir les cibles différentielles à 85/90/100 Ω dans une plage de ±5% (plus ou moins cinq pour cent). L'enregistrement optique et les cibles radiographiques permettent un alignement intercouches généralement inférieur à ±15–25 µm (plus ou moins quinze à vingt-cinq micromètres), garantissant la fiabilité des vias au-delà de 20 couches.

Les options de matériaux vont du standard FR-4 aux systèmes à faible perte pour les canaux de PCB haute vitesse. Les empilements hybrides placent des diélectriques premium uniquement là où c'est nécessaire, réduisant souvent les coûts matériels de 30–50% (trente à cinquante pour cent) tout en préservant l'intégrité du signal. Pour les interconnexions denses, les architectures HDI PCB avec microvias any-layer réduisent le nombre de couches sans sacrifier les performances.

Risque critique : Un écoulement diélectrique inconstant ou une stratification asymétrique peut créer des contraintes de CTE en axe Z, des vides par manque de résine, ou une croissance de filaments anodiques conducteurs (CAF) entre les couches—points de défaillance courants dans les cartes multicouches au-delà de 16–20 couches.

Notre solution : Nous utilisons un contrôle de processus de stratification avec surveillance du cycle de pressage, SPC d'écoulement de résine et débullage sous vide pour assurer un remplissage diélectrique uniforme. Chaque construction est validée avec des données d'expansion TMA et une inspection en coupe transversale pour confirmer la fiabilité en axe Z. La symétrie d'empilement et l'équilibrage du cuivre minimisent la warpage, tandis que la modélisation d'intégrité du signal aligne les prédictions d'impédance et de perte avec les données mesurées sur coupons.

Pour les systèmes critiques—plans arrière de télécom, unités de contrôle de défense ou automobile—nos plateformes Backplane PCB étendent la fiabilité multicouche à plus de 40 couches avec des profils de cure de résine contrôlés et une validation de tolérance de press-fit. Explorez des conseils supplémentaires sur la gestion thermique et mécanique dans la gestion thermique en conception de PCB.

- Nombre de couches jusqu'à 64 (soixante-quatre)

- Précision d'enregistrement typiquement ±15–25 μm

- Rapport d'aspect des microvias inférieur à 1:1 (un pour un)

- Tolérance d'impédance ±5% réalisable

- Atténuation du CAF et systèmes de résine avec Td >340 °C (supérieur à trois cent quarante)

- Contrôle de la warpage typiquement <0.75% (inférieur à zéro virgule soixante-quinze pour cent)

🚀 Demande de Devis Rapide

📋 Obtenir Capacités Complètes

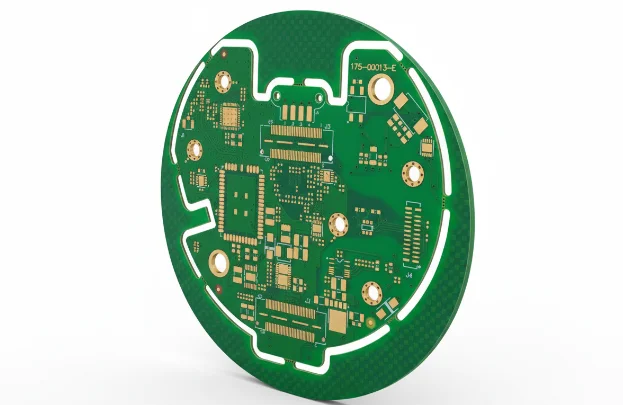

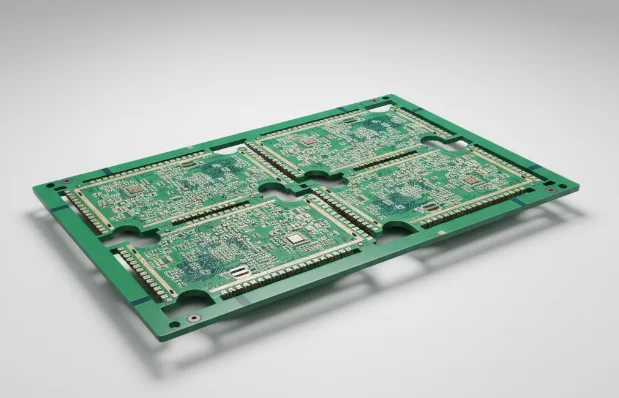

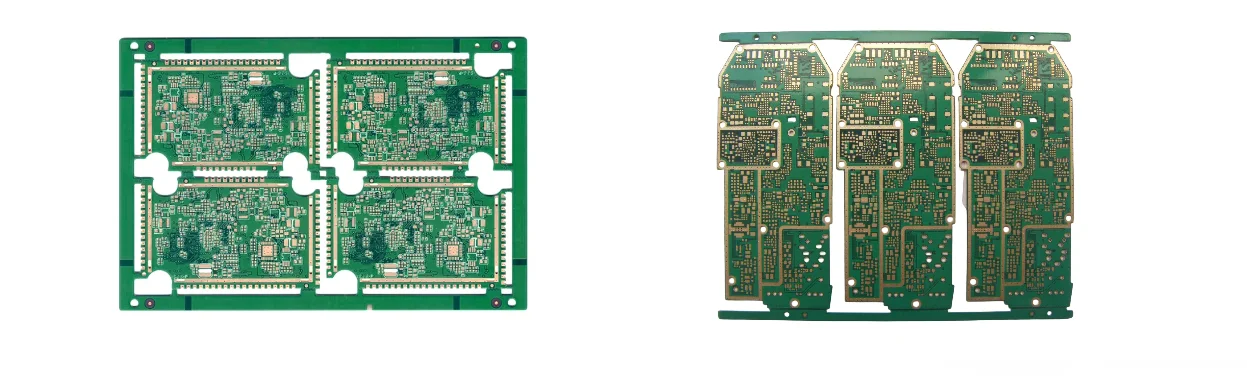

Stratification séquentielle et technologies de vias

Construction multi-étapes avec vérification complète des processusLa stratification séquentielle permet des densités de routage inaccessibles avec les constructions conventionnelles. Chaque cycle utilise une pression/température étagée avec un écoulement de résine typiquement de 10 à 20 % (dix à vingt pour cent) pour stabiliser l'épaisseur diélectrique pour l'impédance. Les microvias UV-laser couramment 75–125 μm (soixante-quinze à cent vingt-cinq micromètres) sont contrôlés en profondeur à ±5 μm et désmearés pour une métallisation propre. Les remplissages de vias incluent de la résine non conductrice (planarisée ±5 μm) ou un remplissage de cuivre pour ~10× (dix fois) la conduction thermique/électrique dans les chemins d'alimentation—voir technologies avancées de vias.

L'AOI en ligne détecte les caractéristiques des couches internes jusqu'à 25 μm ; les rayons X vérifient l'alignement ; le TDR sur les coupons valide l'impédance avant la libération. Le cyclage IST (Interconnect Stress Test) typiquement 200–500 (deux cents à cinq cents) vérifie la robustesse ; les microsections confirment ≥20 μm (supérieur ou égal à vingt micromètres) de cuivre de barillet. Pour les backplanes longue portée, coordonnez avec les équipes backplane PCB sur la stratégie de backdrill et de connecteurs.

- Diamètre des microvias 75–125 μm courant

- Microvias remplis de cuivre pour un gain thermique de 10×

- IST 200–500 cycles (deux cents à cinq cents)

- Cuivre de barillet minimum 20 μm (vingt micromètres)

- Contamination ionique ≤1.56 μg/cm² (inférieur ou égal à un point cinq six)

- Cpk du processus typiquement ≥1.33 (supérieur ou égal à un point trois trois)

Spécifications techniques des PCB multicouches et HDI

Capacités complètes pour les conceptions complexes haute vitesse/haute densité

| Paramètre | Capacité standard | Capacité avancée | Norme |

|---|---|---|---|

Layer Count | 4–12 couches (quatre à douze) | Jusqu'à 64 couches (jusqu'à soixante-quatre) | IPC-2221 |

Base Materials | FR-4 Tg 150–180 °C (cent cinquante à cent quatre-vingts) | Megtron/Rogers/Isola à faible perte | IPC-4101 |

Board Thickness | 0.6–3.2 mm (zéro virgule six à trois virgule deux) | Jusqu'à 8.0 mm (jusqu'à huit) | IPC-A-600 |

Copper Weight | 0.5–2 oz (dix-sept à soixante-dix micromètres) | Jusqu'à 4 oz (jusqu'à quatre) | IPC-4562 |

Min Trace/Space | 75/75 μm (3/3 mil; soixante-quinze par soixante-quinze) | 25/25 μm (1/1 mil; vingt-cinq par vingt-cinq) | IPC-2221 |

Min Hole Size | 0.15 mm (six mil) mécanique | 0.05 mm (deux mil) laser | IPC-2222 |

Via Technology | Trou traversant, aveugle/enterré | Microvias, vias empilés, via-in-pad | IPC-6012 |

Max Panel Size | 571.5 × 609.6 mm | 571.5 × 1200 mm | Manufacturing capability |

Impedance Control | ±10% (plus/moins dix pour cent) | ±5% (plus/moins cinq pour cent) | IPC-2141 |

Surface Finish | ENIG, OSP, Argent immersion | ENEPIG, Or dur/doux | IPC-4552/4556 |

Quality Testing | 100% Test électrique, AOI | Impédance (TDR), Rayon X, microsection | IPC-9252 |

Certifications | ISO 9001, UL, RoHS/REACH | IATF 16949, AS9100, ISO 13485 | Industry standards |

Lead Time | 5–7 jours (cinq à sept) | 3 jours express (trois jours) | Production schedule |

Prêt à démarrer votre projet PCB ?

Que vous ayez besoin de prototypes simples ou de productions complexes, nos capacités de fabrication avancées garantissent une qualité supérieure et une fiabilité. Obtenez votre devis en seulement 30 minutes.

Intégrité du signal & Stratégie de vias

Maintenir un espacement des paires différentielles ~2× (deux fois) la largeur de la trace et placer des barrières de vias de masse dans un rayon ~1× (une fois) le diamètre du via pour assurer la continuité du chemin de retour au-dessus de 1 GHz (un gigahertz). Les moignons résiduels doivent être percés à <10 mil (moins de dix mils) pour les liaisons dépassant 10 Gbps (dix gigabits par seconde). Les séparations des plans d'alimentation doivent préserver les courants de retour ; la règle classique des 20H peut réduire le rayonnement des bords pour la CEM. Notre revue DFM valide ces points avant la mise en production.

- Vérifications de la stabilité Dk/Df de −40 à +125 °C (moins quarante à plus cent vingt-cinq)

- Détection des résonances des moignons de vias au-dessus de 5 GHz

- Dégagement thermique pour les plans en cuivre épais

- Accès ICT ciblant ≥95% (supérieur ou égal à quatre-vingt-quinze pour cent)

Processus complet avec points de contrôle qualité

Imagerie des couches internes à 75 μm (soixante-quinze micromètres) standard et 25 μm (vingt-cinq) avancé. L'AOI couvre 100% des couches internes ; la stratification utilise des presses à vide atteignant 185–195 °C (cent quatre-vingt-cinq à cent quatre-vingt-quinze) avec une pression étagée pour éviter la pénurie de résine. La radiographie post-stratification confirme un positionnement de ±15–25 μm. Le perçage mécanique utilise des broches de classe 300k RPM ; le placage construit 25–35 μm (vingt-cinq à trente-cinq) dans les barils. Pour les itérations HDI, les cycles de stratification/perçage se répètent avec une métrologie à chaque étape.

Les tests incluent le test électrique par sonde volante/fixture, la corrélation d'impédance TDR, les microsections et l'IST. Les données sont liées aux dossiers de lot et conservées pendant 7–10 ans (sept à dix ans) pour les programmes automobile/aérospatial. Pour les assemblages au niveau système et les boîtiers, voir assemblage de boîtier.

Contrôle d'impédance avec modélisation validée sur le terrain

Les coupons de bord subissent un TDR avec une précision typique de ±2 Ω (plus/moins deux ohms) pour valider les prédictions du solveur. Le FR-4 standard Df ~0,015–0,020 à 1 GHz (un gigahertz) contre 0,002–0,005 pour les matériaux à faible perte étend la portée du canal. Le cuivre lisse (Rz <2 μm) améliore la perte d'insertion de ~10–20% (dix à vingt pour cent) au-dessus de 5 GHz. Voir notre méthode de contrôle d'impédance et la co-conception haute vitesse avec PCB haute vitesse.

Validation de la fiabilité & Surveillance SPC

Cycles thermiques −40↔+125 °C (moins quarante à plus cent vingt-cinq) pour 500–1000 cycles avec une dérive de résistance <10% (moins de dix pour cent). Le HAST 130 °C/85% HR détecte les risques d'humidité ; le SIR confirme ≥10^8 Ω (supérieur ou égal à un fois dix puissance huit ohms). Le SPC suit le positionnement, la position des trous, l'épaisseur du placage et l'impédance ; les premiers articles vérifient les dimensions typiquement ±0,05 mm et l'impédance dans ±5%.

Stratégies de mise en œuvre spécifiques à l'application

Télécoms/Datacom : 24–32 couches avec diélectriques à faible perte et perçage arrière pour 25+ Gbps.

Aérospatiale/Défense : Documentation IPC Classe 3 et conservation prolongée des lots.

Industriel/Puissance : Plans de 2–4 oz ; associez avec PCB en cuivre épais si nécessaire. Pour les châssis longue portée, coordonnez avec PCB backplane.

Assurance Ingénierie & Certifications

Expérience : constructions multicouches/HDI avec un enregistrement typiquement de ±15–25 μm et impédance vérifiée par coupon.

Expertise : laminage séquentiel, remplissage de microvia, contrôle de backdrill et Cpk ≥1,33 (supérieur ou égal à un point trois trois).

Autorité : construit selon IPC-6012 Classe 3 ; voir les notes IPC Classe 3.

Fiabilité : traçabilité MES (du lot au niveau unitaire) avec rapports TDR/IST/microsection disponibles sur demande.

- Contrôles : écoulement de la résine, épaisseur diélectrique, enregistrement de perçage

- Traçabilité : voyageur numérique et rapports de lot

- Validation : TDR, IST, coupes transversales, ionique et SIR

Questions fréquentes

Combien de couches pouvez-vous fabriquer de manière fiable ?

Quelles options de vias sont recommandées pour les hautes vitesses ?

Comment l'impédance est-elle vérifiée en production ?

Quels matériaux dois-je choisir pour 10–28+ Gbps ?

Prenez-vous en charge les constructions au niveau boîtier après la fabrication ?

Découvrez l'Excellence de Fabrication

Des processus de fabrication avancés garantissent que chaque PCB répond aux normes de qualité les plus élevées. Obtenez instantanément votre devis personnalisé.