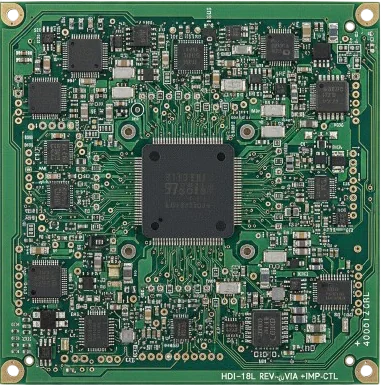

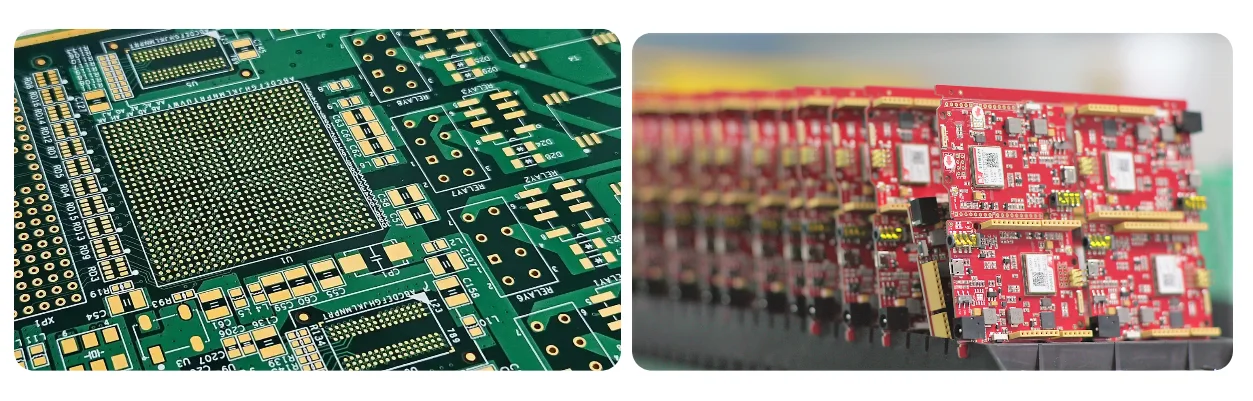

Производство многослойных и HDI печатных плат | 4–64 слоя, контроль импеданса ±5% (плюс/минус пять процентов)

Высокоплотные многослойные и HDI печатные платы с последовательным ламинированием, многоуровневыми микропереходами и контролем импеданса ±5% (плюс/минус пять процентов). Погрешность совмещения обычно ±15–25 мкм (плюс/минус пятнадцать-двадцать пять микрометров). Оптимизированы для высокоскоростных проектов с TDR-верифицированными тестовыми образцами.

Архитектура Stackup и точность регистрации

Оптическое/рентгеновское выравнивание для надежных многослойных конструкцийМногослойные конструкции требуют баланса между целостностью сигнала, распределением питания и технологичностью. Наша инженерная команда сопоставляет моделирование полевых решателей с контролируемыми импедансными структурами и тестовыми образцами для поддержания дифференциальных целей на уровне 85/90/100 Ω с точностью ±5% (плюс/минус пять процентов). Оптическая регистрация и рентгеновские метки обеспечивают межслойное выравнивание обычно в пределах ±15–25 µm (плюс/минус пятнадцать-двадцать пять микрометров), гарантируя надежность переходных отверстий для плат с более чем 20 слоями.

Доступные материалы варьируются от стандартного FR-4 до низкопотерьных систем для высокоскоростных PCB. Гибридные структуры размещают премиальные диэлектрики только там, где это необходимо, часто сокращая стоимость материалов на 30–50% (тридцать-пятьдесят процентов) без ущерба для целостности сигнала. Для плотных межсоединений HDI PCB с микропереходами любого слоя уменьшают количество слоев без потери производительности.

Критический риск: Неравномерное течение диэлектрика или асимметричная ламинация могут вызвать напряжение CTE по оси Z, пустоты из-за недостатка смолы или рост проводящих анодных нитей (CAF) между слоями — типичные точки отказа в многослойных платах с более чем 16–20 слоями.

Наше решение: Мы используем контроль процесса ламинации с мониторингом пресс-циклов, SPC течения смолы и вакуумным удалением пузырей для равномерного заполнения диэлектрика. Каждая сборка проверяется данными TMA и поперечными сечениями для подтверждения надежности по оси Z. Симметрия структуры и баланс меди минимизируют коробление, а моделирование целостности сигнала согласует прогнозы импеданса и потерь с данными тестовых образцов.

Для критически важных систем — телекоммуникационных backplane, оборонных или автомобильных блоков управления — наши платформы Backplane PCB расширяют надежность многослойных плат до 40+ слоев с контролируемыми профилями отверждения смолы и проверкой допусков пресс-посадки. Дополнительные рекомендации по тепловому и механическому управлению доступны в управлении тепловыми режимами в PCB.

- Количество слоев до 64 (шестьдесят четыре)

- Точность регистрации обычно ±15–25 μm

- Соотношение сторон микропереходов менее 1:1 (один к одному)

- Достижимый допуск импеданса ±5%

- Подавление CAF и смоляные системы с Td >340 °C (более трехсот сорока)

- Контроль коробления обычно <0.75% (менее нуля целых семидесяти пяти сотых процента)

🚀 Запрос быстрого предложения

📋 Получить полные возможности

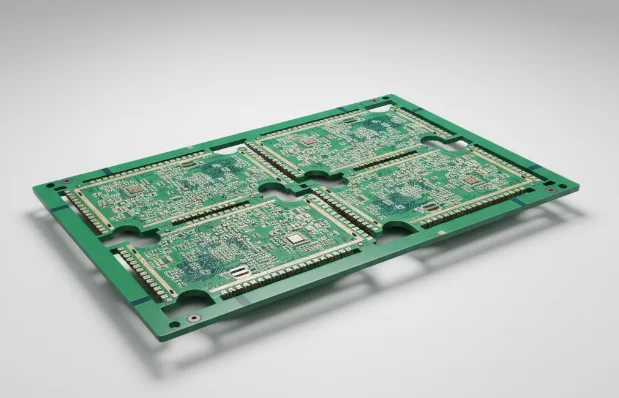

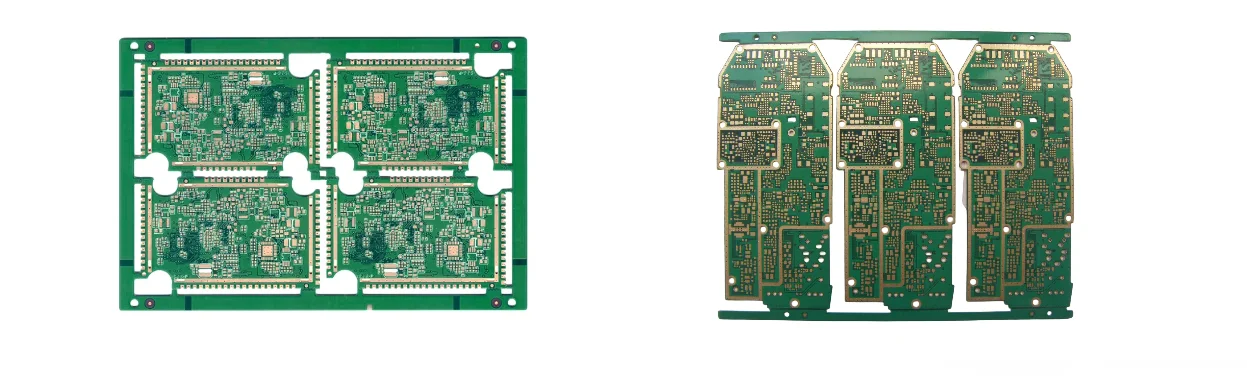

Последовательная ламинация и технологии переходных отверстий

Многоэтапное построение с комплексной проверкой процессовПоследовательная ламинация позволяет достичь плотности трассировки, недостижимой при обычных методах. Каждый цикл использует ступенчатое давление/температуру с потоком смолы, обычно 10–20% (от десяти до двадцати процентов), для стабилизации толщины диэлектрика для импеданса. УФ-лазерные микропереходы обычно 75–125 мкм (от семидесяти пяти до ста двадцати пяти микрометров) контролируются по глубине в пределах ±5 мкм и очищаются для чистого металлизации. Заполнение переходов включает непроводящую смолу (плоскостность ±5 мкм) или медное заполнение для ~10× (в десять раз) лучшей теплопроводности/электропроводности в силовых цепях—см. передовые технологии переходных отверстий.

Встроенный AOI обнаруживает внутренние слои с деталями до 25 мкм; рентген проверяет совмещение; TDR на тестовых образцах подтверждает импеданс перед выпуском. IST (Interconnect Stress Test) обычно 200–500 (от двухсот до пятисот) циклов проверяет надежность; микросекции подтверждают ≥20 мкм (больше или равно двадцати микрометрам) меди в стенках. Для длинных backplanes согласуйте с командами backplane PCB стратегию обратного сверления и разъемов.

- Диаметр микропереходов 75–125 мкм стандартно

- Медные микропереходы для 10× улучшения теплопроводности

- IST 200–500 циклов (от двухсот до пятисот)

- Минимальная толщина меди в стенках 20 мкм (двадцать микрометров)

- Ионное загрязнение ≤1.56 мкг/см² (меньше или равно одной целой пятидесяти шести сотым)

- Процесс Cpk обычно ≥1.33 (больше или равно одной целой тридцати трём сотым)

Технические характеристики многослойных и HDI печатных плат

Комплексные возможности для сложных высокоскоростных/высокоплотных проектов

| Параметр | Стандартные возможности | Расширенные возможности | Стандарт |

|---|---|---|---|

Количество слоев | 4–12 слоев (четыре до двенадцати) | До 64 слоев (до шестидесяти четырех) | IPC-2221 |

Основные материалы | FR-4 Tg 150–180 °C (сто пятьдесят до ста восьмидесяти) | Megtron/Rogers/Isola с низкими потерями | IPC-4101 |

Толщина платы | 0.6–3.2 мм (ноль целых шесть десятых до трех целых две десятых) | До 8.0 мм (до восьми) | IPC-A-600 |

Вес меди | 0.5–2 унции (семнадцать до семидесяти микрометров) | До 4 унций (до четырех) | IPC-4562 |

Мин. ширина/зазор | 75/75 мкм (3/3 мил; семьдесят пять на семьдесят пять) | 25/25 мкм (1/1 мил; двадцать пять на двадцать пять) | IPC-2221 |

Мин. размер отверстия | 0.15 мм (шесть мил) механическое | 0.05 мм (два мил) лазерное | IPC-2222 |

Технология переходных отверстий | Сквозные, глухие/скрытые | Микропереходы, stacked vias, via-in-pad | IPC-6012 |

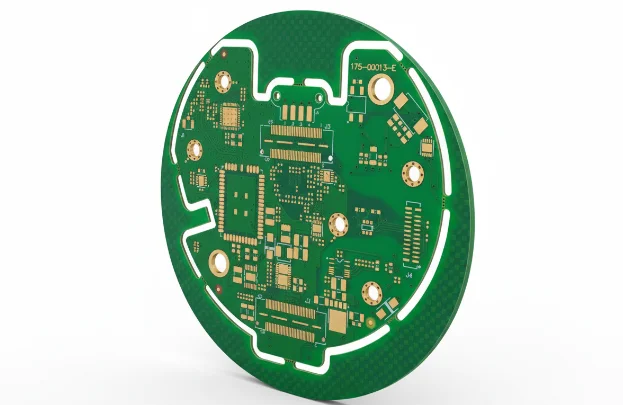

Макс. размер панели | 571.5 × 609.6 мм | 571.5 × 1200 мм | Manufacturing capability |

Контроль импеданса | ±10% (плюс/минус десять процентов) | ±5% (плюс/минус пять процентов) | IPC-2141 |

Поверхностная отделка | ENIG, OSP, Иммерсионное серебро | ENEPIG, Твердое/Мягкое золото | IPC-4552/4556 |

Контроль качества | 100% E-тест, AOI | Импеданс (TDR), Рентген, микросекция | IPC-9252 |

Сертификации | ISO 9001, UL, RoHS/REACH | IATF 16949, AS9100, ISO 13485 | Industry standards |

Срок изготовления | 5–7 дней (пять до семи) | 3 дня экспресс (три дня) | Production schedule |

Готовы начать ваш PCB проект?

Независимо от того, нужен ли вам простой прототип или сложный производственный запуск, наши передовые производственные возможности обеспечивают превосходное качество и надежность. Получите вашу расценку в течение 30 минут.

Целостность сигнала и стратегия размещения переходных отверстий

Поддерживайте расстояние между дифференциальными парами примерно в 2× (два раза) больше ширины дорожки и размещайте экранирующие переходные отверстия в пределах ~1× (одного раза) диаметра отверстия для обеспечения непрерывности обратного пути выше 1 ГГц (один гигагерц). Остаточные части переходных отверстий должны быть уменьшены до <10 мил (менее десяти мил) для линий связи свыше 10 Гбит/с (десять гигабит в секунду). Разделения силовых плоскостей должны сохранять обратные токи; классическое правило 20H может снизить краевое излучение для ЭМС. Наш DFM-аудит проверяет это перед выпуском.

- Проверка стабильности Dk/Df в диапазоне от −40 до +125 °C (минус сорок до плюс сто двадцать пять)

- Скрининг резонанса переходных отверстий выше 5 ГГц

- Терморельеф для плат с толстым медным покрытием

- Доступ для ICT должен составлять ≥95% (больше или равно девяноста пяти процентам)

Полный технологический процесс с контрольными точками качества

Формирование внутренних слоев с точностью до 75 мкм (семьдесят пять микрометров) стандартно и 25 мкм (двадцать пять) для продвинутых. AOI охватывает 100% внутренних слоев; ламинация выполняется на вакуумных прессах при температуре 185–195 °C (сто восемьдесят пять до сто девяносто пять) с поэтапным давлением для предотвращения недостатка смолы. После ламинации рентген подтверждает точность ±15–25 мкм. Механическое сверление использует шпиндели класса 300 тыс. об/мин; гальваническое покрытие формирует 25–35 мкм (двадцать пять до тридцать пять) в отверстиях. Для HDI-процессов циклы ламинации/сверления повторяются с метрологией на каждом этапе.

Тестирование включает летающие зонды/фикстуры E-test, корреляцию импеданса TDR, микросекции и IST. Данные привязываются к партиям и хранятся 7–10 лет (семь до десять лет) для автомобильных/аэрокосмических программ. Для системных сборок и корпусов см. сборку корпусов.

Контроль импеданса с проверенным моделированием

Контрольные образцы проходят TDR с типичной точностью ±2 Ом (плюс/минус два ома) для проверки предсказаний решателя. Стандартный FR-4 Df ~0.015–0.020 на 1 ГГц (один гигагерц) против низкопотерь 0.002–0.005 увеличивает дальность канала. Гладкая медь (Rz <2 мкм) улучшает вносимые потери на ~10–20% (десять до двадцать процентов) выше 5 ГГц. См. наш метод контроля импеданса и совместное проектирование высокоскоростных плат с высокоскоростными PCB.

Проверка надежности и мониторинг SPC

Термоциклирование от −40 до +125 °C (минус сорок до плюс сто двадцать пять) для 500–1000 циклов с дрейфом сопротивления <10% (менее десяти процентов). HAST 130 °C/85% RH выявляет риски влажности; SIR подтверждает ≥10^8 Ом (больше или равно один на десять в восьмой степени ом). SPC отслеживает точность позиционирования, положение отверстий, толщину покрытия и импеданс; первые образцы проверяют размеры обычно ±0.05 мм и импеданс в пределах ±5%.

Стратегии реализации для конкретных отраслей

Телеком/Датаком: 24–32 слоя с низкопотерьными диэлектриками и обратным сверлением для 25+ Гбит/с.

Аэрокосмическая/Оборонная: Документация IPC Class 3 и расширенное хранение партий.

Промышленность/Энергетика: Платы 2–4 унции; комбинируйте с толстослойными PCB по необходимости. Для протяженных шасси координируйте с backplane PCB.

Инженерные гарантии и сертификации

Опыт: производство многослойных/HDI плат с точностью позиционирования обычно ±15–25 μm и проверкой импеданса на тестовых образцах.

Экспертиза: последовательная ламинация, заполнение микропереходов, контроль обратного сверления и Cpk ≥1.33 (больше или равно один точка три три).

Авторитетность: производство по стандарту IPC-6012 Class 3; см. IPC Class 3 примечания.

Надежность: отслеживаемость в MES (от партии до единицы) с отчетами TDR/IST/микросекций по запросу.

- Контроль: течение смолы, толщина диэлектрика, точность сверления

- Отслеживаемость: цифровые маршрутные листы и отчеты по партиям

- Валидация: TDR, IST, поперечные сечения, ионные и SIR тесты

Часто задаваемые вопросы

How many layers can you reliably manufacture?

Which via options are recommended for high speed?

How is impedance verified in production?

Which materials should I choose for 10–28+ Gbps?

Do you support box-level builds after fabrication?

Испытайте превосходство передового производства PCB

От простых прототипов до сложных производственных запусков, наша фабрика мирового класса обеспечивает превосходное качество, быстрый оборот и конкурентоспособные цены. Присоединяйтесь к тысячам довольных клиентов, доверяющих нам свои потребности в производстве PCB.