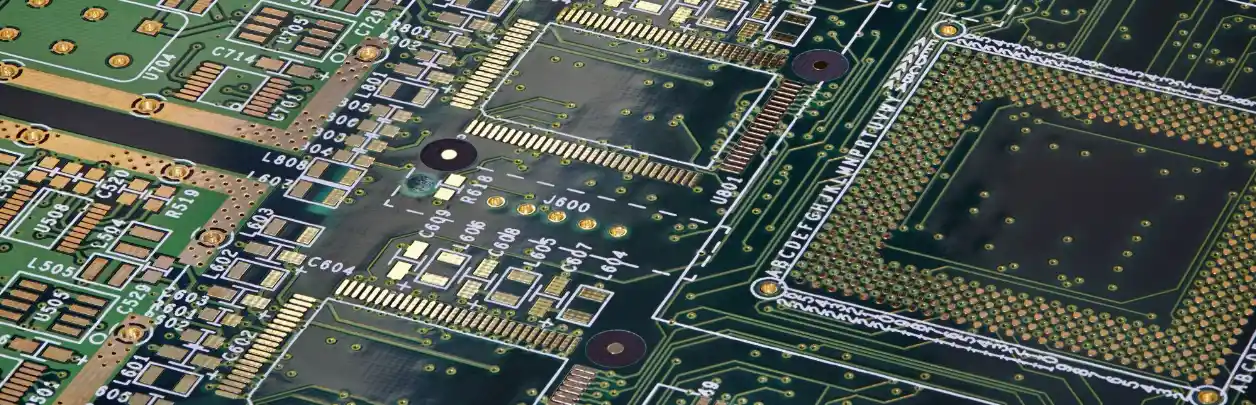

HDI PCB-Herstellung | 50–75 μm Mikrovias, Any-Layer, VIPPO | IATF 16949

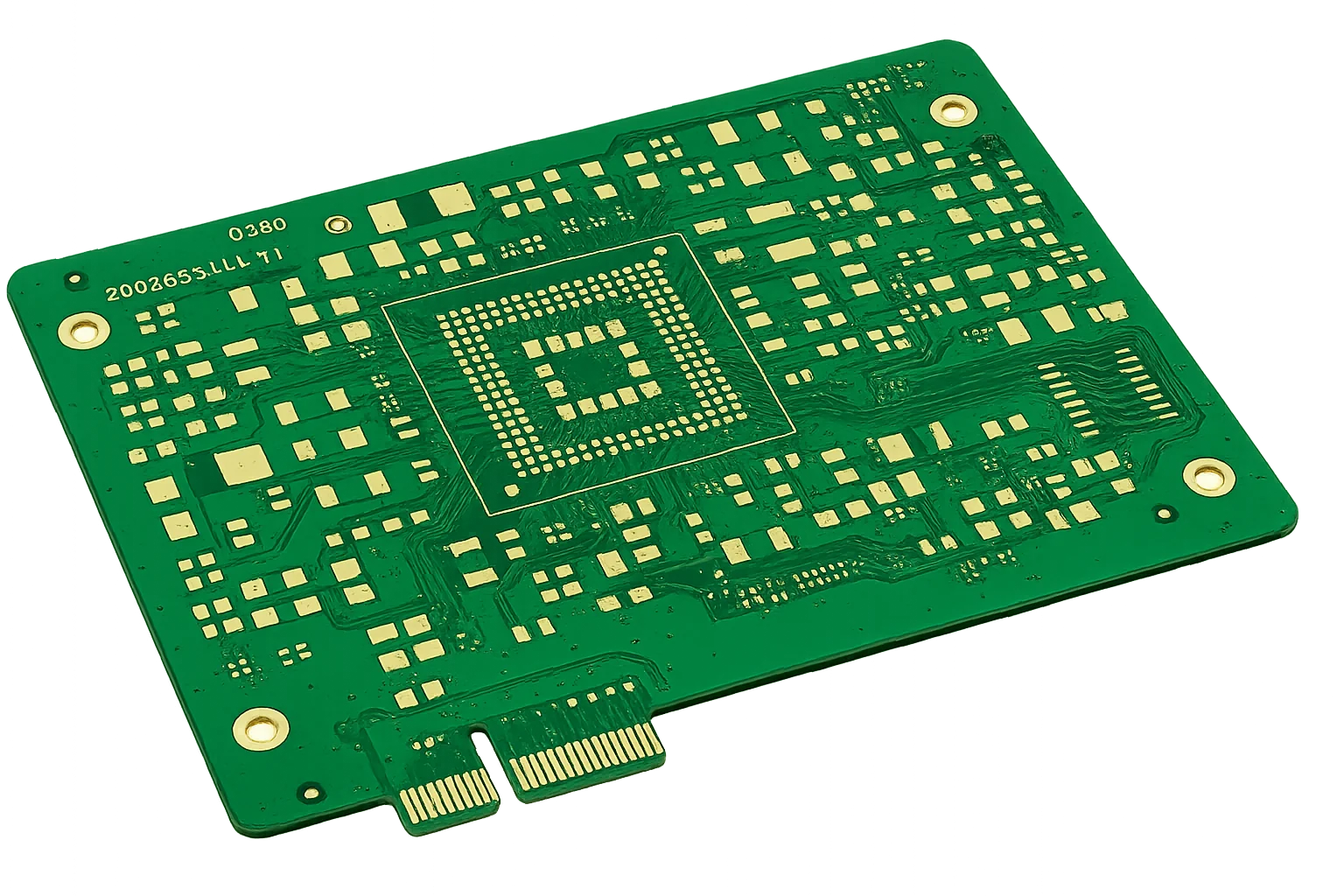

Hochdichte Interconnect (HDI) PCBs mit 50–75 μm (fünfzig bis fünfundsiebzig Mikrometer) Laser-Mikrovias, 1+N+1 bis Any-Layer-Architekturen, Via-in-Pad vergoldet (VIPPO) und verlustarme Schichtungen für 10–56 Gbps (zehn bis sechsundfünfzig Gigabit pro Sekunde). Impedanzkontrolle ±5% (plus/minus fünf Prozent) mit TDR-Validierung. 7-Tage (sieben Tage) Schnellfertigung verfügbar.

HDI-Technologieauswahl und Werttechnik

Schichtungsarchitektur für Dichte-Leistungs-BalanceDer Einsatz von HDI beginnt, wenn der BGA-Raster unter 0,8 mm (null Komma acht Millimeter) fällt oder die Schichtanzahl über wirtschaftliche Grenzen steigt. Wir bewerten drei Entscheidungspunkte: Mikrovia-Stapelhöhe (typischerweise auf zwei für Zuverlässigkeit begrenzt), sequenzielle Laminierungszyklen (1+N+1 vs. 2+N+2 Kosten/Nutzen) und Materialübergänge, wenn die Betriebsfrequenzen 5–8 GHz (fünf bis acht Gigahertz) überschreiten. Durch systematische Aufbauoptimierung wird die Gesamtdicke üblicherweise um 25–40% (fünfundzwanzig bis vierzig Prozent) reduziert, während die IPC-6012 Klasse 3-Zuverlässigkeit erhalten bleibt.

Laser-Mikrovias von 50–75 μm (fünfzig bis fünfundsiebzig Mikrometer) mit einem Aspektverhältnis ≤1:1 (kleiner oder gleich eins zu eins) ermöglichen Via-in-Pad-Fanout, wodurch die parasitäre Induktivität im Vergleich zu Dog-Bone-Routing um ~40–60% (ungefähr vierzig bis sechzig Prozent) reduziert wird. Für >10–12 Gbps (größer als zehn bis zwölf Gigabit pro Sekunde) differenzielle Paare erhalten kürzere Verbindungen die Augenmargen und reduzieren Signalskew. Für detaillierte Via-Design- und Testkorrelationen siehe unsere Impedanzkontrolle-Anleitung und Mikrovia-Zuverlässigkeit-Studie.

Kritisches Risiko: Übermäßige Mikrovia-Stapelung, schlechte Harzfüllung oder unausgewogene Laminierung können zu Hohlräumen, Barrel-Rissen und leitenden anodischen Filamenten (CAF) während thermischer Belastung führen. Überbohrung oder hohe Aspektverhältnisse erhöhen auch das Ausfallrisiko an der Via-to-Capture-Schnittstelle.

Unsere Lösung: Wir setzen IPC-6016 und IPC-6012 Klasse 3-Mikrovia-Zuverlässigkeitsstandards durch. Jede Aufbaustruktur wird auf z-Achsen-Ausdehnung simuliert, mit vakuumunterstützter Kupferbeschichtung gefüllt und planarisiert. Querschnittsanalyse und Verbindungsbelastungstests (IST) bestätigen die Stapelvia-Integrität und Beschichtungs-CPK ≥ 1,33 (größer oder gleich eins Komma drei drei). Für ultradichte Designs kombinieren Hybridschichtungen Mehrschichtige PCBs und Backplane-PCBs für Routing- und Stromverteilungsbalance.

- Mikrovia-Durchmesser: 50–75 μm (fünfzig bis fünfundsiebzig Mikrometer), Aspektverhältnis ≤1:1 (kleiner oder gleich eins zu eins)

- Sequenzielle Laminierung: 1+N+1 durch Any-Layer-Konfigurationen

- VIPPO mit Dimpeltiefe <10% (kleiner als zehn Prozent) der Pad-Dicke

- Differenzielle Paar-Skew-Kontrolle auf ±5 ps (plus/minus fünf Pikosekunden) in optimierten Layouts

- Hybridschichtungen mit niedrigem Df 0,005–0,012 (null Komma null null fünf bis null Komma null eins zwei) auf kritischen Schichten

- Verformungskontrolle ≤0,7% (kleiner oder gleich null Komma sieben Prozent) für große BGAs

🚀 Schnelle Angebotsanfrage

📋 Vollständige Fähigkeiten erhalten

Sequentieller Aufbau-Prozesssteuerung & Validierung

Registrierungsgenauigkeit durch mehrstufige AusrichtungsüberprüfungMehrzyklische Aufbauten halten die Schichtregistrierung innerhalb von ±25–50 μm (plus/minus fünfundzwanzig bis fünfzig Mikrometer). UV-YAG bei 355 nm (dreihundertfünfundfünfzig Nanometer) ermöglicht konsistente Ablation über FR-4 high-Tg (170–180 °C — einhundertsiebzig bis einhundertachtzig Grad Celsius) und Low-Loss-Systeme. Die Energiedichte wird an Dk/Df angepasst, um Carbonisierung zu verhindern und saubere Seitenwände für die Metallisierung zu erhalten.

Kupferfüllung wird nach Zuverlässigkeit ausgewählt: elektrolytisches Kupfer für automobilthermische Profile (−40 °C↔+125 °C — minus vierzig bis plus einhundertfünfundzwanzig) und leitfähige Paste für kostengünstige Verbraucheranwendungen. Die Vorproduktions-CAM-Technik wendet FEA an, um CTE-Spannung an der Mikrovia-Krümmung vorherzusagen. Dimensionsstabilität wird optisch an fünf Stellen pro Panel gemäß IPC-2226 Level C überprüft.

- CO₂- und UV-Laser mit Strahlgenauigkeit ±10 μm (plus/minus zehn Mikrometer)

- Chemische Saatbeschichtung mit Gleichmäßigkeit ±10% (plus/minus zehn Prozent)

- Röntgenausrichtungsprüfung gestapelter Vias mit 5 μm (fünf Mikrometer) Auflösung

- IST nach IPC-TM-650 2.6.26 (Interconnect-Stresstest) qualifiziert

HDI PCB Fähigkeits- und Leistungsmatrix

Prozessfenster optimiert für Zuverlässigkeits-Kosten-Gleichgewicht

| Parameter | Standardfähigkeit | Erweiterte Fähigkeit | Standard |

|---|---|---|---|

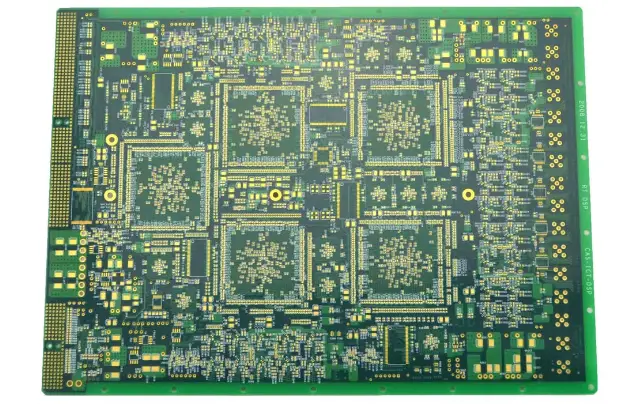

Layer Count | 4–30 Lagen (vier bis dreißig) | Bis zu 60+ Lagen (bis zu sechzig plus, Any-Layer) | IPC-2226 |

Base Materials | High-Tg FR-4, Low-Dk/Df-Materialien | Megtron 6/7, Isola I-Speed, Rogers RO4000 | IPC-4101 |

Board Thickness | 0,4–3,2 mm (null komma vier bis drei komma zwei) | 0,2–6,0 mm (null komma zwei bis sechs komma null) | IPC-A-600 |

Min Trace/Space | 75/75 μm (3/3 mil; fünfundsiebzig mal fünfundsiebzig Mikrometer) | 50/50 μm (2/2 mil; fünfzig mal fünfzig Mikrometer) | IPC-2221 |

Min Hole Size (Laser) | 0,10 mm (4 mil; null komma eins null Millimeter) | 0,05 mm (2 mil; null komma null fünf Millimeter) | IPC-2226 |

Via Technology | Blind-/Buried-Vias, Microvias (1+N+1, 2+N+2) | Gestapelt/Gestaffelt, VIPPO, Any-Layer | IPC-6012 |

Aspect Ratio (Microvia) | 0,8:1 (null komma acht zu eins) | 1:1 (eins zu eins) | IPC-2226 |

Max Panel Size | 500 × 400 mm (fünfhundert mal vierhundert Millimeter) | 600 × 500 mm (sechshundert mal fünfhundert Millimeter) | Manufacturing capability |

Impedance Control | ±10% (plus/minus zehn Prozent) | ±5% (plus/minus fünf Prozent) mit TDR | IPC-2141 |

Surface Finish | HASL, ENIG, OSP, Immersionsilber | ENEPIG, Weich-/Hartgold, Selektives OSP | IPC-4552/4556 |

Quality Testing | E-Test, AOI, Röntgen | 4-Draht-Kelvin, Querschnitt, IST, HAST | IPC-9252 |

Certifications | ISO 9001, UL, RoHS | IATF 16949, ISO 13485, AS9100, MIL-PRF-31032 | Industry standards |

Lead Time | 7–15 Tage (sieben bis fünfzehn Tage) | 24-Stunden (vierundzwanzig-Stunden) Prototyp-Schnellfertigung | Production schedule |

Bereit, Ihr PCB-Projekt zu starten?

Ob Sie einfache Prototypen oder komplexe Produktionsläufe benötigen, unsere fortschrittlichen Fertigungskapazitäten gewährleisten überlegene Qualität und Zuverlässigkeit. Erhalten Sie Ihr Angebot in nur 30 Minuten.

Stack-Up-Architektur & Materialsystemintegration

Der Übergang von 1+N+1 zu 2+N+2 erfolgt typischerweise, wenn 0,8 mm (null Komma acht Millimeter) Pitch-BGAs mehr als 400–600 Pins aufweisen. Wir modellieren Via-Stub-Resonanz bei etwa 0,25λ (ein Viertel Wellenlänge) nahe 10 GHz (zehn Gigahertz) und verlegen kritische Netze auf blinde/rückgebohrte Pfade. Niederlustige Übergänge (Df 0,009–0,012) sind gerechtfertigt, sobald das Einfügedämpfungsbudget unter ~0,8–1,0 dB/in (ungefähr null Komma acht bis eins Komma null Dezibel pro Zoll) fällt. Siehe HDI-Herstellung und Blind-Via-Optimierung.

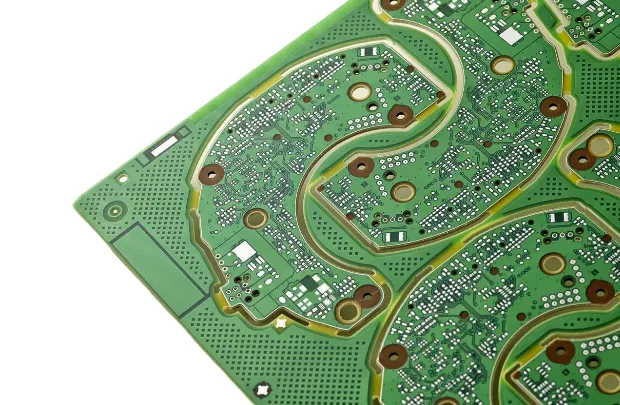

Die Zuverlässigkeit gestapelter Mikrovias hängt von gleichmäßigem Kupfer durch sequentielle Beschichtung ab. Wir streben ≥18–20 μm (größer oder gleich achtzehn bis zwanzig Mikrometer) im Barrel an, verifiziert durch Querschnitt. Gestaffelte Stapel verbessern die Thermozykluslebensdauer um 20–30% (zwanzig bis dreißig Prozent), benötigen jedoch mehr Fläche. VIPPO-Füllung CTE wird abgestimmt (≈45–55 ppm/°C — ungefähr fünfundvierzig bis fünfundfünfzig Teile pro Million pro Grad Celsius), um Lötverbindungsstress zu begrenzen; Kupferfüllung wird gewählt, wenn die Wärmeableitung pro Via ~2 W (etwa zwei Watt) übersteigt.

Aufbaufolgenoptimierung & Prozessfenster

Die Kernvorbereitung zielt auf Schrumpfung <0,05% (weniger als null Komma null fünf Prozent). Jeder SBU-Zyklus: Laminierung 175–190 °C (einhundertfünfundsiebzig bis einhundertneunzig Grad Celsius), Laser-Via-Bildung mit 70–80° (siebzig bis achtzig Grad) Seitenwänden, dann stromlose + elektrolytische Kupferabscheidung. Desmear verwendet Permanganat, abgestimmt auf minimale dielektrische Rezession bei vollständiger Entfernung von Schmutz. Der Prozess-Cpk für Ringfläche und Via-Abstand wird ≥1,33 (größer oder gleich eins Komma drei drei) gehalten. Puls-Umkehr-Plattierung erreicht eine Wurfkraft >80% (größer als achtzig Prozent). Details in unserem HDI-Leitfaden.

Die QA nach der Laminierung umfasst AOI bis zu 10 μm (zehn Mikrometer), Röntgentomographie für Mikrovia-Halsverengung und elektrische Tests (fliegende Sonde/Fixture). 4-Draht-Kelvin verifiziert den Widerstand auf ±1 mΩ (plus/minus ein Milliohm) für die Erkennung marginaler Verbindungen.

Hochgeschwindigkeitsleistung durch kontrollierte Impedanz

Reduzierte Via-Stubs und enge Ebenenkopplung verbessern die Rückflussdämpfung. Für >10 Gbps (größer als zehn Gigabit pro Sekunde) differenzielle Paare verwenden wir blinde/rückgebohrte Architekturen, um resonante Stubs zu eliminieren. Die Materialauswahl wechselt zu ultra-niederlustig (Df 0,005–0,007), wenn das dB/in-GHz-Produkt Grenzen erreicht. Unser Impedanzmodellierung verwendet 3D-EM für Via-Arrays und Übergänge, erreicht ±5% (plus/minus fünf Prozent) Produktionstoleranz mit Coupon-Korrelation. Niederprofil-Kupfer (Rz <2 μm — weniger als zwei Mikrometer) reduziert den Leiterverlust um 15–20% (fünfzehn bis zwanzig Prozent). Dünne Aufbau-Dielektrika (50–75 μm) ermöglichen PDN-Schleifeninduktivität unter 100 pH (einhundert Pikohenry).

Zuverlässigkeitsvalidierung: Thermisch, Feuchtigkeit und IST

Thermische Zyklen von −40 °C bis +125 °C (minus vierzig bis plus einhundertfünfundzwanzig) mit 15-minütigen Haltezeiten zielen auf ≥1000 (größer oder gleich eintausend) Zyklen ohne >10% (größer als zehn Prozent) Widerstandsänderung ab. IST induziert Joulesche Erwärmung, um beginnende Ausfälle zu erkennen (>500 Zyklen typisch bei 150 °C — einhundertfünfzig Grad Celsius). HAST 130 °C/85% RH (einhundertdreißig Grad Celsius/fünfundachtzig Prozent relative Luftfeuchtigkeit) für 96 h (sechsundneunzig Stunden) validiert die Feuchtigkeitsbeständigkeit.

SEM-Querschnitte überprüfen Kupferkörner, Haftung und Hohlräume; IPC-A-600 Klasse 3 Akzeptanz umfasst ≥5 μm (größer oder gleich fünf Mikrometer) Umhüllungsbeschichtung und keine Kniebrüche. Ionische Reinheit ≤1,56 μg/cm² NaCl-Äquivalent (kleiner oder gleich eins Komma fünf sechs Mikrogramm pro Quadratzentimeter). CAF-Tests bei 65 °C/88% RH (fünfundsechzig Grad Celsius/achtundachtzig Prozent relative Luftfeuchtigkeit) mit 100 VDC (einhundert Volt Gleichstrom) für ≥500 h (größer oder gleich fünfhundert Stunden).

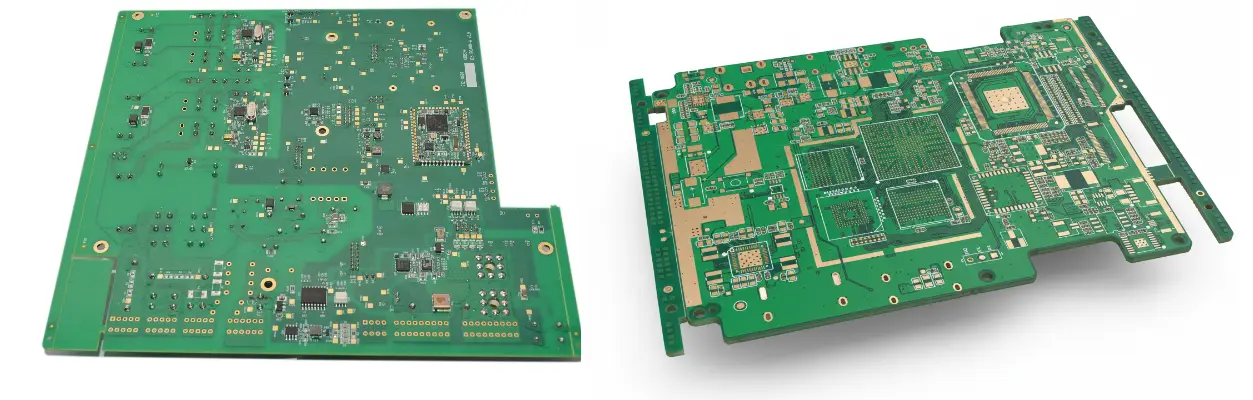

Anwendungsspezifische HDI-Strategien

Automobil ADAS: 2+N+2 mit selektiven verlustarmen RF-Schichten, Einfügedämpfung <0,3 dB/in (kleiner als null Komma drei Dezibel pro Zoll) bei 77 GHz (siebenundsiebzig Gigahertz), kupfergefüllte Wärmedurchgangslöcher mit θJB <2 °C/W (kleiner als zwei Grad Celsius pro Watt).

Medizin: Any-Layer-Miniaturisierung mit ISO 13485-Dokumentation.

Datacom/5G: 25–56 Gbps (fünfundzwanzig bis sechsundfünfzig Gigabit pro Sekunde) SERDES; siehe 5G PCB-Technologie.

Verbraucher: Selektives HDI nur bei Dichteanforderungen, Kostensenkung um 15–25% (fünfzehn bis fünfundzwanzig Prozent).

Technische Absicherung & Zertifizierungen

Erfahrung: Produktionserprobte 1+N+1 bis Any-Layer-Programme mit zonengesteuerter Laminierung und LDI-Registrierung.

Expertise: TDR/VNA für Via-Übergangsmodelle; SPC bei Beschichtung und Bohrungsregistrierung; Cpk-Ziele ≥1,33 (größer oder gleich eins Komma drei drei).

Autorität: IPC Klasse 3, IATF 16949, ISO 13485, AS9100; Audits und Dokumentation end-to-end.

Vertrauenswürdigkeit: MES verfolgt Loscodes und Serialisierung bis zu Inline-Testdaten; IST/HAST-Berichte für die Qualifikation verfügbar.

- Prozesskontrollen: Beschichtungsdicke, Laminierungsdruck/Temperatur, Laserenergie

- Rückverfolgbarkeit: Einheitenserialisierung, Komponentenlosverfolgung, digitaler Begleitschein

- Validierung: IST, HAST, Mikroschnittprüfungen, Impedanzcoupons

Häufig gestellte Fragen

How do I choose between 1+N+1 and 2+N+2 HDI?

What limits stacked microvia reliability and how to mitigate?

When should I move to low-loss or ultra-low-loss materials?

Which factors drive HDI pricing the most?

Can you validate impedance to tight tolerances on HDI?

Erleben Sie Fertigungsexzellenz

Fortschrittliche Fertigungsprozesse gewährleisten, dass jede PCB den höchsten Qualitätsstandards entspricht. Erhalten Sie sofort Ihr individuelles Angebot.