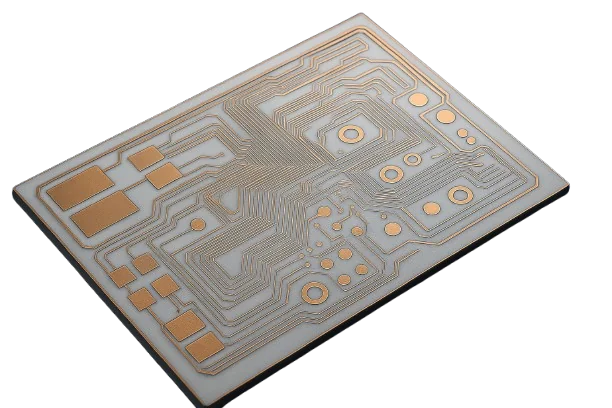

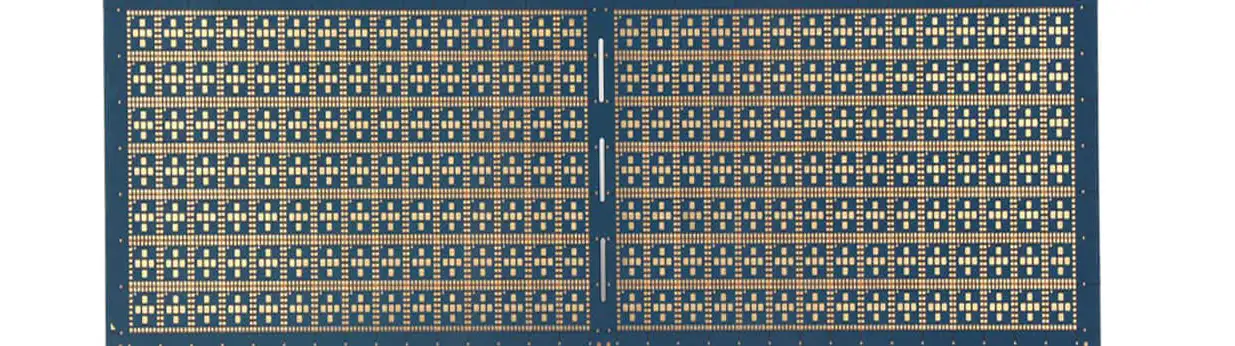

PCB per substrati IC (ABF/BT) | Linee sottili SAP, Microvia sovrapposti, Passo 0,25–0,40 mm (zero virgola venticinque a zero virgola quaranta)

Substrati organici IC per imballaggio avanzato: Processo Semi-Additivo (SAP) 15–20 μm (quindici a venti micrometri) linea/spazio, microvia sovrapposti 25–50 μm (venticinque a cinquanta), stratificazione ABF/BT, pronto per flip-chip con deformazione controllata e impedenza ±5% (più/meno cinque percento).

Produzione di substrati IC e architettura dei materiali

Collegamento della densità di I/O del silicio con l'affidabilità a livello di sistemaI substrati IC combinano la tecnologia di packaging dei semiconduttori e dei PCB per ottenere una densità di routing quasi pari a quella del silicio. Il Processo Semi-Additivo (SAP) deposita rame su uno strato di semina per formare caratteristiche fini, fornendo 15–20 μm (quindici-venti micrometri) linea/spazio con un minimo di sottoincisione—tipicamente un guadagno di densità di 2–4× (due-quattro volte) rispetto all'HDI sottrattivo. Consulta la nostra panoramica sui PCB HDI e le note sulla produzione avanzata di HDI per i concetti di costruzione correlati.

Gli strati di ABF (Ajinomoto Build-up Film) di 30–60 μm (trenta-sessanta micrometri) mantengono un controllo rigoroso dello spessore per stabilizzare l'impedenza e l'induttanza del loop PDN. I compositi in resina BT mostrano tipicamente un CTE X-Y di 12–14 ppm/°C (dodici-quattordici parti per milione per grado Celsius), collegando il silicio ~2.6 ppm/°C (due virgola sei) e l'FR-4 ~16–18 ppm/°C (sedici-diciotto). Per layout misti RF/digitali, le scelte dei materiali sono allineate con la nostra guida sui PCB ad alta frequenza e il manuale sui materiali.

Rischio critico: La disallineamento tra gli strati ABF, la scarsa adesione del rame o la deformazione incontrollata durante la laminazione possono portare a circuiti aperti, crepe delle vie o deriva dell'impedanza > ±10 percento (più/meno dieci percento). Un riempimento inadeguato delle via-in-pad e la planarità superficiale compromettono anche l'affidabilità del wire-bonding negli assemblaggi SiP e flip-chip.

La nostra soluzione: Applichiamo la simulazione dell'integrità del segnale e i metodi di correlazione dei PCB backplane per validare il comportamento degli interconnessioni ad alta densità. Le linee SAP e mSAP operano in camere bianche classe 1000 con controllo della copertura a gradini inferiore a ±2 μm (più/meno due micrometri). Ogni lotto di substrati viene sottoposto a mappatura CTE, profilatura della deformazione e verifica TMA secondo i requisiti IPC-6012 Classe 3 AABUS. Dove i front-end RF richiedono prestazioni ultra-bassa perdita, i sistemi ibridi ABF e PTFE vengono co-processati per minimizzare la discontinuità dielettrica.

Per ulteriori approfondimenti sui compromessi dei materiali e sulla modellazione dell'affidabilità, consulta la validazione dello stress termico e le opzioni dei PCB in substrato ceramico che estendono la tecnologia dei substrati IC alle applicazioni RF ad alta potenza e ai sensori.

- Routing a linee sottili tramite SAP con ridotta sottoincisione rispetto all'incisione sottrattiva

- Costruzione ABF con controllo dielettrico di 30–60 μm (trenta-sessanta)

- Ottimizzazione del CTE composito (obiettivo substrato 9–14 ppm/°C — nove-quattordici)

- Controllo della deformazione ≤0.5% (minore o uguale a zero virgola cinque percento) della diagonale (obiettivo di processo)

- Stabilità dell'impedanza con tolleranza ±5% (più/meno cinque percento)

🚀 Richiesta Preventivo Rapido

📋 Ottieni Capacità Complete

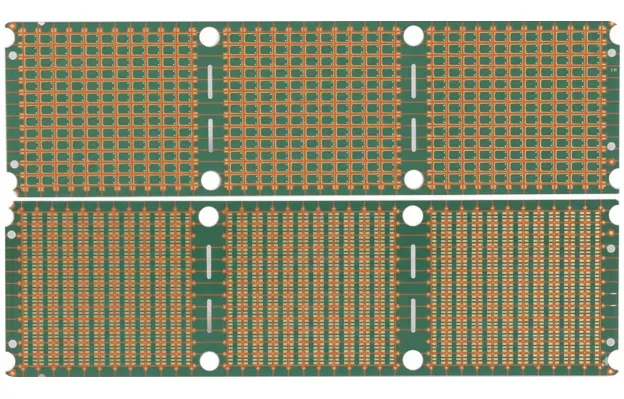

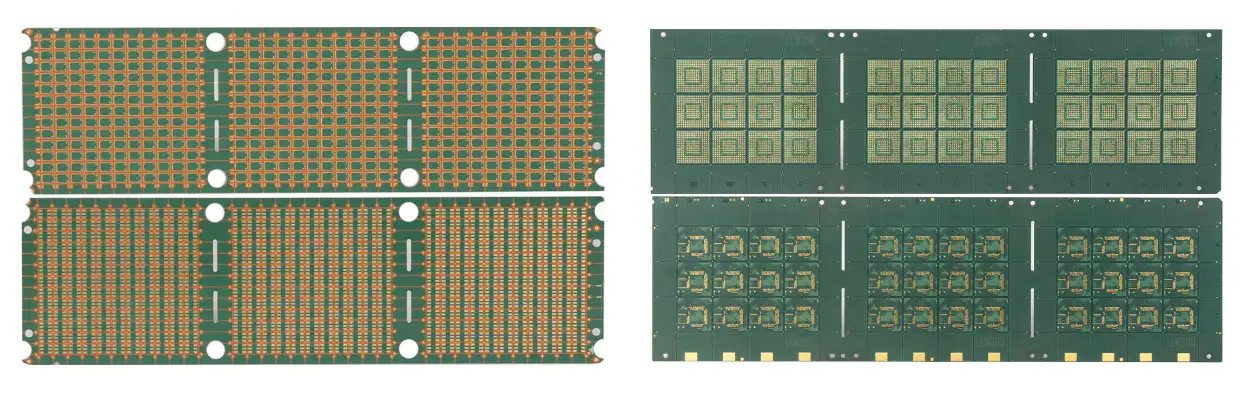

Flusso SAP Controllato e Cancelli di Qualità Guidati dalla Resa

Fotolitografia, placcatura e metrologia ottimizzate per passo fineLe finestre di processo sono significativamente più strette rispetto ai PCB standard. L'uniformità di deposizione dello strato di seme entro ±10% (più o meno dieci percento) precede la modellazione fotografica per caratteristiche di 15–20 μm. La placcatura a impulsi inversi gestisce la crescita dei bordi e il potere di lancio; l'incisione differenziale rimuove il seme tra le tracce con controllo della larghezza ±10% (più o meno dieci percento). Le microvia con diametro di 25–50 μm (venticinque-cinquanta micrometri) raggiungono un controllo della profondità di ±5 μm (più o meno cinque). Vedi eccellenza nella produzione e controlli del processo HDI.

AOI con risoluzione ≤5 μm (minore o uguale a cinque micrometri), bersagli di registrazione a raggi X e IST (Interconnect Stress Test) oltre 200–500 (duecento-cinquecento) cicli proteggono l'affidabilità. Per l'integrazione a livello di scheda (backplane/schede di linea), vedi PCB backplane e capacità PCB ad alta velocità.

- SPC per spessore e uniformità dello strato di seme

- Placcatura in rame a impulsi inversi per caratteristiche uniformi

- Formazione di microvia laser e verifica del riempimento in rame

- Controllo qualità multi-gate AOI/raggi X/IST

Specifiche Tecniche del Substrato IC

Linee sottili, microvia impilate e costruzioni compatibili con flip-chip

| Parametro | Capacità Standard | Capacità Avanzata | Standard |

|---|---|---|---|

Layer Count | 4–16 strati (da quattro a sedici) | Fino a 50 strati (fino a cinquanta) | JEDEC |

Base Materials | Resina BT, FR-4 ad alta Tg | ABF, Poliimmide, Substrato in vetro | IPC-4101/4103 |

Board Thickness | 0.20–0.80 mm (zero virgola due zero a zero virgola otto zero) | Fino a 0.10 mm (fino a zero virgola uno zero) | IPC-A-600 |

Copper Weight | 12–18 μm (da dodici a diciotto micrometri) | 5–35 μm (da cinque a trentacinque; costruzioni SAP) | IPC-4562 |

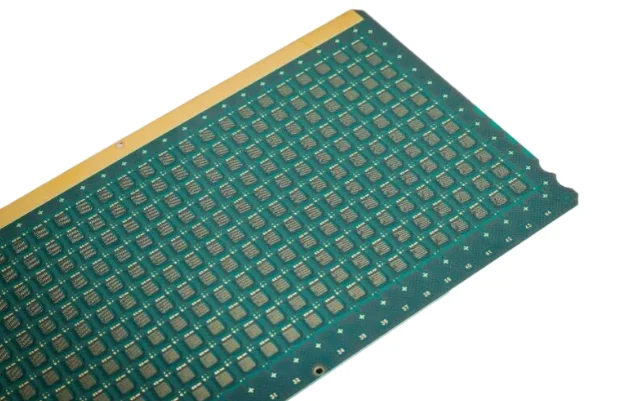

Min Trace/Space | 25/25 μm (uno/uno mil; venticinque per venticinque) | 15/15 μm (0.6/0.6 mil; quindici per quindici) | IPC-2226 |

Min Hole Size (Laser) | 50 μm (due mils) | 25 μm (un mil) | IPC-2226 |

Via Technology | Microvia, vie sepolte | Microvia impilate, via-in-pad, HDI a qualsiasi strato | IPC-6012 |

BGA Pitch | 0.40 mm (zero virgola quattro zero) | 0.25 mm (zero virgola due cinque) | JEDEC |

Impedance Control | ±10% (più/meno dieci percento) | ±5% (più/meno cinque percento) con TDR | IPC-2141 |

Surface Finish | ENIG, OSP | ENEPIG, Nichel/oro senza elettrolisi, Oro morbido/duro | IPC-4552/4556 |

Quality Testing | AOI, E-test | SEM, Sezione trasversale, TDR/IST | IPC-9252 |

Certifications | ISO 9001, UL | IATF 16949, Metodi JEDEC | Standard industriali |

Lead Time | 15–25 giorni (da quindici a venticinque) | Consultare per tempi rapidi | Programma di produzione |

Pronto a iniziare il tuo progetto PCB?

Che tu abbia bisogno di semplici prototipi o di produzioni complesse, le nostre capacità di produzione avanzate garantiscono qualità superiore e affidabilità. Ottieni il tuo preventivo in soli 30 minuti.

Integrità del Segnale e Co-Progettazione PDN

A 28–112 Gbps (ventotto-centododici) SerDes, le discontinuità nelle transizioni palla-substrato dominano perdite e riflessioni. La regolazione degli antipad e le recinzioni di vie di massa entro 0.5–1.0 mm (zero virgola cinque - uno virgola zero millimetri) mantengono i percorsi di ritorno. La selezione del materiale Df (tipico ABF 0.010–0.015 a 10 GHz) e la rugosità del rame (Ra ≤1.5 μm) supportano gli obiettivi di perdita di inserzione—vedi controllo dell'impedenza e test TDR.

Gli obiettivi PDN inferiori a 1–10 mΩ (uno-dieci milliohm) fino a 100 MHz (cento megahertz) si basano su dielettrici sottili 30–60 μm (trenta-sessanta) e fitte aree di vie sotto il die (tipicamente 100–200 vias/cm²). Per i canali a livello di scheda e i connettori, allineati con le nostre capacità PCB ad alta velocità e PCB backplane.

Precisione di Registrazione e Disciplina del Processo in Camera Bianca

Il SAP inizia con micro-irruvidimento (Ra ~0.5–1.0 μm), rame di semina 0.5–1.0 μm (zero virgola cinque - uno virgola zero) e spessore del resist 15–25 μm per modelli 15–20 μm. La placcatura a impulsi inversi costruisce il rame del segnale 10–15 μm (dieci-quindici) e i piani 20–30 μm (venti-trenta). Dopo la rimozione del resist, l'incisione differenziale pulisce il rame di semina senza sottosquadro. Le camere bianche (Classe 1,000–10,000 — mille-diecimila) minimizzano cortocircuiti/interruzioni nei passi fini; vedi flusso di produzione.

Gli obiettivi di registrazione strato-strato ±25 μm (più/meno venticinque micrometri) utilizzano allineamento ottico e riferimenti a raggi X. La costruzione sequenziale utilizza sistemi a basso flusso (flusso di resina <5% — meno del cinque percento) per mantenere lo spessore del dielettrico ±5% (più/meno cinque percento). L'SPC mantiene Cpk ≥1.33 (maggiore o uguale a uno virgola tre tre) per le caratteristiche critiche.

ABF vs. BT vs. Vetro e Opzioni Emergenti

ABF: fotoimmaginabile, microvia per litografia fino a 15–25 μm (quindici-venticinque), Dk ~3.2–3.4, Df ~0.010–0.015 a 10 GHz.

BT: conveniente per wire-bond/flip-chip moderato con CTE X-Y 12–14 ppm/°C.

Substrato in vetro: CTE ~3 ppm/°C e Ra ultra-liscio <0.1 μm (meno di zero virgola uno), abilitando strutture TGV/ponte. Per i moduli RF front-end, considera anche gli interpositori PCB ceramici.

Flip-Chip, Underfill e Assemblaggio PoP

Il flip-chip richiede controllo della coplanarità; una deformazione superiore a 50–75 μm (cinquanta-settantacinque micrometri) rischia giunti non bagnati. L'underfill con CTE 25–35 ppm/°C ridistribuisce lo stress. Per PoP e SiP, coordina passo/deformazione e profili di rifusione. Esplora le note di imballaggio in substrato flip-chip e la validazione del sistema in box build.

Garanzia Ingegneristica & Certificazioni

Esperienza: costruzioni SAP volumetriche con routing di 15–20 μm e pitch di 0.25–0.40 mm.

Competenza: uniformità del seed, placcatura pulse-reverse, riempimento di microvia impilati e registrazione a raggi X; SPC mantiene Cpk ≥1.33 (maggiore o uguale a uno punto tre tre).

Autorevolezza: affidabilità allineata a JEDEC, documentazione IPC-6012 Classe 3.

Affidabilità: tracciabilità MES che collega lotti di fornitori, serializzazione e report AOI/X-ray/IST/TDR.

- Controlli: mappatura dello spessore, fattore di incisione, registrazione, rugosità del rame

- Tracciabilità: codici lotto, serializzazione delle unità, digital traveler

- Validazione: IST 200–500 cicli, sezioni trasversali, SIR, TDR

Domande frequenti

ABF vs. BT: which dielectric should I choose?

What fine-line and via sizes do you support?

How do you manage warpage for flip-chip?

Can the substrate handle 112 Gbps channels?

Which surface finish is recommended?

Sperimenta l'Eccellenza Manifatturiera

Processi di produzione avanzati garantiscono che ogni PCB soddisfi i più alti standard di qualità. Ottieni subito il tuo preventivo personalizzato.