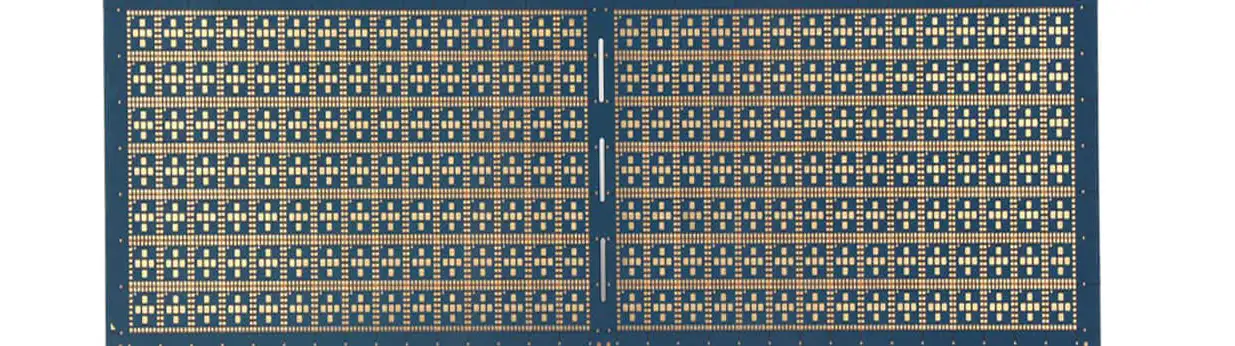

Печатные платы IC Substrate (ABF/BT) | Тонкие линии SAP, многослойные микропереходы, шаг 0.25–0.40 мм (ноль целых двадцать пять сотых до ноль целых сорок сотых)

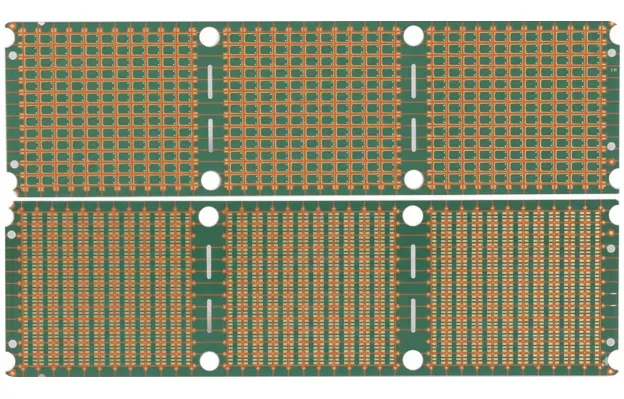

Органические подложки IC для продвинутой упаковки: полуаддитивный процесс (SAP) 15–20 мкм (пятнадцать-двадцать микрометров) линия/промежуток, многослойные микропереходы 25–50 мкм (двадцать пять-пятьдесят), ABF/BT слоистая структура, готовность к флип-чипу с контролируемой деформацией и импедансом ±5% (плюс/минус пять процентов).

Производство и архитектура материалов IC-подложек

Соединение плотности ввода-вывода кремния с надежностью на системном уровнеIC-подложки объединяют технологии полупроводниковой упаковки и печатных плат для достижения плотности трассировки, близкой к кремниевой.

Полуаддитивный процесс (SAP) осаждает медь на затравку для формирования тонких элементов, обеспечивая 15–20 мкм (пятнадцать-двадцать микрометров) линий/промежутков с минимальным подтравливанием — обычно это 2–4× (два-четыре раза) увеличение плотности по сравнению с субтрактивным HDI. См. наш обзор HDI PCB и заметки о продвинутом производстве HDI для связанных концепций построения.

ABF (Ajinomoto Build-up Film) слои толщиной 30–60 мкм (тридцать-шестьдесят микрометров) поддерживают жесткий контроль толщины для стабилизации импеданса и индуктивности петли PDN.

Композиты на основе BT-смолы обычно демонстрируют X-Y CTE 12–14 ppm/°C (двенадцать-четырнадцать частей на миллион на градус Цельсия), соединяя кремний ~2.6 ppm/°C (две целых шесть десятых) и FR-4 ~16–18 ppm/°C (шестнадцать-восемнадцать). Для смешанных RF/цифровых компоновок выбор материалов соответствует нашему руководству по высокочастотным PCB и основам материалов.

Критический риск: Несовмещение слоев ABF, плохая адгезия меди или неконтролируемая деформация при ламинации могут привести к обрывам цепи, растрескиванию переходных отверстий или отклонению импеданса > ±10% (плюс-минус десять процентов). Недостаточное заполнение переходных отверстий в контактных площадках и неровность поверхности также снижают надежность проволочного монтажа в SiP и flip-chip сборках.

Наше решение: Мы применяем моделирование целостности сигнала и методы корреляции backplane PCB для проверки поведения высокоплотных соединений. Линии SAP и mSAP работают в чистых помещениях класса 1000 с контролем покрытия ступеней в пределах ±2 мкм (плюс-минус два микрометра). Каждая партия подложек проходит картирование CTE, профилирование деформации и проверку TMA по требованиям IPC-6012 Class 3 AABUS. Когда RF фронтенды требуют сверхнизких потерь, гибридные системы ABF и PTFE совместно обрабатываются для минимизации диэлектрических разрывов.

Для более глубокого понимания компромиссов материалов и моделирования надежности изучите проверку термических напряжений и варианты керамических подложек PCB, которые расширяют технологию IC-подложек для мощных RF и сенсорных применений.

- Тонкая трассировка через SAP с уменьшенным подтравливанием по сравнению с субтрактивным травлением

- ABF построение с контролем диэлектрика 30–60 мкм (тридцать-шестьдесят)

- Оптимизация композитного CTE (цель подложки 9–14 ppm/°C — девять-четырнадцать)

- Контроль деформации ≤0.5% (меньше или равно нуль целых пять десятых процента) от диагонали (цель процесса)

- Стабильность импеданса с допуском ±5% (плюс-минус пять процентов)

🚀 Запрос быстрого предложения

📋 Получить полные возможности

Контролируемый поток SAP и контроль качества, ориентированный на выход

Фотолитография, гальваника и метрология, настроенные для мелкого шагаОкна процессов значительно уже, чем у стандартных печатных плат. Равномерность осаждения затравки в пределах ±10% (плюс/минус десять процентов) предшествует фотошаблонированию для элементов размером 15–20 мкм. Импульсно-обратная гальваника контролирует рост краев и силу покрытия; дифференциальное травление удаляет затравку между дорожками с контролем ширины ±10% (плюс/минус десять процентов). Микропереходы диаметром 25–50 мкм (двадцать пять-пятьдесят микрометров) обеспечивают контроль глубины ±5 мкм (плюс/минус пять). См. совершенство производства и контроль процессов HDI.

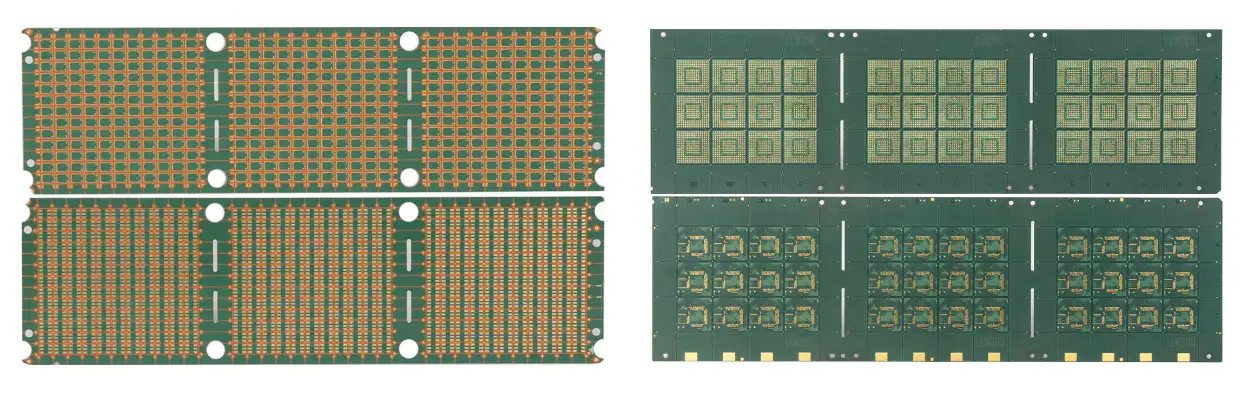

Автоматический оптический контроль с разрешением ≤5 мкм (меньше или равно пяти микрометрам), рентгеновские метки совмещения и тест на механические нагрузки (IST) более 200–500 (двести-пятьсот) циклов обеспечивают надежность. Для интеграции на уровне плат (магистральные платы/линейные карты) см. магистральные печатные платы и возможности высокоскоростных печатных плат.

- SPC контроля толщины и равномерности затравки

- Импульсно-обратная медная гальваника для равномерных элементов

- Формирование лазерных микропереходов и проверка заполнения медью

- Многоступенчатый контроль качества AOI/X-ray/IST

Технические характеристики IC Substrate

Тонкие линии, многослойные микропереходы и совместимые с flip-chip сборки

| Parameter | Standard Capability | Advanced Capability | Standard |

|---|---|---|---|

Layer Count | 4–16 слоев (от четырех до шестнадцати) | До 50 слоев (до пятидесяти) | JEDEC |

Base Materials | BT смола, High-Tg FR-4 | ABF, Полиимид, Стеклянная подложка | IPC-4101/4103 |

Board Thickness | 0.20–0.80 мм (от нуля целых двадцати сотых до нуля целых восьмидесяти сотых) | До 0.10 мм (до нуля целых десяти сотых) | IPC-A-600 |

Copper Weight | 12–18 мкм (от двенадцати до восемнадцати микрометров) | 5–35 мкм (от пяти до тридцати пяти; SAP сборки) | IPC-4562 |

Min Trace/Space | 25/25 мкм (один/один мил; двадцать пять на двадцать пять) | 15/15 мкм (0.6/0.6 мил; пятнадцать на пятнадцать) | IPC-2226 |

Min Hole Size (Laser) | 50 мкм (два мила) | 25 мкм (один мил) | IPC-2226 |

Via Technology | Микропереходы, скрытые переходы | Многослойные микропереходы, переходы в площадке, HDI любого слоя | IPC-6012 |

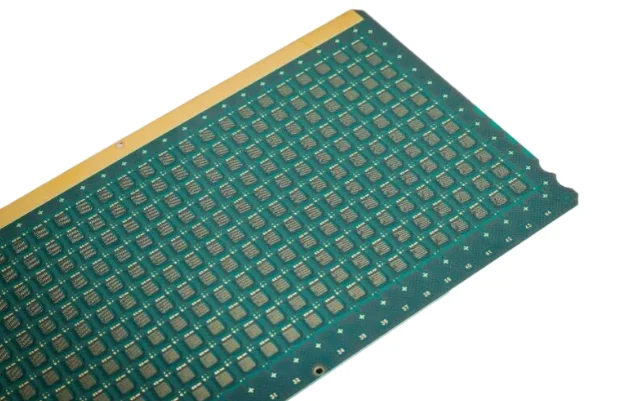

BGA Pitch | 0.40 мм (ноль целых сорок сотых) | 0.25 мм (ноль целых двадцать пять сотых) | JEDEC |

Impedance Control | ±10% (плюс/минус десять процентов) | ±5% (плюс/минус пять процентов) с TDR | IPC-2141 |

Surface Finish | ENIG, OSP | ENEPIG, Безникелевое Ni/Au, Мягкое/Твердое золото | IPC-4552/4556 |

Quality Testing | AOI, E-test | SEM, Поперечный срез, TDR/IST | IPC-9252 |

Certifications | ISO 9001, UL | IATF 16949, Методы JEDEC | Industry standards |

Lead Time | 15–25 дней (от пятнадцати до двадцати пяти) | Уточняйте для ускоренного производства | Production schedule |

Готовы начать ваш PCB проект?

Независимо от того, нужен ли вам простой прототип или сложный производственный запуск, наши передовые производственные возможности обеспечивают превосходное качество и надежность. Получите вашу расценку в течение 30 минут.

Целостность сигнала и совместное проектирование PDN

На скоростях 28–112 Гбит/с (двадцать восемь до ста двенадцати) SerDes, неоднородности при переходе от шарика к подложке доминируют в потерях и отражениях. Настройка антипад и заземляющие виа-барьеры в пределах 0.5–1.0 мм (ноль целых пять десятых до одной целой нуля десятых миллиметра) поддерживают обратные пути. Выбор материала Df (типичный ABF 0.010–0.015 на 10 ГГц) и шероховатость меди (Ra ≤1.5 мкм) соответствуют целевым показателям потерь на вставку — см. контроль импеданса и TDR-тестирование.

Целевые показатели PDN ниже 1–10 мОм (один до десяти миллиом) на частотах до 100 МГц (сто мегагерц) достигаются за счет тонких диэлектриков 30–60 мкм (тридцать до шестидесяти) и плотного расположения виа под кристаллом (обычно 100–200 виа/см²). Для каналов и разъемов на уровне платы используйте наши возможности в области высокоскоростных PCB и backplane PCB.

Точность совмещения и дисциплина чистых помещений

SAP начинается с микрошлифовки (Ra ~0.5–1.0 мкм), осаждения начального слоя меди 0.5–1.0 мкм (ноль целых пять десятых до одной целой нуля десятых) и толщины резиста 15–25 мкм для паттернов 15–20 мкм. Импульсно-обратное осаждение формирует сигнальную медь 10–15 мкм (десять до пятнадцати) и плоскости 20–30 мкм (двадцать до тридцати). После удаления резиста дифференциальное травление удаляет начальный слой без подтравливания. Чистые помещения (Класс 1,000–10,000 — одна тысяча до десяти тысяч) минимизируют короткие замыкания/обрывы в мелком шаге; см. процесс производства.

Целевые показатели межслойного совмещения ±25 мкм (плюс/минус двадцать пять микрометров) достигаются с помощью оптического выравнивания и рентгеновских меток. Последовательное наращивание использует системы с низкой текучестью (текучесть смолы <5% — менее пяти процентов) для поддержания толщины диэлектрика ±5% (плюс/минус пять процентов). SPC поддерживает Cpk ≥1.33 (больше или равно одной целой тридцати трём сотым) для критических элементов.

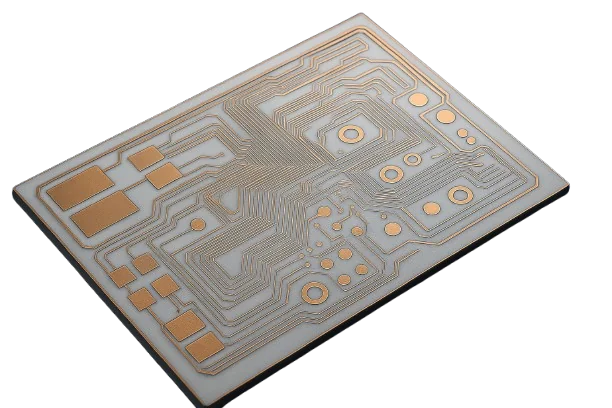

ABF vs. BT vs. Стекло и новые варианты

ABF: фотоформируемый, микропереходы литографией до 15–25 мкм (пятнадцать до двадцати пяти), Dk ~3.2–3.4, Df ~0.010–0.015 на 10 ГГц.

BT: экономически эффективен для проволочного крепления/умеренного flip-chip с X-Y CTE 12–14 ppm/°C.

Стеклянная подложка: CTE ~3 ppm/°C и ультрагладкая Ra <0.1 мкм (менее нуля целых одной десятой), позволяющая создавать TGV/мостовые структуры. Для RF фронтенд-модулей также рассмотрите керамические PCB интерпозеры.

Flip-Chip, Андерфилл и PoP сборка

Flip-chip требует контроля плоскостности; коробление превышающее 50–75 мкм (пятьдесят до семидесяти пяти микрометров) рискует образованием непропаянных соединений. Андерфилл с CTE 25–35 ppm/°C перераспределяет напряжение. Для PoP и SiP согласуйте шаг/коробление и профили повторного нагрева. Изучите заметки по упаковке в flip-chip подложке и валидации системы в box build.

Инженерные гарантии и сертификации

Опыт: объемные сборки SAP с трассировкой 15–20 мкм и шагом 0.25–0.40 мм.

Экспертиза: равномерность затравки, импульсно-обратное покрытие, заполнение стеков микропереходов и регистрация рентгеном; SPC поддерживает Cpk ≥1.33 (больше или равно одной целой тридцать три сотых).

Авторитетность: надежность по стандартам JEDEC, документация IPC-6012 Class 3.

Надежность: прослеживаемость MES, связывающая партии поставщиков, сериализацию и отчеты AOI/X-ray/IST/TDR.

- Контроль: карта толщин, фактор травления, регистрация, шероховатость меди

- Прослеживаемость: коды партий, сериализация единиц, цифровой маршрутный лист

- Валидация: IST 200–500 циклов, поперечные сечения, SIR, TDR

Часто задаваемые вопросы

ABF vs. BT: which dielectric should I choose?

What fine-line and via sizes do you support?

How do you manage warpage for flip-chip?

Can the substrate handle 112 Gbps channels?

Which surface finish is recommended?

Испытайте превосходство передового производства PCB

От простых прототипов до сложных производственных запусков, наша фабрика мирового класса обеспечивает превосходное качество, быстрый оборот и конкурентоспособные цены. Присоединяйтесь к тысячам довольных клиентов, доверяющих нам свои потребности в производстве PCB.