当下一代 5G 基站未通过第一次合规性测试时,罪魁祸首通常不是芯片组或软件,而是 PCB。阻抗失配会产生驻波、反射和不需要的谐波,从而削弱射频和微波性能。对于高频设计,精确的阻抗控制不是可选的;它是可靠运营和法规遵从性的基础。

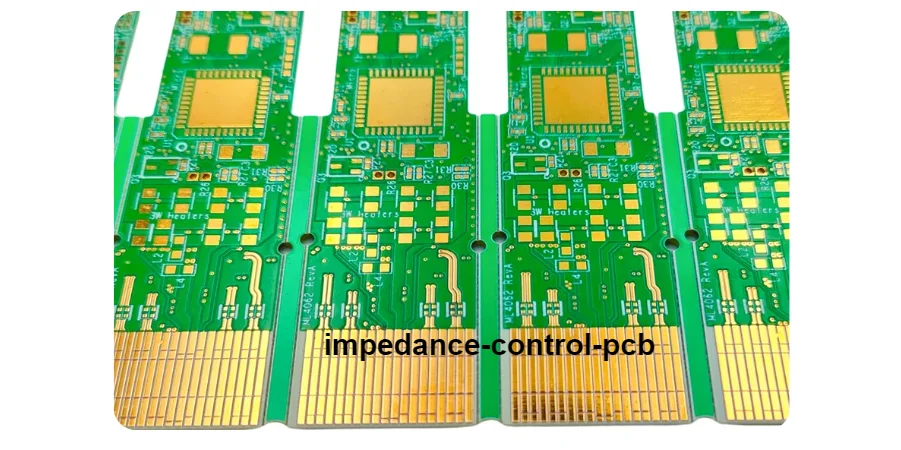

在 Highleap PCB 工厂 (HILPCB),我们专注于阻抗精度为 ±5Ω 的射频和微波 PCB 制造。我们的工程流程在您的设计到达测试台之前消除了可变性,确保 5G、航空航天、国防和其他关键应用的最佳信号完整性。

阻抗控制背后的物理原理

要了解阻抗控制,首先要认识到每条PCB走线在信号波长接近走线尺寸的频率下都充当传输线。对于以多千兆赫兹频率运行的现代数字系统,即使是短走线也会表现出传输线行为,需要仔细的阻抗管理。

特性阻抗基础:走线几何形状和阻抗之间的关系遵循公认的电磁原理。对于微带走线,特性阻抗取决于走线宽度、铜厚度、基板高度和介电常数。任何参数的微小变化都会显着影响最终阻抗值,因此制造控制对于一致的结果至关重要。

材料特性影响:PCB 基板材料表现出与频率相关的介电特性,会影响整个工作带宽的阻抗稳定性。标准 FR4 材料为 5GHz 以下的应用提供足够的性能,而毫米波应用则需要专用的低损耗材料。我们的材料选择过程考虑了电气性能和制造兼容性。

温度系数效应:跨温度范围的阻抗稳定性取决于基板和铜导体的热膨胀特性。高TgPCB 材料提供更好的尺寸稳定性,而适当的热管理可防止运行过程中的阻抗漂移。

卓越的制造工艺

实现一致的阻抗控制需要集成的制造工艺来监控和控制影响最终电气性能的每个变量。

统计过程控制实施:我们的阻抗控制制造使用全面的 SPC 系统来监控每个生产面板的走线宽度、铜厚度和介电高度。实时数据收集可立即调整工艺,始终将阻抗保持在 ±5% 规格以内。

先进的镀铜控制:电镀均匀性直接影响走线电阻和阻抗特性。我们的自动电镀系统使用电流密度优化和实时厚度监控来实现均匀的铜分布,即使在具有高纵横比过孔的复杂 HDI PCB 设计中也是如此。

精密蚀刻技术:蚀刻过程中的走线宽度控制决定了最终阻抗精度。我们增强的蚀刻工艺使用实时监控蚀刻速率均匀性,并自动调整化学成分,从而在整个面板区域保持一致的痕量曲线。

高速数字系统应用

现代处理器和通信系统突破了频率界限,这使得阻抗控制对于基本功能至关重要,而不仅仅是最佳性能。

处理器接口设计:下一代 CPU 的时钟频率接近 10GHz,边沿速率在低于 100 皮秒范围内。在这些速度下,每条走线都表现为传输线,阻抗不匹配会导致反射,从而损坏数据或造成时序违规。DDR5 内存接口就是这一挑战的例证,需要 50Ω 单端阻抗控制在 ±7% 以内,以在所有工作条件下保持时序裕度。

SerDes 信道优化:25G/100G 以太网和 PCIe Gen 5 等多千兆位串行接口使用先进的信令技术,需要卓越的阻抗精度。信道均衡和前向纠错可以补偿一些信道损伤,但一致的阻抗为可靠的高速通信提供了基础。

供电网络集成:高性能处理器需要复杂的供电系统,这些系统必须与敏感的高速信号共存。电源平面阻抗通过接地反弹和同时的开关噪声影响信号完整性。我们的 多层 PCB 叠层设计优化了信号阻抗和供电阻抗,以实现最大的系统性能。

射频和微波 PCB 工程可实现最佳信号完整性

射频和微波 PCB 设计需要最严格的阻抗控制,因为即使是微小的偏差也会导致可测量的损耗、反射和失真。

50Ω 系统完整性 行业标准的 50Ω 阻抗在功率处理和衰减之间提供了最佳平衡。始终如一地实现这一目标需要精确控制走线尺寸、介电性能和制造公差。我们的工艺在各种叠层中保持 ±2Ω 精度,确保最大的功率传输和信号保真度。

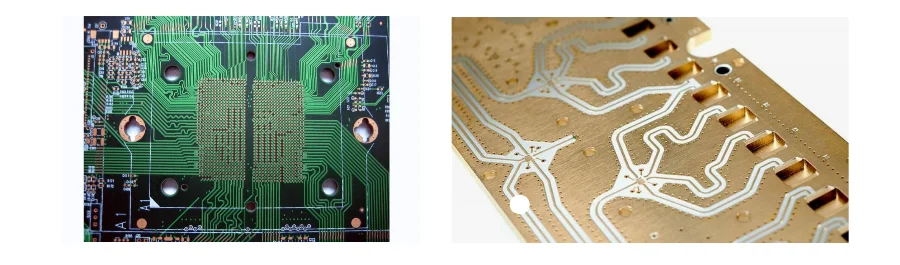

优化的传输线拓扑 常见的射频几何形状包括微带线、带状线和共面波导:

- 微带 – 简化组件访问和调整。

- 带状线 – 在多层结构内提供卓越的隔离。

- 共面波导 – 提供与相邻接地参考的稳定阻抗。

**受控过孔过渡 ** 层变化会引入电感和电容不连续性,从而降低射频性能。我们采用阻抗建模、通过背钻消除短截线以及优化焊盘/过孔几何形状,以最大限度地减少插入损耗和反射。

精密连接器接口 从 PCB 走线到同轴接口,阻抗连续性至关重要。我们的连接器封装工程可确保匹配阻抗、最小寄生效应和机械稳健性,以实现可重复的高频性能。

测试和验证协议

全面的测试验证了所有制造变量和作条件下的阻抗控制性能。

时域反射计 (TDR):TDR 测量提供了阻抗验证的主要方法,以足以识别局部阻抗变化的分辨率测量沿迹线长度的特性阻抗。我们的校准TDR系统在DC至40GHz的频率范围内运行,测量不确定度可追溯到国家标准。

网络分析仪表征:矢量网络分析仪测量通过表征宽频率范围内的阻抗行为来补充 TDR 测试。S 参数测量可验证频率相关影响变得显着的高频应用的插入损耗、回波损耗和阻抗一致性。

生产测试试样设计:每个阻抗控制面板都包含专用的测试试样,可复制关键的走线几何形状和叠层配置。测试试样经过与功能性 PCB 相同的制造工艺,可准确表示所有生产变量的实际电气性能。

我们的 SMT 组装 功能可确保阻抗关键型应用的精确元件放置,而 刚柔结合 PCB 技术将阻抗控制扩展到复杂的三维组装。

常见问题解答

**问:你们在生产中可以达到什么阻抗容差? 我们通常通过先进的过程控制和优质材料选择,为标准应用实现 ±5% 的阻抗容差,为关键射频应用提供 ±2Ω 能力。

**问:在制造过程中如何验证阻抗控制? 每个生产面板都包括使用经过校准的 TDR 设备测量的阻抗测试试样,并提供完整的文档以实现可追溯性和质量保证。

**问:柔性 PCB 上的阻抗可以控制吗? 是的,柔性 PCB 设计可以使用专门的柔性介电材料和精确的导体几何形状控制来实现受控阻抗。

**问:温度对阻抗稳定性有什么影响? 材料选择显着影响温度稳定性。标准 FR4 在汽车温度范围内显示 ~3% 的阻抗变化,而专用材料为关键应用提供了更好的稳定性。

**问:阻抗要求应该在多久之前确定? 应在初始叠层设计期间定义阻抗要求,以确保可制造的解决方案并防止代价高昂的设计修改。

**问:哪些测试方法可以验证阻抗精度? 我们在生产测试试样上同时使用 TDR 和网络分析仪测量来验证阻抗性能并表征整个工作带宽的频率响应。