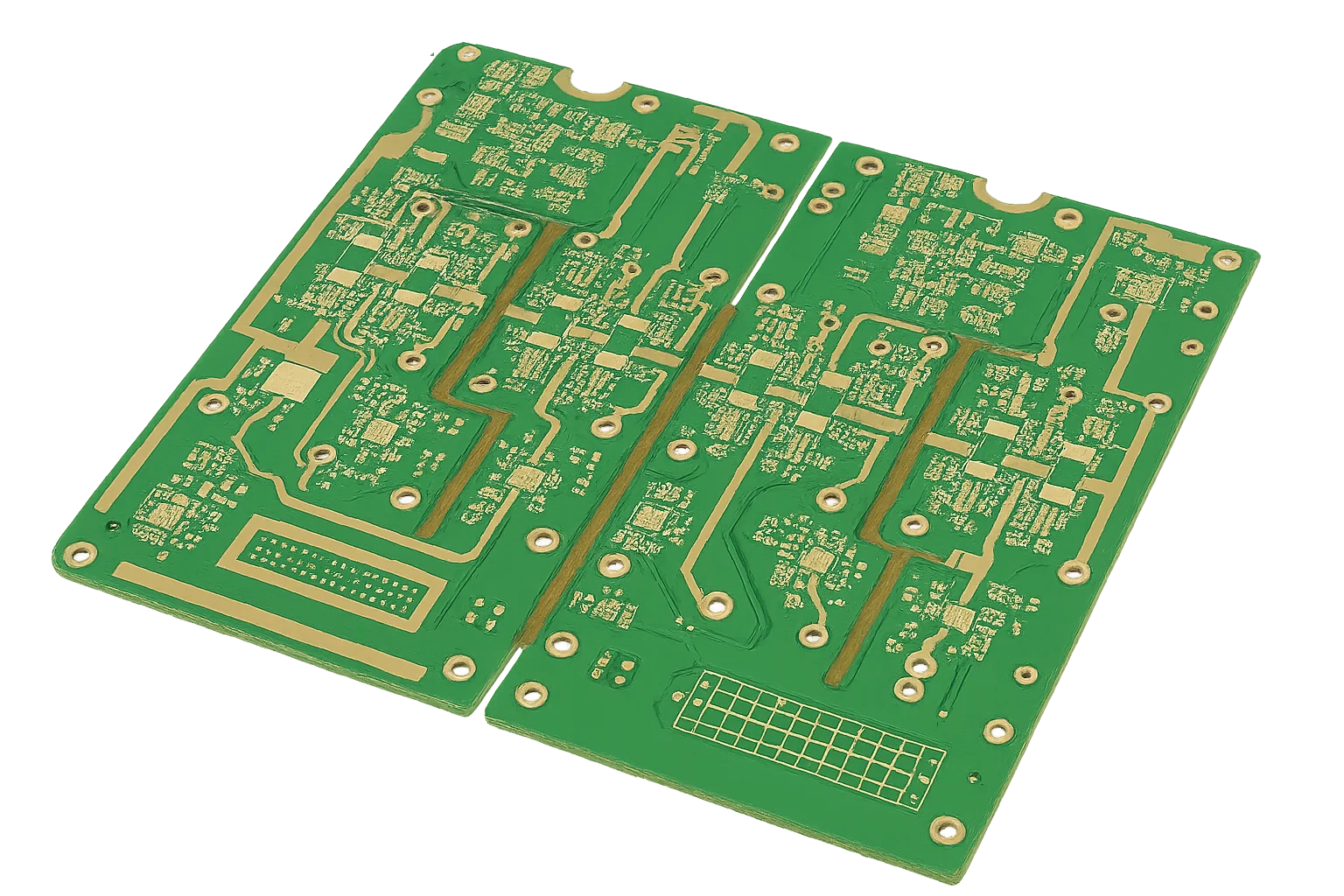

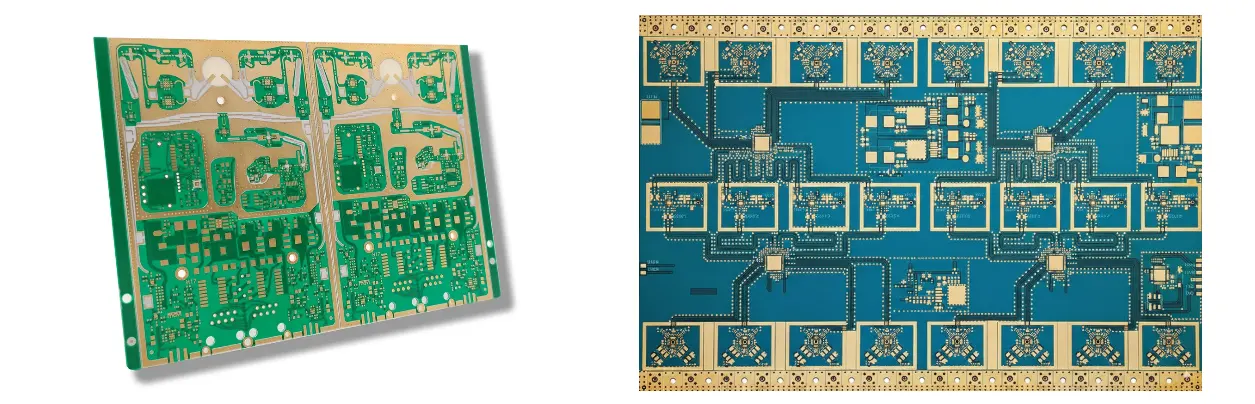

高频PCB制造 | 低损耗射频与毫米波 | 阻抗±5% | 矢量网络分析仪特性测试

适用于6 GHz以下至毫米波的射频与微波PCB:超低损耗材料(介电损耗Df ≤0.0009——小于或等于0.0009),阻抗控制±5%(正负5%)并通过TDR/矢量网络分析仪验证,混合叠层设计可降低成本40–60%(40至60百分比)。提供3–5天(3至5天)快速交付服务。

高频材料选择与性能权衡

优化损耗、相位稳定性及总体拥有成本当工作频率超过约500 MHz至1 GHz(约500兆赫至1000兆赫)时,标准FR-4材料会表现出更高的损耗角正切和介电常数变化,从而降低信号完整性。我们根据频率和预算匹配材料:RO4000或低损耗FR-4用于6 GHz以下(sub-6 gigahertz)系统,PTFE或陶瓷填充层压板用于24–86 GHz(24至86吉赫兹)毫米波应用。典型的低损耗材料可实现Df 0.001–0.003(0.001至0.003),保持稳定的阻抗和相位一致性。如需深入比较,请参阅我们的高频PCB材料指南和Rogers PCB产品系列。

混合叠层将射频层置于优质电介质上,同时在FR-4上布线非关键层,可将总材料成本降低40–60%(40至60百分比)。在通道设计过程中,我们将阻抗建模与铜粗糙度优化相结合——低轮廓铜箔(Ra ≤1.5 µm——小于或等于1.5微米)在10 GHz(10吉赫兹)以上频率下可将导体损耗降低15–25%(15至25百分比)。通过IPC-6018高频PCB可靠性标准验证热管理和膨胀系数匹配。

关键风险:过多的树脂空隙、不受控的Dk变化或不良压合周期可能导致相位偏移和阻抗漂移超过±5%(正负5%),从而在高数据速率下引起反射或眼图闭合。铜粗糙度不一致还会增加插入损耗并限制高速射频链路的传输距离。

我们的解决方案:我们按照IPC-TM-650进行介电常数(Dk)和损耗因子(Df)验证,并通过3D场求解器模拟传输损耗。叠层建模确保使用TDR/VNA关联将阻抗匹配控制在±3%(正负3%)以内。对于毫米波和射频前端模块,采用陶瓷PCB和HDI PCB的混合结构可增强机械稳定性和布线密度。更多内容请参阅我们的高频设计技巧博客。

- 材料Dk范围2.2–10.2(2.2至10.2),稳定性±2%(正负2%)

- 损耗角正切选项Df 0.0009–0.004(0.0009至0.004)

- 通过TDR(时域反射计)验证受控阻抗±5%

- PTFE/陶瓷与FR-4混合以降低成本

- 低轮廓铜Ra ≤1.5 µm(小于或等于1.5微米)

- 相位匹配容差5–10 mil(5至10密耳),典型用于差分对

🚀 快速报价请求

🔧 获取完整制造能力

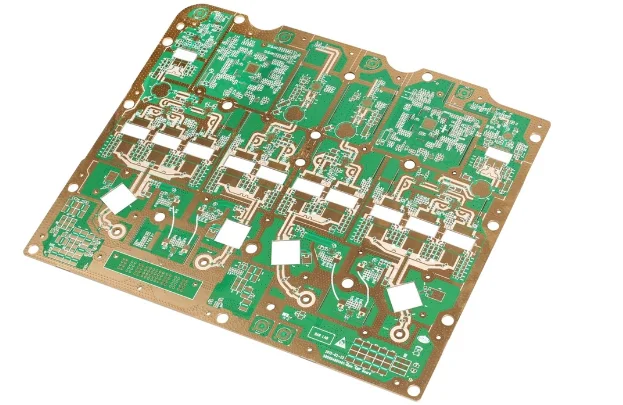

专业射频制造与对位控制

PTFE表面活化、多层对位与毫米波验证基于PTFE的基板需要等离子活化或钠蚀刻以将表面能提升至≥40 dyn/cm(每厘米大于或等于40达因),确保铜层附着力。多层对位通过光学校准保持±25–50 µm(正负25至50微米)精度——这对阵列和波束成形至关重要。我们采用射频工艺窗口——分阶段压合可缓解CTE不匹配(PTFE约200–300 ppm/°C;FR-4约45–70 ppm/°C),防止树脂回缩和分层。

背钻将通孔残桩控制在<10 mil(小于10密耳)以内以支持25–28 Gbps;盲埋孔可完全消除残桩,适用于30+ GHz(30吉赫兹以上)应用。制造后验证包括100%电测、样板TDR及VNA S参数扫描至40–67 GHz(40至67吉赫兹)。成本/交期优化参见组装报价指南。

- PTFE附着力≥40 dyn/cm

- 对位精度±25–50 µm

- 腔体/控深铣切±25 µm

- 背钻残桩<10 mil(小于10密耳)

- 边缘电镀屏蔽典型隔离度−60 dB

射频与微波PCB技术能力

从sub-6 GHz(6吉赫兹以下)到毫米波前端

| 参数 | 标准能力 | 高级能力 | 标准 |

|---|---|---|---|

层数 | 1–20层 | 最高48层(混合结构) | IPC-2221 |

基材 | RO4000 / 低损耗FR-4 | RT/duroid、Taconic、纯PTFE、陶瓷填充 | IPC-4103 |

介电常数(Dk) | 3.0–6.15 | 2.2–10.2,频率稳定性高 | 材料数据表 |

损耗角正切(Df) | <0.004 @10 GHz(10吉赫兹下小于0.004) | ≤0.0009 @10 GHz(10吉赫兹下小于或等于0.0009) | 材料数据表 |

板厚 | 0.2–3.2毫米 | 0.1–6.0毫米 | IPC-A-600 |

铜厚 | 0.5–2盎司 | 最高6盎司 | IPC-4562 |

最小线宽/间距 | 75/75微米(3/3密耳) | 50/50微米(2/2密耳) | IPC-2221 |

阻抗控制 | ±10%(正负10%) | ±5%(正负5%) | IPC-2141 |

表面处理 | ENIG、沉银、OSP | ENEPIG、硬/软金(可键合) | IPC-4552/4553 |

质量测试 | 电测、TDR | 矢量网络分析仪S参数、热冲击测试 | IPC-9252 |

认证 | ISO 9001、UL | IATF 16949、AS9100、MIL-PRF-31032 | 行业标准 |

交付周期 | 5–10天 | 3–5天(加急服务) | 生产计划 |

准备开始您的PCB项目了吗?

无论您需要简单的原型还是复杂的生产运行,我们先进的制造能力确保卓越的质量和可靠性。30分钟内获取您的报价。

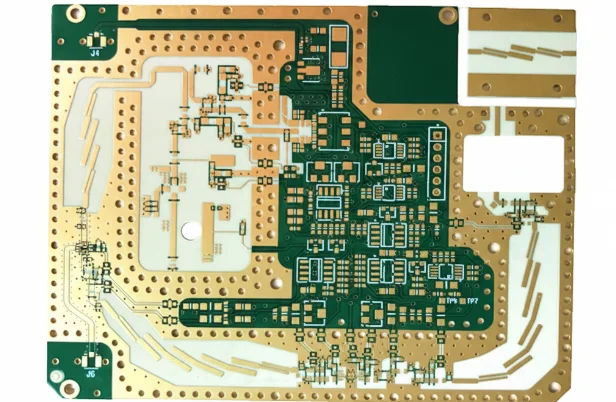

阻抗规划与铜箔粗糙度建模

根据隔离与损耗选择结构:微带线可调谐但在约10 GHz以上会产生辐射;带状线以轻微介质损耗为代价提升隔离度;CPW-G(共面波导接地)可稳定毫米波的回流路径。我们的阻抗控制工作流程包含与低轮廓铜箔的场求解器关联,以抑制粗糙度引起的损耗。差分延迟匹配保持±5 ps(正负5皮秒),最小弯曲半径≥3×线宽。

过孔转换主导不连续性:反焊盘调谐、0.5 mm(0.5毫米)内的接地过孔围栏,以及背钻或盲孔可消除可能在20–30 GHz以上谐振的残桩。

多阶段射频工艺流程与计量学

PTFE在150–170°C预烘以去除可能导致Dk偏移2–4%的湿气。等离子体或钠蚀刻产生微粗糙度以增强附着力。混合层压使用低流动度半固化片(流动度<3%)防止树脂侵入射频核心。在线计量控制介质厚度至±5%(正负5%)以确保阻抗稳定性。参阅射频制造最佳实践。

表面处理权衡:化学浸银最小化插入损耗与无源互调;ENEPIG提供结合耐久性但镍层导致高频损耗适中。选择取决于射频性能与组装工艺的平衡。

损耗机制与无源互调抑制

在10 GHz时,铜的趋肤深度约0.66 µm(约0.66微米);与趋肤深度相当的粗糙度会增加有效电阻。低轮廓铜箔可降低导体损耗15–25%。我们的信号完整性协议筛查磁性污染物并实施洁净处理,以抑制PIM < −150 dBc(低于−150 dBc)。

全面射频测试与可靠性验证

每块面板的TDR将阻抗偏移定位至±2 mm(正负2毫米)。VNA扫描至40–67 GHz(40至67吉赫兹)提供插入损耗不确定度±0.1 dB(正负0.1分贝)的S参数。−40°C至+125°C(零下40至零上125摄氏度)热循环500–1000次限制过孔ΔR≤10%。85°C/85% RH(85摄氏度/100分之85相对湿度)湿度测试500小时验证稳定性。参阅IPC Class 3验收标准。

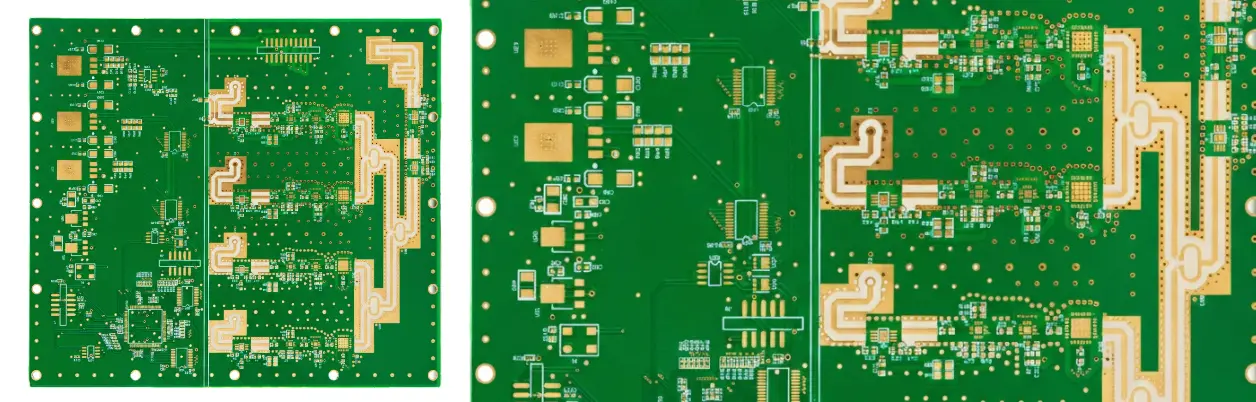

特定应用的射频实现

5G基础设施: sub-6 GHz及28/39 GHz波束成形,Dk漂移≤±0.02(小于或等于正负0.02)。参见5G PCB技术。

汽车雷达: 24/77 GHz,具备ISO/IATF可追溯性。

卫星通信/测试: 符合真空脱气要求的材料,插入损耗重复性±0.05 dB(正负0.05分贝)。

混合信号: 混合堆叠设计隔离射频与高速数字域以控制串扰。

工程保证与认证

经验: 经过生产验证的射频/毫米波构建,具备受控对准和验证堆叠。

专业知识: 场求解器+3D EM用于过孔/过渡;层压、钻孔和电镀的SPC;Cpk目标≥1.33(大于或等于1.33)。

权威性: IPC-6012 Class 3、MIL-PRF-31032、IATF 16949;可随时审计的文件。

可信度: 从批次代码到TDR/VNA结果的MES可追溯性;每次构建提供报告。

- 工艺控制:介质厚度、对准度、铜粗糙度

- 可追溯性:序列化、组件批次、数字流程单

- 验证:测试片TDR、VNA、显微切片、环境应力

常见问题

何时应从FR-4材料切换到射频级材料?

背钻与盲孔——如何选择?

哪种表面处理最适合射频应用?

混合叠层能节省多少成本?

如何验证阻抗和损耗?

体验先进的PCB制造卓越

从简单的原型到复杂的生产运行,我们的世界级工厂提供卓越的质量、快速的周转和有竞争力的价格。加入数千名信任我们PCB制造需求的满意客户。