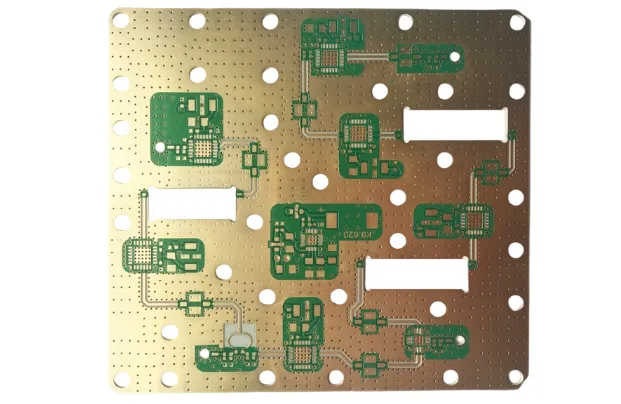

Rogers射频/微波PCB制造 | RO4350B、RO4003C、RT/duroid | 低损耗与混合叠层

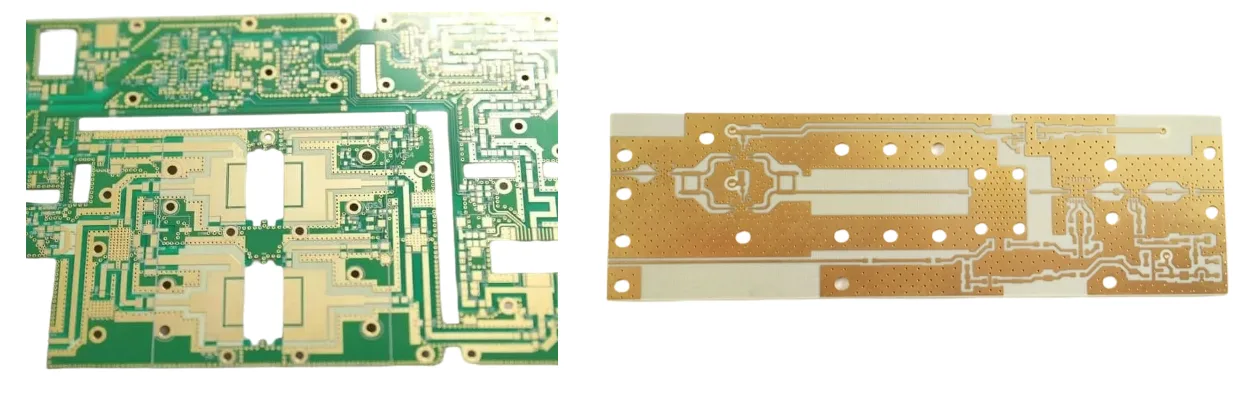

采用Rogers材料的高频PCB,具有低损耗(10 GHz时Df <0.004——小于0.004)、稳定的Dk、阻抗控制±5%(正负5%)、VNA S参数测试,以及Rogers + FR-4混合叠层以实现成本/性能平衡。

为何选择Rogers材料实现高频性能?

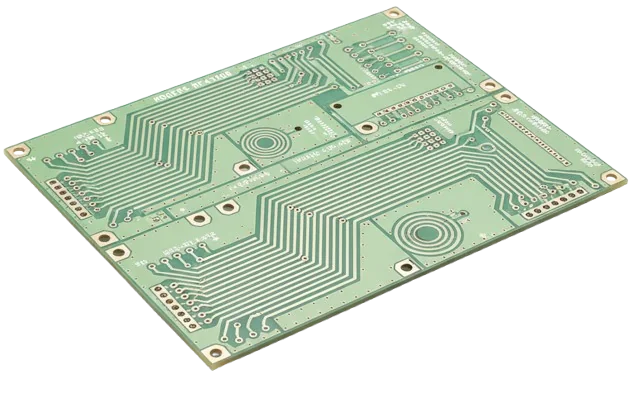

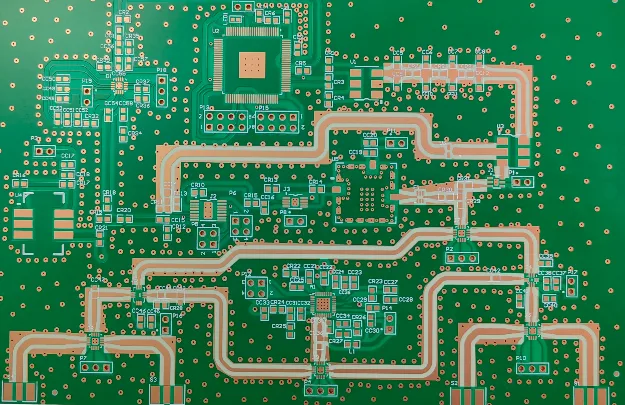

低损耗、稳定的Dk值、可预测的相位——专为RF/微波设计与标准FR-4 PCB相比,Rogers层压板提供超低介电损耗(Df在10 GHz时典型值为0.0009–0.004——0.0009至0.004)和稳定的介电常数(Dk变化在±2%以内——正负100分之2),在RF和微波频段保持插入/回波损耗及相位精度。针对5–40+ GHz(5至40吉赫兹及以上)频率,Rogers材料如RO4350B、RO4835和RT/duroid系列可维持可预测的线路几何形状与阻抗一致性,这对雷达和卫星通信系统至关重要。

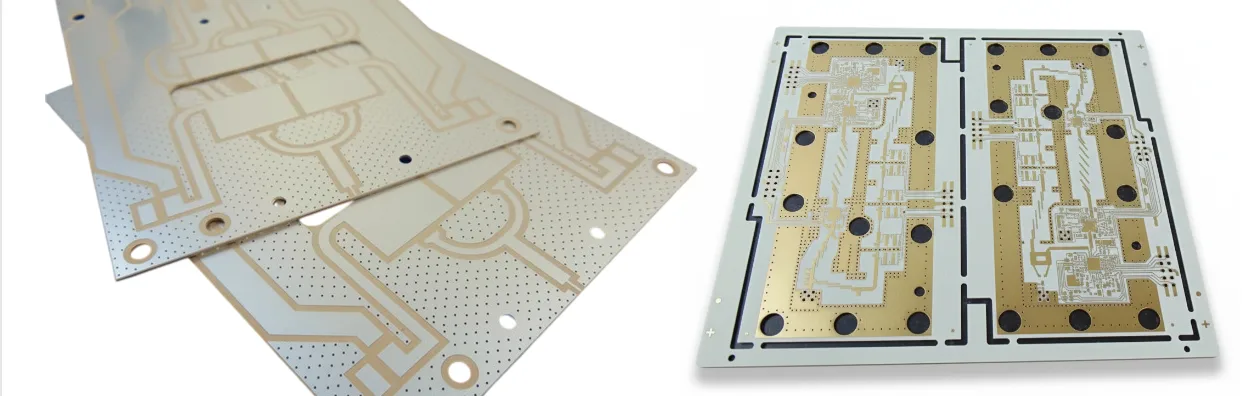

我们的工艺流程——PTFE复合材料的等离子体活化、低轮廓铜的表面粗糙度控制(Ra ≤1.5 μm——小于或等于1.5微米)以及精密层压压力曲线——支持混合堆叠设计,将Rogers材料置于RF能量传输层,同时内部平面使用多层FR-4芯板以降低30–50%(30至50百分比)材料成本。详见我们的Rogers PCB指南和堆叠设计说明获取详细层规划方法。

关键风险:PTFE粘附不良、粘结膜错位或层压温度梯度过度可能导致制造过程中出现空隙、层偏移或Dk漂移。这些效应会增加反射损耗和相位误差,尤其在10 GHz(10吉赫兹)以上频段。

我们的解决方案:我们实施层压工艺控制,通过等离子预清洗、差压层压和原位温度传感器确保粘结线均匀性。信号完整性设计仿真与基于TDR的阻抗验证将仿真数据与实测数据关联以进行生产调校。选择性使用PTFE的混合构建平衡了RF性能、成本与可制造性。

对于极端RF/毫米波系统——雷达、5G前端和航空航天通信——Rogers电路板与我们的高频PCB及陶瓷PCB产品线无缝配合,将热稳定性和电气稳定性扩展至24–110 GHz(24至110吉赫兹)范围。

- 支持RO4000®、RO3000®和RT/duroid®系列

- 在10 GHz时插入损耗目标低于约0.5 dB/英寸(取决于设计)

- 背钻至<10 mil(小于10密耳)以消除残桩

- 阻抗测试条与场求解器结果相关联

- 通过Rogers材料优化RF关键层的混合成本

🚀 快速报价请求

🔧 获取完整制造能力

专业射频/微波制造控制

PTFE处理、薄铜箔、分阶段层压PTFE和陶瓷填充层压板需要定制化控制:等离子蚀刻用于孔壁活化(附着力通常>1.0 N/mm——大于每毫米1.0牛顿)、分阶段压力/温度曲线(例如175–185°C(175至185摄氏度)),以及控深钻孔用于发射过渡。UV激光微孔(75–100 μm——75至100微米)和背钻可消除25+ Gbps(每秒25千兆比特及以上)通道的谐振残桩。

质量验证包括TDR阻抗测试(±5%——正负5%)和基于样本的VNA S参数(S11/S21),通常高达40 GHz(40吉赫兹)。显微切片确认≥20 μm(大于或等于20微米)孔壁铜厚;离子污染控制在≤1.56 μg/cm²(小于或等于1.56微克/平方厘米)。参见高频PCB测试和阻抗测试。

- 薄/超薄铜箔可降低导体损耗≈10–25%(约10至25百分比)

- 背钻和发射优化以减少反射

- 每块面板附带TDR验证样板(如指定)

- 射频原型的VNA S参数测试

- 符合IPC-6018工作流程的文档记录

Rogers PCB技术规格

适用于RF、微波及毫米波设计的能力

| 参数 | 标准能力 | 高级能力 | 标准 |

|---|---|---|---|

层数 | 1–28层(1至28层) | 最高50层(最高50层);混合叠层 | 微波与高频印制板性能规范(IPC-6018) |

基材类型 | RO4003C™、RO4350B™、RT/duroid® 5880 | RO3003™、RO3010™、Taconic、Isola;可与FR-4混合 | 高频基材规范(IPC-4103) |

介电常数(Dk) | ≈2.2–10.2 | 严格公差Dk材料 | 材料数据表 |

介质损耗角正切(Df) | <0.004 @ 10 GHz(10吉赫兹) | 超低损耗 <0.002 | 材料数据表 |

板厚 | 0.20–3.20毫米(0.20至3.20毫米) | 0.10–6.00毫米(0.10至6.00毫米),±5%(正负5%)公差 | 印制板可接受性标准(IPC-A-600) |

铜厚 | 0.5–2盎司(17–70 μm;每平方英尺0.5至2盎司;17至70微米) | 最高4盎司(最高4盎司);可选VLP铜 | 铜箔规范(IPC-4562) |

最小线宽/间距 | 75/75 μm(3/3 mil;75乘75微米) | 50/50 μm(2/2 mil;50乘50微米) | 印制板设计通用要求(IPC-2221) |

最小孔径 | 0.20毫米(8 mil) | 0.10毫米(4 mil)+ 背钻 | 刚性印制板详细设计标准(IPC-2222) |

阻抗控制 | ±10%(正负10%) | ±5%(正负5%)或更严格 | 传输线阻抗计算标准(IPC-2141) |

表面处理 | ENIG、化学沉银、OSP | ENEPIG、软金/硬金 | 表面镀层标准(IPC-4552/4553) |

质量检测 | 100%电测、TDR阻抗测试 | VNA S参数测试、离子污染检测 | 印制板电气测试标准(IPC-9252) |

认证项目 | ISO 9001、UL、IPC Class 2 | AS9100、MIL-PRF-31032、IPC Class 3 | 行业标准 |

交付周期 | 7–15天(7至15天) | 可提供加急服务 | 生产计划 |

准备开始您的PCB项目了吗?

无论您需要简单的原型还是复杂的生产运行,我们先进的制造能力确保卓越的质量和可靠性。30分钟内获取您的报价。

选择合适的Rogers材料

RO4350B™(介电常数约3.48;10 GHz时损耗因子约0.0037)在约30 GHz(30吉赫兹)范围内平衡成本与性能。

RT/duroid® 5880(介电常数约2.20;损耗因子约0.0009)可实现毫米波级的超低损耗。

RO3003™/RO3010™提供温度范围内稳定的介电常数。对于混合信号系统,采用混合堆叠——射频层使用Rogers,电源/数字层使用FR-4——通常可节省30–50%(30至50百分比)成本。详见微波损耗预算。

高级射频质量保证

除AOI/电测试外,基于样本的VNA可表征高达约40 GHz(40吉赫兹)的S参数(S11/S21);TDR验证特性阻抗在±5%(正负5%)范围内。显微切片确认过孔镀层厚度(≥20 μm)与对位精度(典型±50 μm)。离子污染目标≤1.56 μg/cm²。更多内容见高频PCB测试方法。

工程保证与认证

经验: 射频构建包含测试片-求解器关联与混合堆叠优化。

专长: PTFE加工、低轮廓铜箔、深度控制钻孔及背钻。

权威性: 工作流程符合IPC-6018;支持AS9100项目文档。

可信度: MES追溯系统关联材料批次与测试数据;报告可按需提供。

- 控制项:等离子活化、层压窗口、铜轮廓

- 追溯性:批次ID、流程单、测试片/VNA报告

- 验证项:TDR、VNA、显微切片、离子测试

常见问题

何时应选择Rogers而非FR-4材料?

混合Rogers+FR-4叠层结构有何优势?

是否提供S参数测量数据?

如何控制高频下的过孔残桩效应?

射频焊盘推荐使用哪种表面处理?

体验先进的PCB制造卓越

从简单的原型到复杂的生产运行,我们的世界级工厂提供卓越的质量、快速的周转和有竞争力的价格。加入数千名信任我们PCB制造需求的满意客户。