Bei der Highleap PCB Factory (HILPCB) integrieren wir thermische Schocktests als entscheidenden Schritt in unseren PCB-Herstellungs- und Montageprozess. Unsere Fähigkeiten umfassen Luft-zu-Luft- und Flüssigkeits-zu-Flüssigkeits-Tests, Temperaturzyklen und Materialverhaltensanalysen. Dieser Ansatz gewährleistet die Integrität der Lötstellen, die Zuverlässigkeit der Durchkontaktierungen und die Materialstabilität unter extremen thermischen Bedingungen, wie sie in der Luft- und Raumfahrt, Automobilindustrie und industriellen Anwendungen üblich sind.

Grundprinzipien der thermischen Schocktests und Methodenauswahl

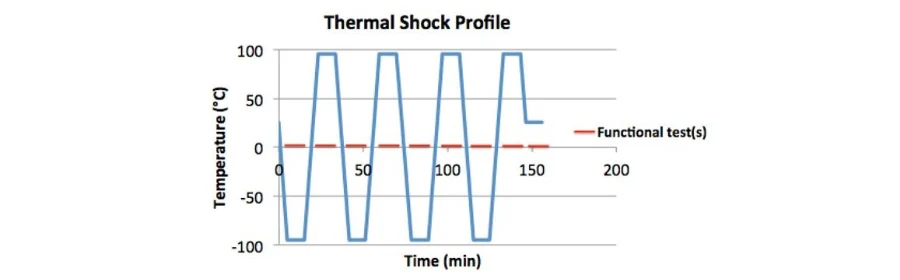

Thermische Schocktests simulieren plötzliche Temperaturwechsel, um mechanische Spannungsausfälle zu identifizieren, die durch unterschiedliche Wärmeausdehnungskoeffizienten (CTE) verschiedener Materialien verursacht werden. Bei HILPCB wählen wir aus mehreren Testtechnologien basierend auf Platinentyp, thermischem Profil und Zuverlässigkeitszielen für den Endgebrauch.

Schlüsseltechnologien:

- Luft-zu-Luft-Kammern: Kontrollierte thermische Belastung mit Übergangsraten über 30°C/min für realistische Simulation

- Flüssigkeits-zu-Flüssigkeits-Systeme: Extremer Schock durch Eintauchen mit Übergängen >100°C/min

- Zwei-Zonen-Automatisierung: Separate Heiß- und Kaltkammern mit robotergesteuerten Transfersystemen

- Programmierbare Profile: Anpassbare Zyklen von -80°C bis +225°C mit Haltezeiten für vollständigen Wärmeübergang

- Echtzeitüberwachung: Kontinuierliche Erfassung der elektrischen Kontinuität und Temperaturgradienten

- Fehlererkennungssysteme: Inline-Warnungen für Mikrorisse und Delamination

- Statistische Zuverlässigkeitstools: Datenerfassung für Weibull-Modellierung und Vorhersage von Feldausfällen

Unsere Umsetzungsstrategie betont die Auswahl optimaler Methoden, die auf Platinentechnologien wie hochthermische PCBs oder Keramik-PCBs zugeschnitten sind, um Teststrenge und Produktionseffizienz auszubalancieren.

Temperaturzyklusprotokolle und Umgebungsstresssimulation

Thermische Schocktests simulieren Betriebsextreme in kurzen Zeiträumen, um Alterungseffekte zu beschleunigen. Die Auswahl der Testprotokolle hängt von der Produktanwendung, den erforderlichen Lebenszyklusdaten und der Umgebungsexposition ab.

Luft-zu-Luft-Simulation: Wird für Produkte verwendet, die Umgebungsschwankungen ausgesetzt sind (z.B. Automobil- oder Outdoor-Elektronik). Übergangsgeschwindigkeiten bis zu 50°C/min unterstützen realistische Ermüdungsbelastungen. Kammern halten eine Genauigkeit von ±2°C, um wiederholbare Ergebnisse zu gewährleisten. Flüssig-zu-Flüssig-Übergang: Geeignet für Hochbelastungsvalidierungen wie Leistungselektronik und missionkritische Designs. Übergangsraten übersteigen 100°C/min, wodurch schnell thermische Spannung in gesamten Leiterplatten mit minimaler thermischer Verzögerung induziert wird. Essenziell für die Validierung von High-Density Interconnect (HDI) und Metallkernplatinen.

Thermische Profiloptimierung: Wir passen Sequenzen von -55°C bis +125°C für kommerzielle Leiterplatten und bis zu -65°C bis +200°C für Luftfahrtstandards an. Haltezeiten, Anstiegsraten und Zyklenanzahl werden gemäß Platinenmasse und -konfiguration angepasst.

Ausfallmechanismen und Materialverhaltensanalyse

Thermischer Schock kann mehrere unterschiedliche Ausfallmodi auslösen. Das Verständnis dieser ist entscheidend für sowohl Designrobustheit als auch vorhersagbare Zuverlässigkeit.

Häufige Ausfälle:

- Durchkontaktierungssrissbildung: Risse in der Fassungswand aufgrund von CTE-Mismatch

- Lötstellenermüdung: Rissbildung in Verbindungen durch zyklische thermische Ausdehnung

- Delamination: Schichttrennung an Harz-Prepreg- oder Kupfergrenzflächen

- Via-Bruch: Rissbildung an Ringbereichen oder Übergängen

- Anschlussbruch: Mechanischer Bruch in Gehäuseanschlüssen während schneller Abkühlung

- Pad-Ablösung: Leiterbahn-Delamination oder SMT-Pad-Ausfall durch Oberflächenspannung

- Bonddrahtschäden: Trennung in Mikroelektronik aufgrund von CTE-Mismatch

Material-CTEs bestimmen die Spannungsintensität. Beispielsweise kann Standard-FR4 sich um 50–70 ppm/°C in der Dicke ausdehnen, während Rogers-Leiterplatten verbesserte thermische Kompatibilität bieten und Spannungskonzentrationen reduzieren.

Implementierung von Thermischer Schockprüfung in Produktionsumgebungen

Integrierte QA und Überwachung

Thermische Schockprüfung ist in unseren Qualitätsarbeitsablauf eingebettet. Eingehende Bauteilvalidierung, prozessspezifische Tests und Endkontrolle gewährleisten Konformität. In-Prozess-Tests helfen, Probleme in Mehrschicht- und Flex-Leiterplatten-Baugruppen vor der Serienproduktion zu isolieren.

Kammertechnologie und Durchsatzoptimierung

Kammern werden basierend auf Leiterplattengröße, thermischer Masse und Durchsatz ausgewählt. Für Großserienfertigung reduzieren automatische Ladesysteme und programmierbare Logik manuelle Handhabung und erhöhen Genauigkeit und Effizienz.

Datenprotokollierung und Rückverfolgbarkeit

Alle Testergebnisse werden digital erfasst und mit Fertigungslos verknüpft. Dies gewährleistet Compliance mit Rückverfolgbarkeitsstandards in Branchen wie Luftfahrt und Medizinelektronik und unterstützt Feldausfallanalyse und Garantieabdeckung.

Erweiterte Ausfallanalyse und Zuverlässigkeitsmodellierung

Wir setzen nach dem Test mehrere Analysetechniken ein, um Ausfallursachen zu verstehen:

- Querschnittsanalyse: Zeigt interne Brüche oder Materialhohlräume

- Röntgenbildgebung: Erkennt verborgene Risse und Delamination

- Fraktopraphie: Identifiziert Rissentstehung und Ausbreitungspfade

- Thermische Modellierung: Korreliert physikalische Testdaten mit Designparametern

Zuverlässigkeitsvorhersagen werden mit statistischen Modellen erstellt:

- Weibull-Verteilung: Definiert die Ausfallwahrscheinlichkeit pro Zyklus

- Arrhenius-Modelle: Schätzen Ausfallraten unter beschleunigter Belastung

- Umweltkonditionierung: Kombiniert Vibration, Feuchtigkeit und Voralterung für Feldkorrelation

Platinen wie Flex-PCBs profitieren von solchen kombinierten Tests, um den Einsatz in rauen Umgebungen zu simulieren.

HILPCBs Strategie für thermische Zuverlässigkeit

Bei HILPCB integrieren wir thermische Zuverlässigkeit von der Designphase bis zur Endmontage.

- Designphase-Unterstützung: CTE-Mapping, Spannungssimulation und Materialauswahl

- Prozessabstimmung: Kontrollierte Reflow-Profile, optimierte Designs und robuste Löttechnik für SMT-Baugruppen

- Testinfrastruktur: Mehrere Thermokammern, Inline-Datenerfassung und Fehlerdiagnostik für Prototypen und Serienproduktion

Thermischer Schocktest – FAQ

Welcher Temperaturbereich wird beim thermischen Schocktest verwendet?

Typische Bereiche sind -55°C bis +125°C für kommerzielle Anwendungen und bis zu -65°C bis +200°C für Luftfahrt/Militär.

Wie unterscheidet sich thermischer Schock von thermischem Zyklieren?

Thermischer Schock hat schnelle Temperaturwechsel (>30°C/min), während thermisches Zyklieren langsamere Übergänge (<5°C/min) nutzt.

Wie viele Zyklen sind Standard?

Hängt von Zuverlässigkeitsstandards ab – 10–100 für Verbrauchergeräte, 500–1000+ für Industrie/Militär.

Kann thermische Schockdaten Feldzuverlässigkeit vorhersagen?

Ja, wenn mit Felddaten und statistischen Modellen wie Arrhenius oder Weibull verknüpft.

Welche Materialien bieten die beste Thermoschockbeständigkeit?

Hoch-Tg-Laminate, Keramiksubstrate und CTE-angepasste Verbundstoffe performen am besten.

Wie werden Testausfälle erkannt?

Durch elektrische Überwachung, Querschliffe und Bildgebung (Röntgen/Rasterelektronenmikroskopie) zur Lokalisierung und Klassifizierung von Fehlerstellen.