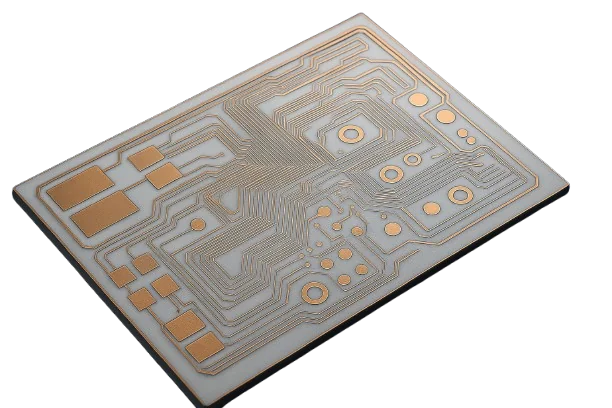

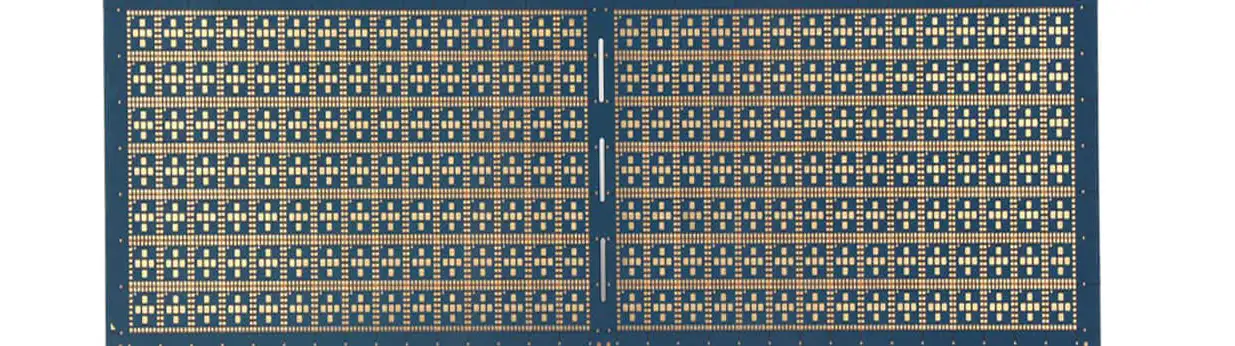

Circuit imprimé substrat IC (ABF/BT) | SAP à lignes fines, microvias empilés, pas de 0,25–0,40 mm (zéro virgule vingt-cinq à zéro virgule quarante)

Substrats IC organiques pour emballage avancé : Procédé semi-additif (SAP) 15–20 μm (quinze à vingt micromètres) ligne/espace, microvias empilés 25–50 μm (vingt-cinq à cinquante), construction ABF/BT, prêt pour flip-chip avec gauchissement contrôlé et impédance ±5% (plus ou moins cinq pourcent).

Fabrication de substrats IC et architecture des matériaux

Relier la densité d'E/S du silicium à la fiabilité au niveau systèmeLes substrats IC combinent la technologie d'emballage des semi-conducteurs et celle des PCB pour atteindre une densité de routage proche du silicium. Le procédé semi-additif (SAP) dépose du cuivre sur une couche de germination pour former des motifs fins, offrant des lignes/espacements de 15–20 μm (quinze à vingt micromètres) avec un sous-découpage minimal—généralement un gain de densité de 2–4× (deux à quatre fois) par rapport au HDI soustractif. Consultez notre aperçu des PCB HDI et nos notes sur la fabrication avancée de PCB HDI pour des concepts d'empilement connexes.

Les couches de film ABF (Ajinomoto Build-up Film) de 30–60 μm (trente à soixante micromètres) maintiennent un contrôle strict de l'épaisseur pour stabiliser l'impédance et l'inductance de boucle PDN. Les composites à base de résine BT présentent généralement un CTE X-Y de 12–14 ppm/°C (douze à quatorze parties par million par degré Celsius), reliant le silicium ~2.6 ppm/°C (deux virgule six) et le FR-4 ~16–18 ppm/°C (seize à dix-huit). Pour les configurations mixtes RF/numériques, les choix de matériaux s'alignent sur notre guide des PCB haute fréquence et notre introduction aux matériaux.

Risque critique : Un mauvais alignement entre les couches ABF, une mauvaise adhérence du cuivre ou un gauchissement non contrôlé pendant la stratification peut entraîner des circuits ouverts, des fissures de via ou une dérive d'impédance > ±10 % (plus ou moins dix pour cent). Un remplissage inadéquat des via-in-pad et une planarité de surface insuffisante compromettent également la fiabilité du wire-bonding dans les assemblages SiP et flip-chip.

Notre solution : Nous appliquons des méthodes de simulation d'intégrité du signal et de corrélation des PCB backplane pour valider le comportement des interconnexions haute densité. Les lignes SAP et mSAP fonctionnent dans des salles blanches de classe 1000 avec un contrôle de couverture par étapes inférieur à ±2 μm (plus ou moins deux micromètres). Chaque lot de substrats subit une cartographie CTE, un profilage de gauchissement et une vérification TMA selon les exigences IPC-6012 Classe 3 AABUS. Lorsque les frontaux RF exigent des performances ultra-faible perte, les systèmes hybrides ABF et PTFE sont co-traités pour minimiser la discontinuité diélectrique.

Pour plus d'informations sur les compromis matériels et la modélisation de la fiabilité, consultez la validation des contraintes thermiques et les options de PCB en substrat céramique qui étendent la technologie des substrats IC aux applications RF haute puissance et aux capteurs.

- Routage à fines lignes via SAP avec un sous-découpage réduit par rapport à la gravure soustractive

- Empilement ABF avec contrôle diélectrique de 30–60 μm (trente à soixante)

- Optimisation du CTE composite (cible du substrat 9–14 ppm/°C — neuf à quatorze)

- Contrôle du gauchissement ≤0,5 % (inférieur ou égal à zéro virgule cinq pour cent) de la diagonale (objectif de processus)

- Stabilité d'impédance avec une tolérance de ±5 % (plus ou moins cinq pour cent)

🚀 Demande de Devis Rapide

📋 Obtenir Capacités Complètes

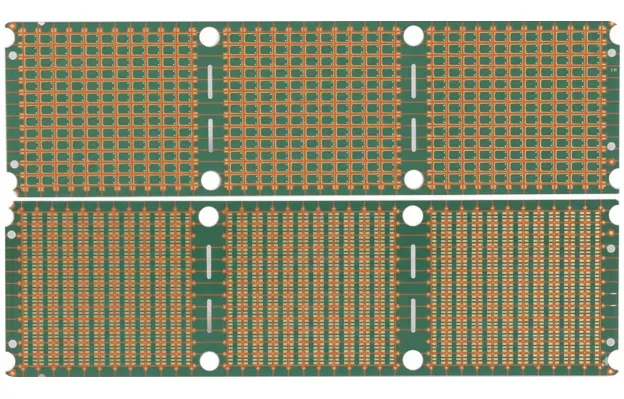

Flux SAP contrôlé et portes de qualité axées sur le rendement

Photolithographie, placage et métrologie optimisés pour un pas finLes fenêtres de processus sont nettement plus strictes que celles des circuits imprimés standard. L'uniformité de dépôt de la couche de semence dans une plage de ±10 % (plus ou moins dix pour cent) précède le motif photo pour des caractéristiques de 15–20 μm. Le placage par impulsions inversées gère la croissance des bords et le pouvoir de projection ; la gravure différentielle supprime la semence entre les traces avec un contrôle de largeur de ±10 % (plus ou moins dix pour cent). Les microvias d'un diamètre de 25–50 μm (vingt-cinq à cinquante micromètres) atteignent un contrôle de profondeur de ±5 μm (plus ou moins cinq). Voir l'excellence manufacturière et les contrôles de processus HDI.

L'AOI avec une résolution ≤5 μm (inférieure ou égale à cinq micromètres), les cibles d'enregistrement par rayons X et l'IST (test de stress d'interconnexion) sur 200–500 (deux cents à cinq cents) cycles protègent la fiabilité. Pour l'intégration au niveau de la carte (panneaux arrière/cartes de ligne), voir les circuits imprimés pour panneaux arrière et les capacités des circuits imprimés haute vitesse.

- Épaisseur et uniformité de la couche de semence SPC

- Placage de cuivre par impulsions inversées pour des caractéristiques uniformes

- Formation de microvias laser et vérification du remplissage de cuivre

- Contrôle qualité multi-portes AOI/rayons X/IST

Spécifications techniques du substrat IC

Lignes fines, microvias empilés et constructions compatibles avec le flip-chip

| Paramètre | Capacité standard | Capacité avancée | Norme |

|---|---|---|---|

Layer Count | 4–16 couches (quatre à seize) | Jusqu'à 50 couches (jusqu'à cinquante) | JEDEC |

Base Materials | Résine BT, FR-4 haute Tg | ABF, Polyimide, Substrat en verre | IPC-4101/4103 |

Board Thickness | 0.20–0.80 mm (zéro virgule deux zéro à zéro virgule huit zéro) | Jusqu'à 0.10 mm (jusqu'à zéro virgule un zéro) | IPC-A-600 |

Copper Weight | 12–18 μm (douze à dix-huit micromètres) | 5–35 μm (cinq à trente-cinq ; constructions SAP) | IPC-4562 |

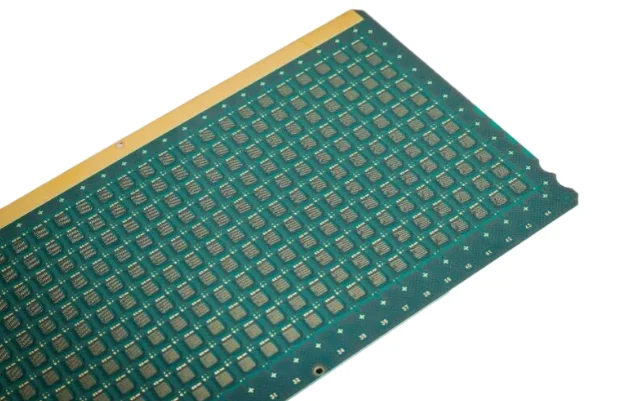

Min Trace/Space | 25/25 μm (un/un mil ; vingt-cinq par vingt-cinq) | 15/15 μm (0.6/0.6 mil ; quinze par quinze) | IPC-2226 |

Min Hole Size (Laser) | 50 μm (deux mils) | 25 μm (un mil) | IPC-2226 |

Via Technology | Microvias, vias enterrés | Microvias empilés, via-in-pad, HDI toute couche | IPC-6012 |

BGA Pitch | 0.40 mm (zéro virgule quatre zéro) | 0.25 mm (zéro virgule deux cinq) | JEDEC |

Impedance Control | ±10% (plus/minus dix pour cent) | ±5% (plus/minus cinq pour cent) avec TDR | IPC-2141 |

Surface Finish | ENIG, OSP | ENEPIG, Ni/Au sans électrolyse, Or doux/dur | IPC-4552/4556 |

Quality Testing | AOI, Test électrique | SEM, Coupe transversale, TDR/IST | IPC-9252 |

Certifications | ISO 9001, UL | IATF 16949, Méthodes JEDEC | Industry standards |

Lead Time | 15–25 jours (quinze à vingt-cinq) | Consulter pour accélération | Production schedule |

Prêt à démarrer votre projet PCB ?

Que vous ayez besoin de prototypes simples ou de productions complexes, nos capacités de fabrication avancées garantissent une qualité supérieure et une fiabilité. Obtenez votre devis en seulement 30 minutes.

Intégrité du signal et co-conception PDN

À 28–112 Gbps (vingt-huit à cent douze) SerDes, les discontinuités aux transitions balle-substrat dominent les pertes et réflexions. Le réglage des antipads et les barrières de vias de masse dans un rayon de 0.5–1.0 mm (zéro virgule cinq à un virgule zéro millimètre) maintiennent les chemins de retour. La sélection du Df du matériau (typiquement ABF 0.010–0.015 à 10 GHz) et la rugosité du cuivre (Ra ≤1.5 μm) soutiennent les objectifs de perte d'insertion—voir contrôle d'impédance et test TDR.

Les objectifs PDN en dessous de 1–10 mΩ (un à dix milliohms) jusqu'à 100 MHz (cent mégahertz) reposent sur des diélectriques fins 30–60 μm (trente à soixante) et des fermes de vias denses sous la puce (typiquement 100–200 vias/cm²). Pour les canaux au niveau de la carte et les connecteurs, alignez-vous avec nos capacités PCB haute vitesse et PCB backplane.

Précision d'enregistrement et discipline de processus en salle blanche

Le SAP commence par une micro-rugosité (Ra ~0.5–1.0 μm), une couche de cuivre de départ 0.5–1.0 μm (zéro virgule cinq à un virgule zéro) et une épaisseur de résine 15–25 μm pour des motifs de 15–20 μm. Le placage par impulsions inversées construit le cuivre de signal 10–15 μm (dix à quinze) et les plans 20–30 μm (vingt à trente). Après le décapage de la résine, la gravure différentielle élimine la couche de départ sans sous-découpe. Les salles blanches (Classe 1,000–10,000 — mille à dix mille) minimisent les courts-circuits/ouvertures dans les pas fins ; voir flux de fabrication.

Les objectifs d'enregistrement couche à couche de ±25 μm (plus/moins vingt-cinq micromètres) utilisent un alignement optique et des repères aux rayons X. La construction séquentielle utilise des systèmes à faible écoulement (écoulement de résine <5% — moins de cinq pour cent) pour maintenir l'épaisseur du diélectrique à ±5% (plus/moins cinq pour cent). Le SPC maintient un Cpk ≥1.33 (supérieur ou égal à un virgule trois trois) pour les caractéristiques critiques.

ABF vs. BT vs. Verre et options émergentes

ABF: photosensible, microvia par lithographie jusqu'à 15–25 μm (quinze à vingt-cinq), Dk ~3.2–3.4, Df ~0.010–0.015 à 10 GHz.

BT: économique pour le wire-bond/flip-chip modéré avec CTE X-Y 12–14 ppm/°C.

Substrat en verre: CTE ~3 ppm/°C et rugosité ultra-faible Ra <0.1 μm (moins de zéro virgule un), permettant des structures TGV/pont. Pour les modules RF frontaux, considérez également les interposeurs PCB céramique.

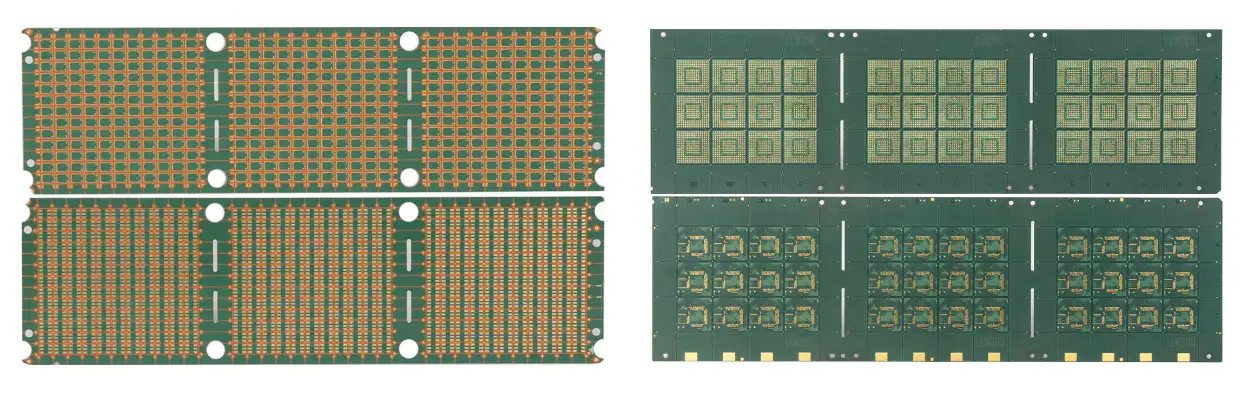

Flip-Chip, Underfill et assemblage PoP

Le flip-chip nécessite un contrôle de coplanarité ; une déformation dépassant 50–75 μm (cinquante à soixante-quinze micromètres) risque des joints non mouillés. L'underfill avec un CTE 25–35 ppm/°C redistribue les contraintes. Pour le PoP et le SiP, coordonnez le pas/déformation et les profils de refusion. Explorez les notes d'emballage dans substrat flip-chip et la validation du système dans assemblage box build.

Assurance Ingénierie & Certifications

Expérience : constructions SAP en volume avec routage de 15–20 μm et pas de 0.25–0.40 mm.

Expertise : uniformité de la graine, placage par impulsion inverse, remplissage de microvia empilé et enregistrement par rayons X ; SPC maintient Cpk ≥1.33 (supérieur ou égal à un point trois trois).

Autorité : fiabilité alignée sur JEDEC, documentation IPC-6012 Classe 3.

Fiabilité : traçabilité MES reliant les lots fournisseurs, sérialisation et rapports AOI/X-ray/IST/TDR.

- Contrôles : cartographie d'épaisseur, facteur de gravure, enregistrement, rugosité du cuivre

- Traçabilité : codes de lot, sérialisation des unités, voyageur numérique

- Validation : IST 200–500 cycles, coupes transversales, SIR, TDR

Questions fréquentes

ABF vs. BT: which dielectric should I choose?

What fine-line and via sizes do you support?

How do you manage warpage for flip-chip?

Can the substrate handle 112 Gbps channels?

Which surface finish is recommended?

Découvrez l'Excellence de Fabrication

Des processus de fabrication avancés garantissent que chaque PCB répond aux normes de qualité les plus élevées. Obtenez instantanément votre devis personnalisé.