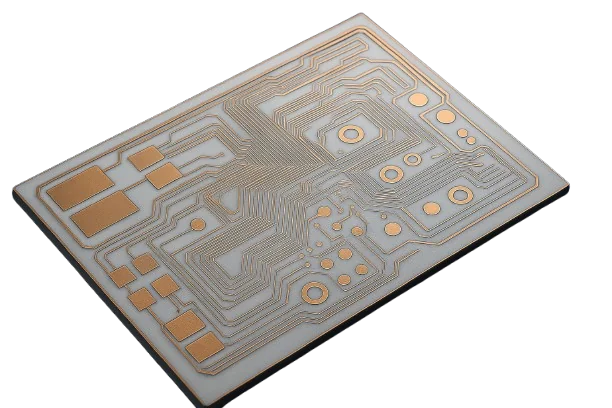

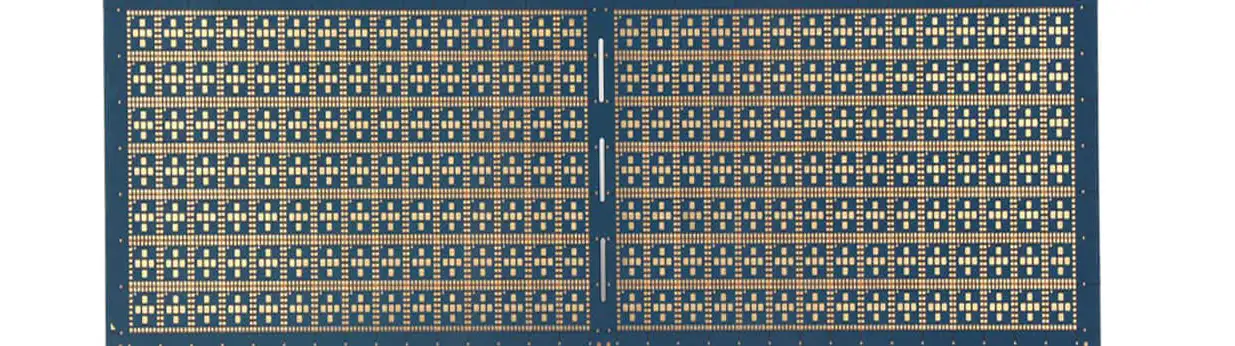

IC-Substrat-Leiterplatte (ABF/BT) | Feine SAP-Leitungen, gestapelte Mikrovias, 0,25–0,40 mm (null Komma zwei fünf bis null Komma vier null) Rastermaß

Organische IC-Substrate für fortschrittliche Verpackung: Semi-Additives Verfahren (SAP) 15–20 μm (fünfzehn bis zwanzig Mikrometer) Leiterbahn/Abstand, gestapelte Mikrovias 25–50 μm (fünfundzwanzig bis fünfzig), ABF/BT-Aufbau, Flip-Chip-fähig mit kontrollierter Verformung und Impedanz ±5 % (plus/minus fünf Prozent).

IC-Substrat-Herstellung & Materialarchitektur

Überbrückung der Silizium-I/O-Dichte mit systemweiter ZuverlässigkeitIC-Substrate vereinen Halbleiterverpackung und Leiterplattentechnologie, um eine nahezu siliziumähnliche Leitungsdichte zu erreichen. Der Semi-Additive-Prozess (SAP) lagert Kupfer auf einer Saatschicht ab, um feine Strukturen zu bilden, und ermöglicht 15–20 μm (fünfzehn bis zwanzig Mikrometer) Leiterbahn/Abstand mit minimalem Unterätzen – typischerweise ein 2–4× (zwei- bis viermal) höhere Dichte im Vergleich zu subtraktivem HDI. Siehe unsere HDI-PCB-Übersicht und fortgeschrittene HDI-Herstellung für verwandte Aufbaukonzepte.

ABF (Ajinomoto Build-up Film)-Schichten von 30–60 μm (dreißig bis sechzig Mikrometer) gewährleisten eine präzise Dickekontrolle zur Stabilisierung der Impedanz und PDN-Schleifeninduktivität.

BT-Harzkomposite zeigen typischerweise einen X-Y-CTE von 12–14 ppm/°C (zwölf bis vierzehn Teile pro Million pro Grad Celsius), was zwischen Silizium ~2,6 ppm/°C (zwei Komma sechs) und FR-4 ~16–18 ppm/°C (sechzehn bis achtzehn) liegt. Für gemischte RF/digitale Layouts orientieren sich Materialauswahl an unserer Hochfrequenz-PCB-Anleitung und Materialgrundlagen.

Kritisches Risiko: Fehlausrichtung zwischen ABF-Schichten, schlechte Kupferhaftung oder unkontrollierte Verformung während der Laminierung können zu offenen Stromkreisen, Via-Rissen oder Impedanzabweichungen > ±10 % (plus/minus zehn Prozent) führen. Unzureichende Via-in-Pad-Füllung und Oberflächenplanarität beeinträchtigen auch die Drahtbond-Zuverlässigkeit in SiP- und Flip-Chip-Montagen.

Unsere Lösung: Wir wenden Signalintegritätssimulation und Backplane-PCB-Korrelationsmethoden an, um das Verhalten hochdichter Verbindungen zu validieren. SAP- und mSAP-Leitungen arbeiten in Reinräumen der Klasse 1000 mit einer Schrittabdeckungskontrolle unter ±2 μm (plus/minus zwei Mikrometer). Jedes Substrat-Lot unterzieht sich CTE-Mapping, Verformungsprofilierung und TMA-Verifizierung gemäß IPC-6012 Klasse 3 AABUS-Anforderungen. Bei RF-Frontends mit ultra-niedrigem Verlust werden hybride ABF- und PTFE-Systeme gemeinsam verarbeitet, um dielektrische Diskontinuität zu minimieren.

Für weitere Einblicke in Materialkompromisse und Zuverlässigkeitsmodellierung siehe thermische Stressvalidierung und Keramiksubstrat-PCB-Optionen, die IC-Substrattechnologie in Hochleistungs-RF- und Sensoranwendungen erweitern.

- Feinleitungsführung via SAP mit reduziertem Unterätzen im Vergleich zu subtraktivem Ätzen

- ABF-Aufbau 30–60 μm (dreißig bis sechzig) Dielektrikumkontrolle

- Komposit-CTE-Optimierung (Substrat-Ziel 9–14 ppm/°C — neun bis vierzehn)

- Verformungskontrolle ≤0,5 % (kleiner oder gleich null Komma fünf Prozent) der Diagonale (Prozessziel)

- Impedanzstabilität mit ±5 % (plus/minus fünf Prozent) Toleranz

🚀 Schnelle Angebotsanfrage

📋 Vollständige Fähigkeiten erhalten

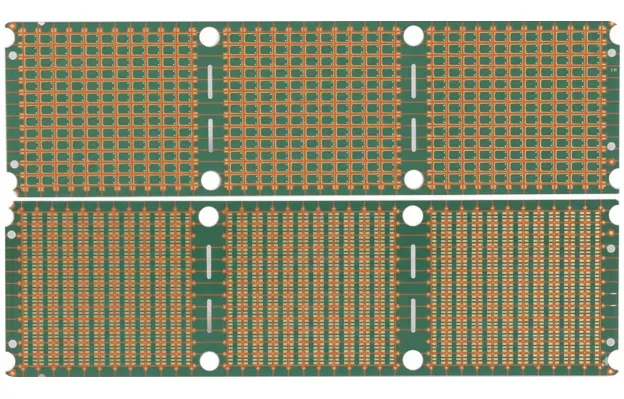

Kontrollierter SAP-Fluss & ertragsgesteuerte Qualitätsprüfpunkte

Photolithografie, Galvanik und Messtechnik für feine Strukturen optimiertProzessfenster sind deutlich enger als bei Standard-PCBs. Die Gleichmäßigkeit der Saatbeschichtung innerhalb von ±10% (plus/minus zehn Prozent) geht dem Fotolackieren für 15–20 μm Strukturen voraus. Pulsierende Umkehrgalvanik steuert Kantenwachstum und Streufähigkeit; differenzielles Ätzen entfernt die Saat zwischen den Leitungen mit einer Breitenkontrolle von ±10% (plus/minus zehn Prozent). Mikrovias mit 25–50 μm (fünfundzwanzig bis fünfzig Mikrometer) Durchmesser erreichen eine Tiefenkontrolle von ±5 μm (plus/minus fünf). Siehe Herstellungsexzellenz und HDI-Prozesskontrollen.

AOI mit ≤5 μm (kleiner oder gleich fünf Mikrometer) Auflösung, Röntgenregistrierungsziele und IST (Interconnect Stress Test) über 200–500 (zweihundert bis fünfhundert) Zyklen sichern die Zuverlässigkeit. Für Board-Level-Integration (Backplanes/Line Cards) siehe Backplane-PCB und Hochgeschwindigkeits-PCB Fähigkeiten.

- SPC für Saatschichtdicke und Gleichmäßigkeit

- Pulsierende Umkehrkupfergalvanik für gleichmäßige Strukturen

- Laser-Mikrovia-Bildung und Kupferfüllungsprüfung

- AOI/Röntgen/IST Mehrstufen-Qualitätskontrolle

Technische Spezifikationen für IC-Substrate

Feinleiter, gestapelte Mikrovias und Flip-Chip-kompatible Aufbauten

| Parameter | Standardfähigkeit | Erweiterte Fähigkeit | Standard |

|---|---|---|---|

Layer Count | 4–16 Schichten (vier bis sechzehn) | Bis zu 50 Schichten (bis zu fünfzig) | JEDEC |

Base Materials | BT-Harz, High-Tg FR-4 | ABF, Polyimid, Glassubstrat | IPC-4101/4103 |

Board Thickness | 0,20–0,80 mm (null Komma zwei null bis null Komma acht null) | Bis zu 0,10 mm (bis zu null Komma eins null) | IPC-A-600 |

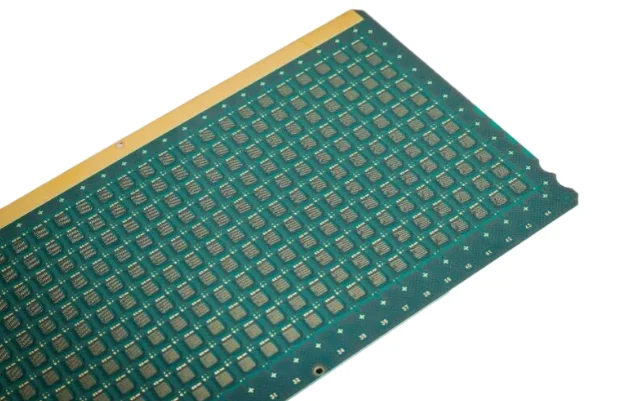

Copper Weight | 12–18 μm (zwölf bis achtzehn Mikrometer) | 5–35 μm (fünf bis fünfunddreißig; SAP-Aufbauten) | IPC-4562 |

Min Trace/Space | 25/25 μm (eins/eins mil; fünfundzwanzig mal fünfundzwanzig) | 15/15 μm (0,6/0,6 mil; fünfzehn mal fünfzehn) | IPC-2226 |

Min Hole Size (Laser) | 50 μm (zwei mils) | 25 μm (ein mil) | IPC-2226 |

Via Technology | Mikrovias, vergrabene Vias | Gestapelte Mikrovias, Via-in-Pad, Any-Layer-HDI | IPC-6012 |

BGA Pitch | 0,40 mm (null Komma vier null) | 0,25 mm (null Komma zwei fünf) | JEDEC |

Impedance Control | ±10 % (plus/minus zehn Prozent) | ±5 % (plus/minus fünf Prozent) mit TDR | IPC-2141 |

Surface Finish | ENIG, OSP | ENEPIG, Chemisch Nickel/Gold, Weich/Hartgold | IPC-4552/4556 |

Quality Testing | AOI, E-Test | SEM, Querschnitt, TDR/IST | IPC-9252 |

Certifications | ISO 9001, UL | IATF 16949, JEDEC-Methoden | Industriestandards |

Lead Time | 15–25 Tage (fünfzehn bis fünfundzwanzig) | Anfrage für Expresslieferung | Produktionsplan |

Bereit, Ihr PCB-Projekt zu starten?

Ob Sie einfache Prototypen oder komplexe Produktionsläufe benötigen, unsere fortschrittlichen Fertigungskapazitäten gewährleisten überlegene Qualität und Zuverlässigkeit. Erhalten Sie Ihr Angebot in nur 30 Minuten.

Signalintegrität & PDN-Co-Design

Bei 28–112 Gbps (achtundzwanzig bis einhundertzwölf) SerDes dominieren Diskontinuitäten an Ball-zu-Substrat-Übergängen die Verluste und Reflexionen. Antipad-Abstimmung und Erdungs-Via-Zäune innerhalb von 0,5–1,0 mm (null Komma fünf bis eins Komma null Millimeter) erhalten Rückpfade aufrecht. Die Auswahl des Material-Df (typisch ABF 0,010–0,015 bei 10 GHz) und die Kupferrauheit (Ra ≤1,5 μm) unterstützen die Einfügungsverlustziele – siehe Impedanzkontrolle und TDR-Tests.

PDN-Ziele unter 1–10 mΩ (eins bis zehn Milliohm) bei bis zu 100 MHz (einhundert Megahertz) basieren auf dünnen Dielektrika 30–60 μm (dreißig bis sechzig) und dichten Via-Feldern unter dem Die (typisch 100–200 vias/cm²). Für Board-Level-Kanäle und Steckverbinder stimmen Sie mit unseren Hochgeschwindigkeits-PCB- und Backplane-PCB-Fähigkeiten ab.

Registrierungsgenauigkeit & Reinraumprozessdisziplin

SAP beginnt mit Mikrorauheit (Ra ~0,5–1,0 μm), Saatkupfer 0,5–1,0 μm (null Komma fünf bis eins Komma null) und Resistdicke 15–25 μm für 15–20 μm Muster. Puls-umgekehrte Plattierung baut Signalkupfer 10–15 μm (zehn bis fünfzehn) und Ebenen 20–30 μm (zwanzig bis dreißig) auf. Nach dem Resistabzug beseitigt differenzielles Ätzen das Saatkupfer ohne Unterätzung. Reinräume (Klasse 1.000–10.000 — eintausend bis zehntausend) minimieren Kurzschlüsse/Unterbrechungen im Feinstpitzen; siehe Fertigungsablauf.

Schicht-zu-Schicht-Registrierungsziele ±25 μm (plus/minus fünfundzwanzig Mikrometer) unter Verwendung optischer Ausrichtung und Röntgenreferenzen. Sequentieller Aufbau verwendet Niedrigflusssysteme (Harzfluss <5% — weniger als fünf Prozent), um die Dielektrikumsdicke ±5% (plus/minus fünf Prozent) zu halten. SPC hält Cpk ≥1,33 (größer oder gleich eins Komma drei drei) für kritische Merkmale aufrecht.

ABF vs. BT vs. Glas & aufkommende Optionen

ABF: fotobildbar, Mikrovia durch Lithographie bis 15–25 μm (fünfzehn bis fünfundzwanzig), Dk ~3,2–3,4, Df ~0,010–0,015 bei 10 GHz.

BT: kostengünstig für Drahtbond/moderates Flip-Chip mit X-Y CTE 12–14 ppm/°C.

Glassubstrat: CTE ~3 ppm/°C und ultra-glatt Ra <0,1 μm (weniger als null Komma eins), ermöglicht TGV/Brückenstrukturen. Für RF-Frontend-Module ziehen Sie auch Keramik-PCB-Interposer in Betracht.

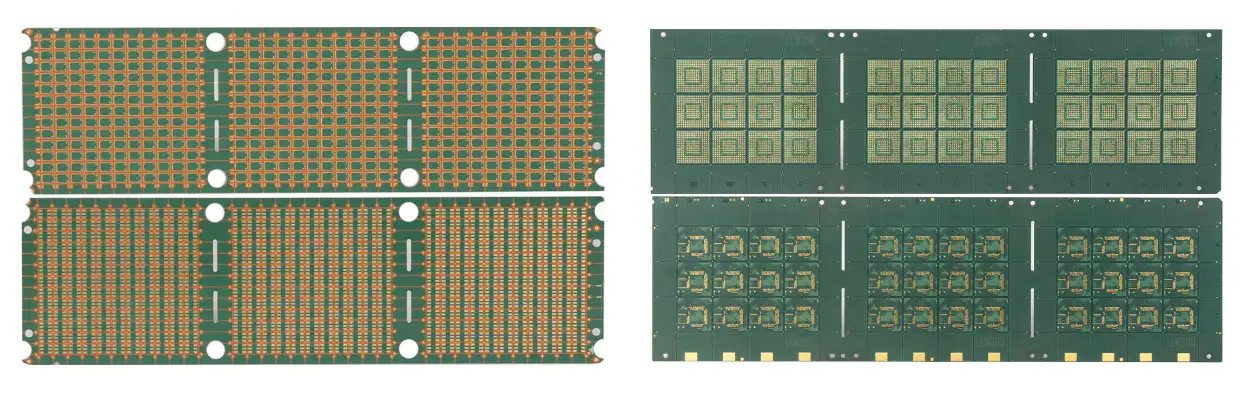

Flip-Chip, Underfill & PoP-Montage

Flip-Chip erfordert Ebenheitskontrolle; Verzug über 50–75 μm (fünfzig bis fünfundsiebzig Mikrometer) riskiert nichtbenetzte Verbindungen. Underfill mit CTE 25–35 ppm/°C verteilt Spannung um. Für PoP und SiP koordinieren Sie Steigung/Verzug und Reflow-Profile. Erkunden Sie Verpackungshinweise in Flip-Chip-Substrat und Systemvalidierung in Box Build.

Ingenieurtechnische Absicherung & Zertifizierungen

Erfahrung: Volumen-SAP-Aufbauten mit 15–20 μm Leitbahnbreite und 0,25–0,40 mm Rastermaß.

Expertise: Saatgutgleichmäßigkeit, Puls-Umkehr-Galvanisierung, gestapelte Microvia-Füllung und Röntgenregistrierung; SPC hält Cpk ≥1,33 (größer oder gleich eins Komma drei drei).

Autorität: JEDEC-konforme Zuverlässigkeit, IPC-6012 Klasse 3 Dokumentation.

Vertrauenswürdigkeit: MES-Rückverfolgbarkeit mit Verknüpfung von Lieferantenchargen, Serialisierung und AOI/Röntgen/IST/TDR-Berichten.

- Kontrollen: Dickeverteilung, Ätzfaktor, Registrierung, Kupferrauheit

- Rückverfolgbarkeit: Chargencodes, Einheitenserialisierung, digitaler Begleitschein

- Validierung: IST 200–500 Zyklen, Querschnitte, SIR, TDR

Häufig gestellte Fragen

ABF vs. BT: which dielectric should I choose?

What fine-line and via sizes do you support?

How do you manage warpage for flip-chip?

Can the substrate handle 112 Gbps channels?

Which surface finish is recommended?

Erleben Sie Fertigungsexzellenz

Fortschrittliche Fertigungsprozesse gewährleisten, dass jede PCB den höchsten Qualitätsstandards entspricht. Erhalten Sie sofort Ihr individuelles Angebot.